Устройство для диагностики ресурса деталей механизмов и машин

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОЛ ИСАИИЕ

ИЗОБРЕТЕНИЯ (iii 729482 (6! ) Дополнительное к авт. свил-ву— (22) Заявлено 12.06.76 (2! ) 2383699/25-28 (5 ll ) M. Кл.

G 01 N 3/06 с присоединением заявки M— (23) Приоритет—

Гесударстеенный комитет до девам нзобретений н открытий (53) УДK 620.178. .311.82 (088.8) Опубликовано 25.04.80 Бюллетень _#_ 1S

Дата опубликования описания 25.04.80 (72) А вторы изобретения

- В. В. Волков, И. И. Дулевичюс, К. M. Рагульскис и А. — P. Я. Янкунас

Каунасский политехнический институт им. Антанаса Снечкуса (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ ДИАГНОСТИКИ РЕСУРСА

ДЕТАЛЕЙ МЕХАНИЗМОВ И МАШИН

Изобретение относится к испытаниям конструкций на выносливость.

Известно устройство для диагностики ресурса деталей механизмов и машин, содержащее преобразователь, блок сбора информации, регистрации и управляющие механизмы (!l..

Известно также устройство для диагностики ресурса деталей механизмов и маивтн, содержащее последовательно соединенные преобразователь, блок сбора информации, блок обработки информации и регистрирующее устройство (2).

Однако известные устройства не позволяют количествеьно оценить остаточный ресурс де15 талей механизмов и мавлн, характер случай- ных стационарных процессов.

Целью изобретения является получение качественной оценки остаточного ресурса деталей, работаницих в условиях случайного дчнамичесi0 кого нагружения.

Это достигается тем, что блок сбора информации выполнен в. виде долговременного запоминающего устройства и двухканальной систе2 мы, одтн из каналов которои образован последовательно соединенными ограничителем уровня нагрузки, счетчиком интервалов времени и промежуточным запоминающим устройством, другой канал образован кольцевым запоминающим устройством, входы каналов соединены с преобразователем,. выходы — с входами долговременного запоминающего устройства, выход . которого соединен с входом блока обработки информации, а блок обработки информации выполнен в виде промежуточного запоминающего устройства, блока задержки, вычислительного устройства, и последовательно соединенных оперативного запоминающего устройства, ачализатора спектра, дискриминатора спектральных составляющих блока определения выносливости, выхоцы дискриминатора спектральных составляющих и блока определения выносливости соединены с входами промежуточного запоминающего устройства, вход анализатора спектра— с входом блока задержки, выходы промежуточного запоминающего устройства блока задержки и оперативного запоминающего устройства с входами вычислительного устройства. ство содержит также регулирующее устройство

23, вход которого соединен с выходом промежуточного запоминающего устройства 22.

Устройство работает следующим образом.

Динамические нагрузки в виде случайных динамических процессов О (t) воспринимаются преобразователем 1 и, усиленные в усилителе 2, записываются в кольцевом запоминающем уст- ройстве 6. Одновременно непрерывным потоком реализация 5(t) поступает в ограничитель 4 уровня нагрузки, который управляет счетчиком 5 интервалов времени TJ; т.е. фиксируются все интервалы времени, в течение кото-рых 5(t) + Π— 1, где 5 — 1, — предел выносли. вости материала испытуемой детали, соответствующий уровню ограничения. Определенные интервалы времени записываются промежуточным запоминающим устройством 5 для TJ, 1К.

В случае смены режима нагружения информация через схемы. совпадения 7 и 8 переписывается в долговременное запоминающее устройство 10, где она хранится постоянно, а новая информация поступает в кольцевое запоминающее устройство 6 и промежуточное запоминающее устройство 5.

По сигналу от переключателя 12 подачи информации включается схема совпадения 9 и происходит считывание информации из долговременного запоминающего устройстга 10 в оперативное запоминающее устройство 13, после чего проводится анализ остаточного ресурса, Для этого в анализаторе спектра 14 определяется амплитудный спектр реализации и в дискригинаторе 15 производится дискриьа-нация этих составляющих спектра, амплитуда. которых нревыщает уровень ограничения с соответствующими значениями частоты О. Затем в блоке

16 определения выносливости с помощью выделенных составляющих спектра и кривых усталости для материала испытуемой детали определяются значения 1/Ni, где Ni — выносливость материала. Последние одновременно с соответствующими частотами fi, i = 1, и записываются в промежуточное запоминающее устройство 17.

После конца анализа спектра через блок задержки поступает сигнал "конец анализа", и открываются схемы совпадения 19 и 20, а сформированные массивы TJ, fi„1/Ni иэ оперативного запоминающего устройства 17 поступают в вычислительное устройство 21., реализующее операцию г gT ЕЕ СТ2f. + ).

1 1

Определенное значение остаточного ресурса через промежуточное запоминающее устройство 22 поступает в регистрирующее устройство

3 729482 4 а выход вычислительного устройства — с входом регистрирующего устройства.

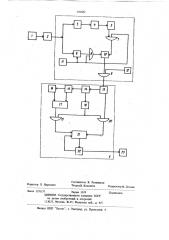

На чертеже показана структурная схема предложенного устройства.

Устройство содержит преобразователь 1, усилитель 2, блок сбора информации и блок обработки информации. Блок сбора информации включает ограничитель 3 уровня нагрузок, вход которого соединен с выходом усилители 2, счетчик 4 интервалов времени, вход которого 10 соединен с выходом ограничителя 3 уровня на,грузок, промежуточное запоминающее устрой,ство 5, вход которого соединен с выходом счетчика 4 интервалов времени, кольцевое запоминающее устройство 6, вход которого соединен с выходом усилителя 2, схемы совпадения 7 — 9, две 7 и 8 из которых соответственно соединены с выходами промежуточного запоминающего устройства 5 и кольцевого запоминающего устройства 6. Кроме того, блок сбора эо информации содержит долговременное запоминающее устройство 10, входы которого соединены с выходами схем 7 и 8 совпадения, а выход — со входом схемы 9 совпадения, переключатель 11 смены режима, соединенный с. 2« кольцевым запоминающим устройством 6 и схемами 7,, 8 совпадения; переключатель 12 подачи информации, соединенный со схемой 9 совпадения.

Блок обработки информации включает опе- 30 ративное запоминающее устройство 13, вход которого соединен с выходом схемы 9 совнадения, анализатор 14 спектра, вход которого соединен с одним иэ выходов оперативного запоминающего устройства 13, дискриминатор 15 спектральных составляющих, вход которого соединен с одним из выходов анализатора 14 спектра, блок 16 определения, выносливости, вход которого соединен с одним из выходов дискриминатора 15, промежуточное запомина- 4Г ющее устройство 17, выходы которого соединены с другим выходом дискриминатора 15 спектральных составляющих и выходом блока

16 определения выносливости, блок 18 задержки, выход которого соединен с другим выходом анализатора 14 спектра, схемы совпадения

l9 и 20,,входы одной из которых соединены с входом промежуточного запоминающего устройства 17 и одним из выходов блока 18 задержки, а выходы другой — c другим выхо- «о дом блока 18 задержки и другим выходом оперативного запоминающего устройства 13, Кроме того, блок обработки информации включает вычислительное устройство 21, входы которого соединены с выходами схем 19 и 20 «« совпадения и другого промежуточного запоминающего устройства 22, вход которого соединен с выходом вычислительного устройства 21, и связанного с ним обратной связью, Устрой729482

Составитель В. Ротницкая

Техред Н, Ковалева

Редактор Л. Народная

Корректор М. Демчик Подли сное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 1253/37 Тираж 1019

ЦНИИПИ Государственного комитата СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5