Программно-задающее устройство

Иллюстрации

Показать всеРеферат

-всссвеэмйл

3 .М (Щ: i..; -..:,в", 4 я

Союз Советских

Социалистических

Республик

О П И С А Н И В"ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6)) Дополнительное к авт. свид-ву— (22) Заявлено 11,1177 (21) 2542986/18-24 с присоединением заявки Йо (23) Приоритет— (51)М. Кл.2

G 05 В а8

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 2504.80. Бюллетень М 15

Дата опубликования описания 2504.80 (53) УДЯ 621 503 °

° 55 (088 ° 8) (72) Авторы изобретения

Л, Р . Фрейдель и П. И. Файн (71) Заявитель (54) ПРОГРАММНО-ЗАДАКЩЕЕ УСТРОЙСТВО

Предлагаемое устройство относится к автоматическому управлению, и может быть использовано в устройствах программного регулирования параметров различных технологических процессов.

Известно программное задающее устройство, содержащее блоки набора программы, каждый иэ которых состоит иэ схемы задания скорости, схемы задания уровня и переключающей схемы,. причем вход схемы задания скорости подключен к управляемому делителю частоты, выход схемы задания уровня подключен к реверсивному счетчику, один выход переключающей схемы соединен со схемами задания скорости и уровня, другой — с переключающей схемой последующего блока набора программ, а входы переключающей 2О схемы соединены, соответственно, с выходом схемы задания уровня и выходом переключающей схемы предыдущего блока набора программы (1).

Однако, применение управляемого делителя частоты существенно затрудняет получение требуемой в современных условиях дискретности задания скорости изменения выходного сигнала.

Кроме того, устройство, построенное 30 по такому принципу, содержит очень большое число схем переключения и блоков набора программ, равное числу участков задаваемой программы.

Известно также программное задающее устройство, содержащее блок задания уровня и скорости, реверсивный счетчик со схемой совпадения, один вход которого соединен с выходом делителя частоты, другой — с выходом блока задания уровня, а выход подключен ко входу коммутатора, причем вход блока задания уровня подсоединен к выходу коммутатора (2).

Это устройство содержит один блок набора программы,.однако применение управляемого делителя частоты оно также не обеспечивает получение требуемой дискретности задания скорости изменения выходного сигнала, а применение коммутатора приводит к снижению надежности устройства.

Наиболее близким техническим решением к предлагаемому изобретению является программно-задающее устройство, содержащее блок постоянной программируемой памяти, выход которого соединен с входом основного блока оперативной памяти, блок сравнения, первый вход которого соеди729553 нен с первым выходом основного блока оперативной памяти, блок задания программы, выход которого соединен с входом блока постоянной программи руемой памяти и блок управления (3).

Недостатком устройства является то, что--оно содержит управляемый генератор частоты и цифроаналоговый преобразователь, не обеспечивающие получения выходного сигнала с точностью, удовлетворяющей требованиям промышленности, а, следовательно, реализация программных задающих устройств, построенных по подобной структуре, является недостаточно рациональной.

Целью изобретения является повышение точности и надежности устрой-. ства.

Это достигается тем, что - в устройство введены дополнительный блок

1 оперативной памяти и блок алгебраического суммирования, причем второй выход основного блока оперативной памяти соединен с первым входом блока алгебраического суммирования, второй вход которого соединен с вы.ходом дополнительного блока оперативной памяти, выход блока алгебраического суммирования соединен с входом дополнительного блока оперативной памяти и со вторым входом блока сравнения, выход которого соединен с входом блока управления.

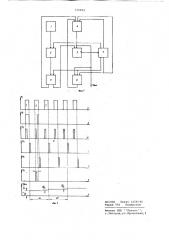

На фиг. 1 представлена функциональ. ная схема программно-задающего устройства; на фиг. 2 — диаграммы импульсов. Устройство содержит блок задания программы 1, блок постоянной программируемой памяти 2,основной блок оперативной памяти 3, блок ал.гебраического суммирования 4, блок сравнения 5, дополнительный блок оперативной памяти 6 и блок управления 7 устройство работает следующим образом.

После включения устройства в сеть из тактовых импульсов 04 блока 7 формируются импульсы 0, поступающие на управляющий вход блока 2.

Каждый импульс О дает команду на считывание чисел, хранимых в блоке 2, а адреса этих чисел определяются количеством /. импульсов поступивших на управляющий вход блока 2 с. момента включения устройства, Первый импульс 0О считывает первое число находящееся в, блоке 2 — на""a ло первого участка () < и вводит его в блок оперативной памяти 3. Число

U при этом возникает на первом и втором выходах блока 3.

На эагних фронтах импульсов 0 формируются следующие поочередно импульсы 04 и 0, поступающие с чет вертого и второго выходов блока 7 на управляющие входы блоков 6, 4 и 6,3, соответственно.

Первый импульс 04 дает команду алгебраического суммирования числа

Uz на втором выходе блока 3 с числом на выходе блока 6 .

Так как в рассматривае/ый момент времени запоминающие элементы (например, регистры) блока 6 не заполнены, на выходе блока алгебраического суммирования возникает

S число 0 и

Блок 7 содержит обычную триггерную схему запрета, которая после поступления каждого импульса 0 на управляющий вход блока 2 запреща ет прохождение следующих импульсов до появления ; импульса на выходе блока 5. Непосредственно после включения устройства схема запрета устанавливается в открытое состояние.

К моменту появления второго импульса 04 на третьем управляющем входе блока 4 возникает импульс U который дает команду на передачу выходного числа блока 4 на второй вход блока 5.

В связи с тем, что в рассматриваемый момент времени на первый и второй входы блока 5 поступают одина/ ковые числа, а именно 0я, на выходе блока 5 появляется импульс U который через временную э адержку-1 возвращает триггерную схему запрета в блоке 3 в исходное состояние, разрешающее прохождение еще одного импульса О

В результате поступления второго импульса U на управляющий вход блока 2 происходит считывание следующих чисел U y, и BURY которые поступают на первый и второй выходы блока 3 соответственно.

Далее,. в момент окончания второго импульса 0 возникает первый импульс U, который обеспечивает передачу выходного числа блока 4 в блок

6 - однояременным запретом считывания информации со второго выхода блока 3. В результате на выходе блока оперативной памяти б возникает число 0н .

«

Далее, в момент появления третьего тактового импульса U< возникает третий импульс U з и вновь, прои сходит сравнение кодов с выходом блока 4 и 3. Однако теперь на первом выходе блока 3 существует число

UK - ордината конца первого участка, и, так как U, 4 0„, совпадения кодов не происходит, импульс 0 не появляется и, следовательно, импульсы 0< не проходят.

Затем, в результате появления второго импульса 04 происходит либо суммирование числа 0й с числом Ь 04, либо вычитание этого же числа из Оя в зависимости от значения знакового разряда (О или / ) числа 0н . В этот момент

729553 времени выходная величина уэеличивается на цЛ.

В дальнейшем происходят аналогичные процессы, поэтому, в момент прохождения каждого из импульсов

0л происходит увеличение выходной величины на приращение 60Л, 5 а выходная величина Озь, в случае ее нарастания, принимает последовательно следующие значения: ц ц + U UH4+Еb,u н н л причем каждое из этих значений остается неизменным в течение шага квантования ht . Таким образом, реализуется зависимость Ugь1 Ц для

1-го участка, представленная ранее 15 выражением

U =0 +аО

2.

1 я

Затем, когда U +> достигает значения О, на выходе блока 5 возни- 2ц кает сигнал, пропускающий следующий импульс 0, который считывает следующие числа — 0 к и h,U< из блока 2; эти числа поступают на первый и второй выходы блока 3, соответственно, после чего ближайший импульс

U4 осуществит первое суммирование или.вычитание чисел 0к и h.Î а дальше пройзойдут процессы, аналогичные описанным и формирующие закон изменения U b,> на втором участке, ЗО потом на третьем участке и т.д. до конца заданной программы.

Построение программно-задающего устройства по предлагаемой схеме позволяет существенно повысить точность реализации заданной программы изменения выходной величины устройства по сравнению с известными устройствами.

К составляющим результирующей по- 40 грешности предлагаемого устройства относятся: погрешность, называемая конечностью значений приращений AU; погрешность, определяемая дискретностью младших разрядов чисел концов участков U> U, ...,Ок, по45 грешностью шага квантования

Первые две составляющие погрешности могут быть уменьшены до сколь угодно малой величины при возрастании числа разрядов чисел U и 6 Ц . 50

Например, для снижения этих составляющих до 0,01% для представления чисел ОК и а0 необходимо 4 и 1 десятичных разряда, соответственно.

Погрешность шага квантования возникает при изменениях частоты =„

А генератора тактовых импульсов, Эта погрешность минимизируется путем ,применения кварцевого генератора тактовых импульсов с делителем час-. тоты на дискретных элементах, нестабильность частоты которого и соответствующая составляющая погрешность предлагаемого, устройства составляют сотые доли процента.

Предлагаемое устройство существенно превосходит известное по точности, что обеспечивает целесообразность его применения для прецизионного контроля и регулирования, обеспечивающего высокое качество выпускаемой продукции. Кроме того, в предлагаемом устройстве отсутствует цифроаналоговый преобразователь и сложные коммутирующие устройтва.

Устранение цифроаналогового преобразователя и коммутаторов значительно повышает надежность в работе устройства и обеспечивает возможность его применения для контроля и регулирования ответственных технологических параметров.

Формула изобретения

Программно-задающее устройство, содержащее блок постоянной программируемой памяти, выход которого соеди- нен с входом основного блока оперативной памяти, блок сравнения, первый вход которого соединен с первым выходом основного блока оперативной памяти, блок задания программы, выход которого соединен с входом блока постоянной программируемой памяти и блок управления, о т л и ч а ющ е е с я тем, что, с целью повышения точности и надежности устройства, в него введены дополнительный блок, оперативной памяти и блок алгебраического суммирования, причем второй выход основного блока оперативной памяти соединен с первым входом блока алгебраического.суммирования„второй вход которого соединен с выходом дополнительного блока оперативной памяти, выход блока алгебра- ического суммирования соединен с входом дополнительного блока оперативной памяти и со вторым входом блока сравнения, выход которого соединен с входом блока управления.

Источники информации, принятые во внимание при экспертизе ,l. Авторское свидетельство СССР

9463100, . кл. G 05 В 19/04, 1972.

2. Авторское свидетельство СССР

9265220, кл, G 05 В 19/02, 1964.

3. Авторское свидетельство СССР

9239406, .кл, G 05 В 19/18, 1963 (прототип) .