Логическое устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ нн729588 (61) Дополнительное к ввт. сеид-ву (22) Заявлено 09.11.77 (21) 2543272/18-24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 250430. Бюллетень ¹ 15

Дата опубликования описания 30. 04. 80 (51) м. кл.2

С 06 Г 9/00

Государственный комитет

СССР ло делам изобретений и открытий

Щ) УДК, 681. 325. 65 (088.8) (72) Авторы изобретения

В. Ф. Муравьев и В. А. Полунов (71) Заявитель (54) ЛОГИЧЕСКОЕ УСТРОИСТВО

Изобретение относится к вычислительной технике и может быть использовано в качестве управляющего устройства в информационно-управляющих сйстемах.

Известны логические устройства, 5 содержащие вычислительные машины, входные и выходные регистры, блоки цифроаналогового преобразования, селекторы каналов и дешифраторы выполняющие функции анализа состояния про-1О цесса и формирования последовательностей команд управления технологического процесса (1).

Недостаток известных устройств состоит в большом объеме оборудования. 15

Наиболее близким к предлагаемому техническому решению является логическое устройстно, содержащее блок па,мяти в виде матрицы элементов памяти, блок управления, соединенный первой 20 группой входов с группой выходов блока дешифрации связей, а второй группой входов — с группой выходов блока дешифрации состояния, управляющий вход которого и управляющий вход блока де-25 шифрации связей подключены к соответствующим управляющим выходам блока управления, и две группы элементов И, входы которых соединены с соответствующими выходами блока управления, выходы к-тых элементон И первой и второй групп подключены соответственно к первым и вторым входам элементов памяти к-той строки матрицы (2).

Целью изобретения является уменьшение объема оборудования.

Поставленная цель достигается тем, что блок памяти выполнен н ниде треугольной матрицы элементов памяти, причем третьи и четвертые входы элементов памяти к-ой строки матрицы со-. единены соответственно с первыми и нторыми входами элементов памяти к-ой строки и к-ми входами из первой и нторой групп входов блока дешифрации связей, к-ый вход из третьей группы входов которого соединен с к-ым входом из первой группы входов блока дешифрации состояния и первыми выходами элементов памяти к-ой строки к-ro столбца матрицы, к-ый вход из второй группы входов блока дешифрации состояния подключен ко нторым выходам элементов памяти к-ro столбца матрицы (к=1,К);

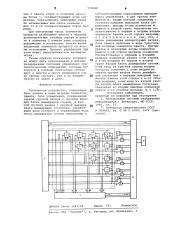

На чертеже показана блок-схема логического устройства.

Схема устройства содержит блок 1 памяти из образующих матрицу элементов 2 памяти, первый 3 и вто729588 рой 4 входы элементов памяти 2, элементы И 5, блок 6 управле-.. ния, блок 7 дешифрации состояния, блок 8 дешифрации связей, первый 9 и второй 10 выходы элементов памяти 2, третий 11 и четвертый 12 входы элементов памяти 2, шины 13 выбора операций, шины 14 ограничений на одновременность, шины 15 запрета, шины

16 анализа связей и объект 17 управления.

Предположим, что каждый элемент

2 памяти выполнен в виде контакта, соединяющего один иэ входов элемента .с одним из выходов. Предположим также, что имеется пять команд (этому примеру соответствует блок-схема на чертеже), обозначенные через Al, A2, А3, А4 и А5, и что реализация управления состоит в выдаче этих команд, например в последовательности Al A5

А3, А2 А4. Пусть объект управления при невозможности выполнить команду

А5 (например, из-за отказов оборудования, выполняющего эту команду) допускает выполнение команды AÇ. В других же случаях замена команд недопустима.

Построим квадратную матрицу переходов размеров 5 х 5, причем будем считать, что номеру команды соответствует одноименные столбец и строка.

Возьмем, для примера, команду AÇ и запишем в третий столбец и пятую строку (номер предшествующей команды) единицу, а в остальные клетки столбца занесем нули. Аналогичным образом для каждой команды заполним матрицу. Для рассматриваемого примера матрица выглядит следующим образом:

Х 0 00 1 ох О>О

0 1 ХОО

000 Х 0

00 10Х

Конструкция блока 1 памяти выполнена так, что матрица элементов 2 соответствует части матрицы переходоЪ, лежащей выше главной диагонали. Для работы устройства необходимо» чтобы каждый элемент 2 матрицы был скоммутирован по следующим правилам: а) если в данной клетке матрицы, расположенной выше главной диагонали, и в клетке, симметричной ей относительно главной диагонали, то стоит единица связи между входами и выхоI дами соответствующего элемента 2 отсутствуют. Например, элемент 2 верхней строки и левого столбца блока 1, соответствующий первой строке и второму столбцу матрицы переходов (в блоке 1 отсутствуют элементы 2 для главной диагонали) должен обеспечивать во всех случаях разрыв между входами и выходами; б) если в данной клетке матрицы, расположенной выше главной диагонали, стоит единица, то элемент 2 должен коммутировать вход 3, подключенный к шине выбора операций на выход

10, подключенный к шине анализа связи; в) если в клетке матрицы, расположенной ниже главной диагонали, стоит единйца,.то элемент 2 должен коммутировать вход 11, подключенный к шине выбора операций, на выход 9, подключенный к шине запрета;

r) если в заданной программе допускается замена одной команды, выполнение которой в данный момент не представляется возможным, другой, то в соответствующем этой предшествующей

15 команде элементе 2 рабочим входом должны быть не входы 3 или 11, а входы 4 или 12, подключенные к шине ограничения на одновременность.

Устройство работает следующим обраgP зом.

При подаче сигналов от блока 6 управления на шины 13 и 14 информация с элементов 2 выдается через шины 15

16 в блок 7 дешифрации состояния элементов. Блок 7 сигнализирует в блок 6 о столбце, на шинах 15 и 16 которого присутствует нулевой сигнал . Номер этого столбца однозначно соответствует номеру команды, которую необходимо выполнить. Блок 6 выдает эту команду в объект 17 и ждет уведомления о выполнении этой команды. Получив уведомление, блок 6 вновь возбуждает шины

13 и 14, блокируя при этом с помощью соответствующих элементов И 5 шины 13 и 14 строки, номер которой равен но— меру выполненной команды.

Таким путем происходит последовательное чтение номеров, команд, кото-. рые необходимо выдавать в объект 7.

Если вместо уведомления об исполнении команды блок 6 получает от объекта сигнал о невозможности ее выполнить, то блок 6 снова возбуждает шины 13 и 14, блокируя при этом указан45 ные шины строк элементов 2 исполненных команд и шину 14 строки, соответствующей номеру невыполненной команды. При этом, если команды связаны не жестко, будет выполняться следующая

$p команда.

Блок 8 во время работы устройства определяет те элементы процесса, которые уже выполнены, а также те элементы процесса, которые еще не выполнены, так как сигналы с блока 6 с выходов столбцов матрицы по шинам 13 и

14 поступают в блок 8. Кроме того, блок 8 выдает в блок 6 информацию о том, от каких элементов процесса зависит любой выбранный элемент процес<0 са, так как данная информация поступает с элементов 2 памяти через шины запрета 15 в блок 8.

Если число элементов процесса из цикла в цикл изменяется, например

65 уменьшается, то достаточно в элемен729588

Формула изобретения

ЦНИИПИ Заказ 1261 f 42 Тираж 751 Подпис ное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 тах 2 памяти строк и столбцов матрп-цы блока 1, соответствующих этим элементам, перезаписать зависимые связи на независимые или снять сигналы с шин 13 и 14 соответствующих строк матрицы. 5

При увеличении числа элементов процесса необходимо ввести в матрицу дополнительные столбцы справа и ввести в элементы 2 памяти этих столбцов информацию о логических связях вновь введенных элементов процесса со всеми остальными. Процесс управления при этом может перестраиваться автоматически.

Таким образом логическое устройст во может быть использовано в автоматизированных системах управления технологическими операциями, которые находятся в сложных логических связях друг с другом и могут изменяться как по своему составу, так и по взаимо- 20 связям из цикла в цикл.

Логическое устройство, содержащее блок памяти в виде матрицы элементов памяти, блок управления, соединенный первой группой входов с группой выходов блока дешифрации связей, а второй группой входов с группой выходов блока дешифрации состояния, управляющий вход которого и управляющий вход блока дешифрации связей подключены к соответствующим управляющим выходам блока управления, и две группы эле ментов И, входы которых соединены с соответствующими выходами блока управления, выходы к-тых элементов И первой и второй групп подключены соответственно к первым и вторым входам элементов памяти к-ой строки матрицы, о т л и ч а ю щ е е с я тем, что, с целью уменьшения аппаратурных затрат, блок памяти выполнен в виде треугольной матрицы элементов памяти, причем третьи и четвертые входы элементов памяти к-ой строки матрицы соединены соответственно с первыми и вторымй входами элементов памяти к-ой строки и к-ми входами из первой и второй групп входов блока дешифрации связей, к-ый вход из третьей группы входов которого соединен с к-ым входом из первой группы входов блока дешифрации состояния и первыми выходами элементов памяти к-ой строки и к-ro столбца матрицы, к-ый вход из второй группы входов блока дешифрации состояния подключен ко вторым выходам элементов памяти к-ro столбца матрицы (к = 1,R).

Источники информации, принятые во внимание при экспертизе

1. Электронные системы отображения информации, М.: Воениздат, MO СССР, 1966, гл. 13.

2. Авторское свидетельство СССР

Р 368602, кл. G 06 F 9/00, 1970 (прототип) .