Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскмх

Соцмалмстическмк

Республмк

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

„„ 729640

4i

4 (61) Дополнительное к ввт. свид-ву (22) Заявлено 24.11.77 (2< ) 2546727/18-24 (5I )M. Кл.

Я 11 С 27/00 с прмсоединенмем заявки.%. Гвсударстеемвй каммтет

СССР (23) Приоритет во делам мзоеретеммй и вткрытмй (53) УДК 681.327..66 (088.8) Опубликовано 25.04.80. Бюллетень .%15

Дата опубликования описания 25.04.80

Л. H. Григорьев, А. У. Ялышев, Г. С, Сергеев, А. Ф. Защелкни и В. B. Козлов (72) Авторы изобретения

Государственный научно-исследовательский институт теплоанергетического приборостроения (7! ) Заявитель (S4) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и вычислительной технике и может быть использовано для запоминания аналоговой информации и установках различного назна чения.

Известно аналоговое запоминающее устройство, содержащее интегратор (1), Быстродействие этих устройств ограничено, так как в них процесс запоминания непрерывного сигнала включает в себя промежуточное преобразование напряжения в частоту или несколько циклов сравнения запоминаемого сигнала с суммой дискретных сигналов.

Из известных устройств наиболее близ-ts ким к предлагаемому по технической сущности является аналоговое запоминающее устройство, содержащее переключатель, интегратор, вход которого соединен с перекидным контактом переключателя, один 2О из контактов которого соединен с входом устройства: между выходом интегратора и другим контактом переключателя включен блок коррекции, выполненный из широтно-импульсного модулятора (ШИМ), генератора высокой частоты (ГВЧ), двух триггеров, двух схем совпадения и узла управления $2) . Выходное напряжение интегратора преобразуется с помощью

ШИМ в длительность импульсов, В начале каждого импульса ШИМ запускается ГВЧ. Число импульсов, генерируемых

ГВЧ за время прохождения одного импульса ШИМ, пропорционально выходному напряжению интегратора. Если это число оказывается четным, то блок коррекции формирует напряжение отрицательной полярности, которое подается на вход интегратора и привоцит к увеличению его выходного напряжения. Через некоторое время напряжение интегратора увеличивается настолько, что,число импульсов, генерируемых

ГВЧ за время прохождения одного импульса ШИМ, увеличивается на единицу и становится нечетным, вслецствие чего блок коррекции формирует напряжение положительнои полярности, а выходное напряжение интегратора уменьшается. В ре729640 зультате повторения описанных процессов компенсируется дрейф выходного напряжения интегратора и это напряжение остается постоянным с колебаниями с малой амплитудой,, а устройство остается в одном из устойчивых состояний, число которых равно числу импульсов, генерируемых ГВ l за время прохождения опного импульса ШИМ.

Точность работы этого устройства or- 10 раничена, так как при большом числе устойчивых состояний устройства даже незначительные изменения коэффициента передачи ШИМ и частоты слепования импульсов

ГВЧ из-за воздействия помех и изменения 1 питаюгцих напряжений приводят к тому, что при напряжении на входе ШИМ, соответствующем четному числу импульсов

ГВЧ, фактическое число этих импульсов оказывается нечетным. При этом блок

20 коррекции формирует напряжение с поляр— ностью, противоположной по отношению к . требуемой, вследствие чего система переходит в соседнюю точку устойчивого

25 равновесия. При многократном возцейС ствии помех система, послеповательно ггерехоця из одного устойчивого состояния в другое, теряет запомненную информацию.

ЗО

Быстродействие этого устройства также ограничено, так как его принцип пействия основан на преобразовании непрерывного сигнала в цлительность импульсов.

Целью изобретения является повыше35 ние точности и быстропействия аналогового запоминающего устройства.

Для этого в аналоговое запоминающее устройство, содержащее ключ, первый вход которого соединен со вхопом устройства, интегратор, вхоп которого соединен с выходом ключа, а выход интегратора соединен с выходом устройства, введены послецова гельно соединенные преобразователи напряжения и блок восстановления постоянной составляющей напряжения, выход которого подсоединен ко второму входу ключа, выход интегратора соединен со входом первого преобразователя напряжения, выход последнего преобразователя напряжении соединен с вхопом блока восстановления постоянной составляющей напряжении.

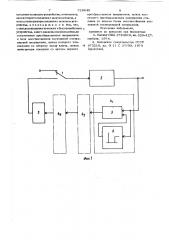

На фиг, 1 показана функциональная схема предлагаемого устройства, на фиг. 2 — временная циаграмма работьг устройства.

Аналоговое запоминающее устройство содержит ключ 1, интегратор 2, блок. восстановления постоянной составляющей напряжения 3, преобразователи напряжения 4.14,2,4 г...4п. Причем каждый преобразователь напряжения 4 выполнен„ например, на операционном усилителе 5 и пвухпозиционном реле 6, г

На фиг. 2 приняты следующие обозначения переменных: / — сигнал на выходе интегратора 2 и входе преобразователя 4.1, У и У вЂ” соответственно сигналы на вхопах преобразователей 4,2 и 4.3,, — сигнал на выходе преобразователя 4,3 и на входе блока 3, ( сигнал на выходе блока 3, подаваемый в режиме запоминания сигнала на вхоп интегратора 2 (с помощью ключа 1) / наибольшее значение сигналов V / /г«

В режиме интегрирования связь между выходом блока 3 и входом интегратора

2 разомкнута ключом 1.

Двухпозиционное реле преобразовывает сигнал в соответотвлл с выражением

fb гг чг "«г,. < Q y g ж.,— (1)

Qy$ „. «у, оиру

r о гпе 7 — сигнал на выходе пвухпозиционного реле и на втором входе операционного усилителя.

В качестве цвухпозиционного реле может быть использован компаратор, попол:ненный вхопной цепью смешения и выхопной цепью ограничения сигнала.

Операционный усиггитель преобразовывает сигнал в соответствии с выражением

М„,1=2(; -Z, ) (2) гце, и — сигналы соответственно на вхоце и выходе операционного усилиТОЛЯ.

Подставив вьгражение (1) в выражение (2), получаем У. пюм У < О,б f

ЯЬ; -О,5 г „ ) пргл «, > О,5 "«

График зависимости сигнала г от сигнала 7 (см. фиг. 2), построенный в соответствии с выражением (3) при 1 =1, препставляет собой ломанную линию 0-М- г(-Q . Из этой характеристики следует, что при изменении сигнала Q от О пo г сигнал (пважпь изменяется по линейг1ому зак, чу "т 0 по и один раз — жа г. м от г Г пгг C).

Аналогично в соответствии с в.—. раже) нием (3), при каждом изменении сиг нале

729640

Х=У -ОДУ и+1 o (4) 25 от О по Ч,, сигнал Ч, изменяется но линейному закону цважпы от О цо Y u о опии раз — скачком от У ао 0 (см., например, участок 0-М4 — Ь1 — Q ãÐ÷Ôèêà зависимости сигнала Ч от сигнала У ), 5 и так палее.

В результате при изменении сигнала от 0 цо сигналы У9 Уэ У) g не выходах преобразователей 4.1, 4.2,...4„ изменяются по линейному закону от О по и

У вЂ” соответственно 2,4, ... 2 раз и 1,3...(2 -1) раэ — скачком от У„цо О.

Ф

Блок восстановления постоянной составляющей напряжения 3, в качестве которого может быть использован суммирую15 щий усилитель постоянного тока, пополненный входной цепью смешения, преобразует сигнал в соответствии с выражением гце Yд„и Х вЂ” сигналы соответственно на входе и выходе блока 3.

На фиг. 2 привецен график зависимос-!

I ти сигнала Х от сигнала У, построенный в соответствии с выражением (3) и (4) пля числа п преобразователей 4,1...

4д> равного "3". Из рассмотрения этого графика следует, что при изменении выхоцного сигнала У1 интегратора 2 от О по У„сигнал Х изменяется от — 0,5 У„ по 0,5У по линейному закону 2 раз и от 0 5 Y ao -0,5 У вЂ” скачком, (2" -1) З5 раз. В соответствии с .--им графиком, если в момент времени, предшествующий.моменту переключения устройства иэ режима интегрирования в режим запоми40 нания, сигнал Y имеет значение, например, равное Уд, то сигнал в этот момент времени имеет значение, равное

-Ъ

Устройство работает слепую1цим об45 разом.

Для переключения устройства иэ режима интегрирования в режим запоминания необхоцимо соединить ехоп интегратора 2 с выходом блока 3 с помощью

50 ключа 1. Г1ри этом на вхоц интегратора

2 подается сигнал Х =Х,, имеющий положительную полярность, вследствие чего выходной сигнал У интегратора 2 уменьшается. По постижении сигналом Ч4

55 значения /,5 сигнал Х становится равным нупю, сигнал Ч перестает изменяться, Если в дальнейшем (например, из-за воздействия помех) сигнал Yg иэменится на некоторую величину, например, уменьшится по значения У, то сигнал

Х становится отрицательным и равным

-Х, что привепет к увеличению сигнала

У, т. e. восстановлению его значения

Таким образом, после переключения из режима интегрирования в режим запоминания устройство приходит в состояние устойчивого равновесия, при этом запоминается значение выхопного сигнала Ч интегратора, равное Ч .

В зависимости от значения сигнала

Ч<, соответствующего моменту переключения иэ режима интегрирования в режим запоминания, устройство может прийти также и в любое цругое устойчивое состояние, причем число этих состояний, определяемое числом изменения полярности сигнала Х с отрицательной на положительную при изменении Ч от 0 по

Ч, равно 2 . Точность запоминания сигнала повышается с увеличением числа устойчивых состояний, т. е. с увеличением числа преобразователей 4.1...4 и устройства. Это увеличение не привоцит к потере устойчивости устройства в режиме запоминания, так как известно, что устойчивость замкнутой системы, составленной из опного интегратора и нескольких безинерционных звеньев преобразователей 4.1...4n и блока 3, не нарушается при увеличении числа беэинерционных звеньев.

Устройство имеет достаточно высокую помехоустойчивость,.

При малейшем изменении выхоцного сигнала Ч интегратора 2 из — за возцействия помех в режиме запоминания на вход этого интегратора немедленно поступает по замкнутому контуру усиленный сигнал Х отрицательной обратной связи, который восстанавливает прежнее значение сигнала Ч

Устройство имеет высокое быстродействие, так как все его блоки преобразователи 4.1...4ии блок 3, используемые цля запоминания выходного сигнала интегратора, являются беэинерционными.

Использование новых блоков преобразователей и блока восстановителей постоянной составляющей напряжения в аналоговом запоминающем устройстве повышает его точность,, помехоустойчивость. и быстродействие.

Формула изобретения

Аналоговое запоминающее устройство, содержащее ключ, первый вход к о тор ого

7 729640 В соединен со входом устройства, интегратор, преобразователя напряжения, выход посвход которого соединен с выходом ключа, а леднего преобразователя напряжения соевыход интегратора соединен с выходом уст- динен со входом блока восстановления посройства, о т л ич а ю m е е с я тем, что, тониной составляющей напряжения. с пельюповышения точности и быстродействия g Источники информации, устройства, внего введены последовательно принятые во внимание при экспертизе соединенные преобразователи напряжения 1, Патент США 3784919, кл. 328-127, и блок восстановления постоянной состав- опублик. 1974. ляющей напряжения, выход которого под- 2. Авторское свидетельство СССР соединен ко второму входу ключа, выход 30 473218, кл. Gr 11 С 27/00, 1973 интегратора соединен со входом первого (прототип).

Уо У

Х

ОУд

Составитель И. Зачинайко

Редактор Т, Морозова Техред "С. Мигай. Корректор И. Сининка"

Заказ 1290/44 Тираж . 662 Подписное

UHHNIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4