Логарифмический аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советск ни

Социалистические

Республик

40 (61) Дополнительное к авт. саид-ву (22) Заявлено 18.10.78 (21)2675149/18-2 1 с присоединением заявки Ж (23) П р нор итет

Опубликовано 25.04.80. Бюллетень № 1

Дата опубликования описания 28,04.80

Геоударотееииьй комитет ио делам изобретеиий и открытий

1.325

В. Е. Ямный (72) Автор изобретения

Бепорусский ордена Трудового Красного Жамени государственный университет им. B. И. Ленина (7I) Заявитель (54) ЛОГАРИФМИЧЕСКИЙ АНАЛОГО-ЦИФРОВОЙ

ПР ЕОБР А ЗОВ АТЕЛЬ

Изобретение относится к информационно-измерительной технике .

Известны логарифмические аналогоцифровые преобразователи, содержащие генератор экспоненциального напряжения в виде RC-цепи, компаратор и блох управ5 леши, в которых выходной код образуется подсчетом количества импульсов, прошедших за время разрядки конденсаторе до уровня преобразуемого напряжения 1.1), i0

Недостатох этих преобраэователей—

1Ьльшое время преобразования.

Известен также логарифмический аналого-цифровой преобразователь, содержеший ЙС -цепь, между резистором которой

15 и обшей шиной питания включен первый электронный ключ, источник опорного напряжения, соединенный через второй электронный ключ с КС-цепью и неинвертйруюшим входом буферного усилителя, выход которого соединен с его инвертируюшим входом и первым входом компаpampa, выход которого подключен к к первому входу блока управления, второй вход которого соединен с генератором импульсов, первый и второй вьпод блока управления соответственно подключен к унравляюшему входу первого и второго электронного ключа, третий и четвертый выход — соответственно к входу счетчика стерших и младших разрядов, пятый выход — к установочному входу счетчика, а шестой выход — к разрядному ключу интеграторе (21 .

Этот преобразователь также обладает большим временем преобразования.

11ель изобретения — повышение быстродействия устро йства.

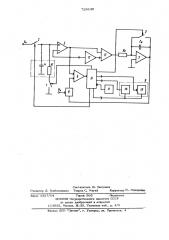

Это достигается тем, что в преобразователе, содержащем AC-цепь, между резистором которой и обшей шиной питания включен первый элехтронный ключ, источшпс опорного напряжения, соединенный через второй электронный ключ с AC-цепью и неинвертируюшим входом буфепного уст1лителя, выход которого соединен с его инвертируюшим входом и первым. входом компаретора, выход которого под3 7298 ключен к первому входу блока управления, второй вход которого соединен с генератором импульсов, первый и второй выход блока управления соответственно подключен к управляющему входу перво5 го и второго электронного ключа, третий и четвертый выход — соответственно к входу счетчика старших и младших разрядов, пятый выход — к установочному входу счетчика, а шестой выход — к разрядному ключу интегратора, выход интегратора подключен к первому входу сумматора, второй вход которого соединен с входной клеммой устройства, а выход подключен к первому входу компаратора, второй вход которого подключен к первому входу дифференциального усилителя через дополнительньrA усилитель, и к второму входу непосредственно, а вход ин, тегратора соединен с выходом дифферен- о циального усилителя, На чертеже дана функциональная элек, трическая схема предлагаемого устройства.

В исходном состоянии ключи 1, 2, 3 замкнуты. Напряжение на конденсаторе 4: равно опорному напряжению E . Это напряжение прикладывается через буферный усилитель к первому входу компаратора 6. Выходное напряжение интегратора 7 в исходном состоянии равно gp рулю. Преобразуемое напряжение U через сумматор 8 прикладывается к второму входу компаратора 6. По команде

Пуск обнуляется и переводится в режим суммирования счетчик 9, ключ 2 размыкается и начинается экспоненциальный разряд конденсатора 4 через резистор 10.

При достижении напряжения на конденсаторе 4 уровня О„сработает компаратор 6. Следующим от этого момента щ импульсом генератора 11 блок управления переводит счетчик 9 в режим вычитания и размыкает ключи 1 и 3, при этом разряд конденсатора 4 прекращается, а на вход сумматора 8 начинает 45 поступать линейно нарастающее напряжение от интегратора 7. Скорость нарастания этого напряжения определяется величиной напряжения на выходе буферного усилителя 5 и коэффициентом усиления усили теля 12 (коэффициент усиления усилителя 13 можно принять равным единице). Скорость нарастания выбирают с помощью изменения коэффициента усиления усилителя 12 такой величины, чтобы разряд у конденсатора 4 через резистор 10 в момент равенства напряжения на конденсаторе и преобразуемого напряжения за время, равное периоду импульсов генера

40 ф тора 11, было бы равно напряжению на выходе интегратора за это же время.

Тогда на участке между двумя импуль=ами будет осуществляться линейная интерполяция логарифмической функции преобразователя. Во время экспоненциального разряда конденсатора импульсы от генератора 11 поступают в старшие разряды .14 счетчика 9 и увеличивают его содержимое, а во время работы интегратора импульсы от генератора 1 1 импульсов поступают в младшие разряды 15 счетчика 9 и уменьшают его содержимое. При равенстве напряжения на обоих входах компаратора 6 он воз вращается в исходное состояние, а блок

16 управления останавливает работу счетчика 9. В счетчике 9 запишется число эквивален тное изм еря ем ому нап ряжен ию, Формула изобретения

Логарифмический аналого-цифровой преобразователь, содержащий ЙС-цепь, между резистором которой и общей шиной питания включен первый электронный. ключ, источник опорного напряжения,соединенный через второй электронный ключ с КС-цепью и неинвертируюшим входом буферного усипителя, выход которого соединен с его инвертирующим входом и первым входом компаратора, выход которого подключен к первому входу блока управления, второй вход которого соединен с генератором импульсов, первый и второй выход блока управления соответственно подключен к управляющему входу первого и второго электронного ключа, третий и четвертый выход -соответственно к входу счетчика старших и младших разрядов, пятый выход — к установочному входу счетчика, а шестой выход — к разрядному ключу интегратора, отличающийся тем, что, с целью повышения быстродействия, выход интегратора подключен к первому входу сумматора, второй вход которого соединен с входной, клеммой устройства, а выход подключен к первому входу компаратора, второй вход которого.подключен к первому входу дифференциального усилителя через дополнительный усатитель, и к второму входу непосредственно,а вход интегратора соединен с выходом дифференциального усилителя.

Источники информации; принятые во внимание при экспертизе

1, Авторское свидетельство СССР

Уо 209073, кл. Н 03 К 13/02, 13.06.66.

2. Патент CII1A М 3.493.963. ,кл. Н 03 К 13/20 (прототип).

729840

Составитель Ю. Богданов

Редактор Л. Гребеннихова Техред С. Мигай Корректор Ю. Макаренко

Заказ 1 32 7/5 4 Тираж 995 Подписно е

?1НИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4