Устройство для исправления ошибок

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республии

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ () ?29849 (61) Дополнительное к авт. свид-ву № 432677 (22)Заявлеио07. 12.78 (21) 2694081/18-21 с присоединением заявки № (23) Приоритет

Опубликовано 25 04 80. Бюллетень №15

Дата опубликования описания 28.04.80 (51)M. Кл.

Н 03 К 21/34

Н 03 К 13/32

Гее %арстееннъй комитет

СССР ао делам нэебретеннй и аткрытнй (53 ) УД К 62 1. 374..32(088.8) (72) Автор изобретения

В. H. Горшков (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК

Изобретение относится к технике связи и вычислительной технике и может использоваться в системах передачи и хранения и«е1юрмации, подверженных воздействию помех.

Иэ основного авт. св. ¹ 432677 известно устройство для исправления ошибок, содержащее счетчик повторений, выход которого соединен с входом коммутатора, а вход — с входами первого и второго сумматоров и управляющего ключа, другие входы которого соединены с выходами первого и второго сумматоров, регистра сдвига и коммутатора, а выход — с входом регистра сдвига, 15 сумматоры декодера, входы которых соединены с потенциальными выходами регистра сдвига, а выходы — с входами мажоритарного элемента, выход которого соединен с входом ключа, другой вход которого соединен с выходом коммутатора $1).

Декодирование кодовой комбийации в устройстве, происходит следующим образом: в начале принимается мажоритарное решение по нескольким повторениям информации, а затем производится дополнительное исправление ошибок.

Недостатком известного устройства является его низкое быстродействие.

Бель изобретения — повышение быстродействия устройства.

Это достигается тем, что в устройство для исправления ошибок, содержащее счетчик повторений, коммутатор, ключи, регистр сдвига, сумматоры, сумматоры декодера и мажоритарный элемент, введены дополнительный регистр сдвига, эключенный между входом второго клю«а и выходом мажоритарного элемента, счетчик ошибок н элемент сравнения, первый вход которого подключен к входной шине, второй вход — к выходу мажоритарного элемента, а выход через счетчик ошибок — к одному из входов коммутатора.

3 7298

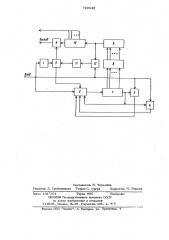

На чертеже представлена структурная электрическая схема устройства для исправления ошибок.

Устройство содержит счетчик 1 повторений, первый ключ 2, сумматоры 3 и 4, коммутатор 5, второй ключ 6, регистр 7 сдвига, сумматоры 8 декодера, . мажоритарный элемент 9, дополнительный регистр 10 сдвига, счетчик 11 ошибок, элемент 12 сравнения. 10

Устройство работает следуюшим образом, При приеме первой посылки сигнал с коммутатора 5 ставит первый ключ 2 в положение, при котором на вход ре- >5 гиетра 7 сдвига проходят принимаемые символы, при этом второй ключ 6 закрыт.

По окончании приема первой посылки сигнал со счетчика 1 повторений посту- 20 пает на коммутатор 5, последний ставит первый ключ 2 в положение, при котором на вход регистра 7 сдвига проходят сигналы с первого сумматора 3, работаюшего по правилу 1 + 1=1,0+О=0,1 + 0 = 2,0 + 1 = 2. Счетчик 11 ошибок устанавливается в нулевое состояние.

При приеме второй посылки одновремен но производится исправление ошибок в 30 первой посылке с помошью сумматоров 8 декодера и мажоритарного элемента 9, Каждый символ второй посылки в элементе 12 сравнения сравниваетсч с соответствующим символом скорректирован- 35 ной первой посылки, которая записывается в дополнительный регистр 10 сдвига, При несовпадении символов первой и второй посылки . элемент 12 сравнения выдает единичный сигнал, по ко- 40 торому счетчик 11 ошибок увеличивает свое состояние на единицу, B первом случае вторая и скорректированная первая посылки отличаются больше, чем на 1 (-максимальная 45 кратность ошибки, исправляемой корректирующим кодом)символов.

О наличии ошибок, кратности больше 9 свидетельствует состояние счетчика 11 ошибок. По окончании приема $0 второй посылки сигналы со счетчика 1 повторений и счетчика 11 ошибок поступают на коммутатор 5, ставяший первый ключ 2 в положение, при котором на вход регистра 7 сдвига проходят сигналы 55 с выхода второго сумматора 4, работаю49 4 щего по правилу: 1+1=1, 0+0=-О, 1+0=1, 0+1=0, 2+1=1,2+0=0, где первыми записаны символы, поступающие из регистра 7 сдвига. Одновременно с приемом третьей посылки производится исправление ошибок с помошью сумматоров 8 декодера и мажоритарного элемента 9 и запись исправленной кодовой комбинации и дополнительный регистр 10 сдвига.

По окончании приема третьей посылки сигнал со счетчика 1 повторений поступает на коммутатор 5, который открывает второй ключ 6 и исправленная кодовая комбинация выдается на выход устройства последовательным кодом. Кроме того, возможна выдача исправленной кодовой комбинации параллельным способом.

B другом случае вторая и скорректированная первая посылки отличаются не больше, чем на символов, либо совпадают, По окончании приема второй посылки сигналы со счетчика 1 повторений и счетчика 11 ошибок поступают на коммутатор 5, который открывает второй ключ 6 и исправленная первая посылка из дополнительного регистра 10 сдвига выдается на выход устройства.

Таким образом, устройство позволяет произвести декодирование кодовой комбинации после приема двух посылок, т.е. имеет повышенное быстродействие в случае, если кратность ошибок не больше допустимо й.

Формула изобретения

Устройство для исправления ошибок по авт. св. № 432677, о т л и ч а юш е е с я тем, что, с целью повышения быстродействия, в него введены дополнительный регистр сдвига, включенный между входом второго ключа и выходом мажоритарного элемента, счетчик ошибок и элемент сравнения, первый вход которого подключен к входной шине, второй вход — к выходу мажоритарного элемента, а выход через счетчик ошибок — к одному из входов комммутатора.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

М 432677, кл. Н 03 К 13/32, 1972.

729849

Составитель В. Чернышев

Редактор Л. Гребенникова Техред,С, Мигай . Корректор,М. Шароши

Заказ 1 327/54 Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская, наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная!