Устройство для управления встечно-параллельно включенными тиристорами

Иллюстрации

Показать всеРеферат

73Б23

ОЛИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 08.08.77 (21) 2514847/24-07 с присоединением заявки № (51) М. Кл з

Н 02 М 1/08

Н 03 К 17/72 (23) Приоритет

Государственный комитет

СССР (43) Опубликовано 30.04.80. Бюллетень № 16, (45) Дата опубликования описания 30.04.80 (53) УДК 621.316.727 (088.8) по делам изобретений и открытий (72) Авторы изобретения

В. Ф. Бобров и Л. Я. Новиков (71) Заявитель

° а (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВСТРЕЧНОПАРАЛЛЕЛЬНО ВКЛЮЧЕННЫМИ ТИРИСТОРАМИ фер.;-; .+

Изобретение относится к электротехнике и может быть использовано для управления тиристорами, коммутирующими трансформаторную нагрузку.

Известно устройство для управления тиристором (1), содержащее источник синхроимпульсов и формирователь, соединенные с входами логического элемента, выход которого подключен к первому входу клю-. чевого устройства, источник пульсирующего напряжения, первый выход которого соединен с входом формирователя, а второй выход —. с вторым входом ключевого устройства, соединенного с нагрузкой.

Данная схема имеет пониженную надежность при трансформаторной нагрузке изза наличия бросков тока в переходном процессе включения трансформатора.

Наиболее близким по технической сущности к предлагаемому является устройство для управления встречно-параллельно включенными тиристорами (2), содержащее формирователь — усилитель импульсов управления и блок магнитной памяти, обеспечивающий запоминание остаточного магнитного потока в сердечнике силового трансформатора.

К недостаткам устройства относится отсутствие синхронизации первоначального импульса запуска тиристора с напряжением сети, что приводит к броскам тока и ухудшает надежность работы трансформатора.

Цель изобретения — повышение надежно5 ети устройства.

Поставленная цель достигается тем, что устройство для управления встречно-параллельно включенными тиристорами, содержащее формирователь и усилитель импуль10 сов управления и блок магнитной памяти, снабжено блоком синхронизации с сетью, включенным на вход формирователя импульсов, а блок магнитной памяти выполнен в виде датчика тока, порогового эле15 мента, запоминающего и тактируемого

RS-триггеров с дополнительными информационным и тактируемым входами, вход. ного RS-триггера, формирователя задержанных импульсов и логического элемента

20 И вЂ”,ИЛИ. При этом выход датчика тока, включенного последовательно с тиристорами, через пороговый элемент подсоединен к

$-входу запоминающего триггера, R-вход которого, а также R-вход тактируемого

25 триггера подключены к прямому выходу входного RS-триггера, тактовый вход — к выходу блока синхронизации, информационный вход — к инверсному выходу тактируемого триггера, а прямой выход — к од30 ному из входов элементов И вЂ” ИЛИ, второй

731523

3 вход которого подсоединен к выходу формирователя импульсов, выход — к входу усилителя импульсов управления, а третий вход вместе с тактовым входом тактируемого триггера включен на выход формирователя задержанных импульсов, тактовый вход которого подсоединен к выходу блока синхронизации, а информационный вход вместе с информационным входом тактируемого триггера включен на инверсный выход входного RS-триггера.

Ъ

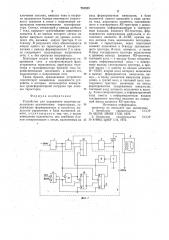

На фиг. 1 представлена принципиальная схема устройства для управлейия встречнопараллельно включенными тиристорами; на фиг. 2 — диаграммы, поясняющие принцип его работы.

Устройство содержит блок 1 синхронизации с сетью, соединенный с формирователем 2 импульсов управления, усилитель 3 импульсов, подключенный к управляющим переходам встречно-параллельно соединенных тиристоров 4, включенных последовательно с трансформаторной нагрузкой 5, блок б магнитной памяти, выполненный в виде датчика 7 тока, включенного в цепь тиристоров 4, порогового элемента 8, включенного между датчиком 7 тока и S-входом запоминающего RS-триггера 9, R-вход которого, а также Я-вход тактируемого

RS-триггера 10 подключен к прямому выходу входного RS-триггера 11, тактовый вход — к выходу блока 1 синхронизации, информационный вход — к инверсному выходу тактируемого триггера 10; а прямой выход — к одному из входов логического элемент И вЂ” ИЛИ 12. Последний включен между формирователем 2 и усилителем 3 и подключен также вместе с тактовым входом тактируемого триггера 10 к выходу формирователя 13 задержанных импульсов, тактовый вход которого подсоединен к выходу блока 1 синхронизации, а информационный вход вместе с информационным входом тактируемого триггера 10 включен на инверсный выход RS-триггера 11.

Принцип работы устройства поясняется диаграммами фиг. 2.

Синусоидальное. напряжение сети (фиг.

2,a), поступающее на блок 1 синхронизации, преобразуется в парафазные синхросигналы прямоугольной формы (фиг. 2, б, в), которые используются для запуска формирователя 2 импульсов и тактирования формирователя 13 задержанных импульсов и запоминающего триггера 9. Формирователь

2 импульсов выдает сигналы (фиг. 2,г) в начале каждого полупериода напряжения сети. Эти сигналы поступают на первый выход элемента И вЂ” ИЛИ 12. Формирователь 13 задержанных импульсов, тактируемый сигналами с одного из выходов блока

1 синхронизации, запускается при наличии на его информационном входе сигнала логического «О», поступающего с инверсного

4 выхода RS-триггера 11 при включении последнего.

В исходном состоянии, когда RS-триггер

11 выключен и-на его прямом выходе сигнал равен «О» (фиг. 2,д), на выходе формирователя (фиг. 2,е) сигнал равен логическому «О», на инверсном выходе тактируемого триггера 10 (фиг. 2,ж) — логической

«1», на, прямом выходе запоминающего . триггера 9 (фиг. 2,з) — логическому «О», на выходе элемента 12 (фиг. 2,и) — логическому «О» . При этом тиристоры 4 закрыты, на выходе датчика 7 тока (фиг. 2,к) сигнал отсутствует, на выходе порогового элемента 8 (фиг. 2,л) сигнал равен логической «1». На нагрузке 5 напряжения нет (фиг. 2,м).

При включении RS-триггера 11 на выходе формирователя 13 задержанных импульсов получаются импульсы (фиг. 2,е), сме-, щенные относительно отрицательного фронта синхросигналов (фиг. 2,б) к концу полупериода, но не выходящие за положительный фронт синхросигналов. Первый из этих импульсов, пройдя через элемент 12 и усилитель - 3, осуществляет предварительное включение одного из тиристоров 4 в конце соответствующего полупериода напряжения сети. Импульс тока в нагрузке оказывается при этом небольшим, так как подключение нагрузки к источнику питания происходит при пониженном напряжении. Однако его величина получается различной в зависимости от того, в какой фазе происходит предыдущее отключение питания нагрузки.

В тех случаях, когда фаза включения питания оказывается противоположной фазе предыдущего выключения питания, импульс тока в нагрузке будет минимальным в связи с изменением направления перемагничивания трансформатора и меньше некоторого (порогового) значения. Поэтому сигнал с выхода датчика 7 тока не сможет переключить пороговый элемент 8, и запоминающий триггер 9 не будет включен по S-входу.

Первый из импульсов, сформированный формирователем 13, обеспечивающий предварительное включение одного из .тиристоров 4, осуществляет также и включение по тактовому входу триггера 10 (отрицательным фронтом). Сигнал с инверсного выхода этого триггера разрешает запуск по тактовому входу запоминающего триггера

9, который переключается в состояние логической «1» синхросигналом с выхода блока 1 синхронизации, пропустив один полупериод напряжения сети. Сигнал с прямого выхода триггера 9 разрешает прохождение на выход элемента 12 сигналов с выхода формирователя 2, которые обеспечивают включение одного из тиристоров 4. в начале каждого полупериода напряжения сети.

В тех случаях, когда фаза включения питания совпадает с фазой предыдущего вы-73i523

Г !

1 !

1 !

1 (I

1 ключения питания, импульс тока в нагрузке оказывается больше некоторого (порогового) значения в связи с сохранением направления перемагничивания трансформатора. Сигнал, снимаемый с выхода датчика

7 тока, вызывает срабатывание порогового элемента 8, на выходе которого сигнал на время импульса падает до уровня логического «О», вызывая запуск триггера 9 по

S-входу. В результате этого обеспечивается запуск одного из тиристоров 4 синхросигналами с выхода формирователя 2 в начале следующего полупериода напряжения сети, т. е. без пропуска полупериода, Благодаря подаче на трансформатор на пряжения сети в соответствующей фазе, устраняется возможность перегрузки тиристора и трансформатора броском тока перемагничивания последнего в момент его подключения к напряжению сети.

Таким бразом, предлагаемое устройство способствует повышению надежности устройств, в которых используется коммутация трансформаторной нагрузки при помощи тиристоров.

Формула изобретения

l . Устройство для управления встречно-параллельно включенными тиристорами, содержащее формирователь и усилитель импульсов управления и блок магнитной памяти, отличающееся тем, что, с целью повышения надежности, оно снабжено блоком синхронизации с сетью, включенным на вход формирователя импульсов, а блок магнитной памяти выполнен в виде датчика тока, порогового элемента, запоминающего и тактируемого RS-триггеров с допол5 нительными информационным и тактируемым входами, входного RS-триггера, формирователя задержанных импульсов и логического элемента И вЂ И, причем выход датчика тока, включенного последова10 тельно с тиристорами, через пороговый элемент подключен к S-входу запоминающего триггера, R-вход которого, а также

R-вход тактируемого триггера подключены к прямому выходу входного RS-триггера, I5 тактовый вход — к выходу блока синхронизации, информационный вход — к инверсному выходу тактируемого триггера, а прямой выход — к одному из входов элемента

И вЂ И, второй вход которого подключен

20 к выходу формирователя импульсов, выход — к входу усилителя импульсов управления, а третий вход и тактовый вход тактируемого триггера включены на выход формирователя задержанных импульсов, 25 тактовый вход которого подключен к выходу блока синхронизации, а информационный вход вместе с информационным входом тактируемого триггера включен на инверсный выход входного RS-триггера.

30 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 422100, 2НОЗК 17/02, 1970.

2. Авторское свидетельство СССР

35 № 419862, 2g05F 1/14, 1972.

Редактор И. Грузова

Составитель В. Жмуров

Техред В. Серякова

Корректор Е. Осипова

Заказ 755/12 Изд. № 279 Тираж 798 . Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва; 7К-35, Раушская наб., д. 4/5

Типография, пр, Сапунова, 2