Элемент задержки потенциальных сигналов

Иллюстрации

Показать всеРеферат

(i ц 73I 568

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Саюа Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву 517151 (22) Заявлено 16.03.78 (21) 2589991/18-21 с присоединением заявки № (51) М. Кл.-

Н 03К 5/13

Н ОЗК 17/28

СССР по делам изобретений (53) УДК 621.374.5 (088.8) (43) Опубликовано 30.04.80. Бюллетень № 16 (45) Дата опубликования описания 30.04.80 и открытий (72) Авторы изобретения

В. М. Кабанов и С. А. Поволоцкий (71) Заявитель (54) ЭЛ EMEHT ЗАДЕРЖКИ ПОТЕНЦИАЛ ЬН ЫХ

СИГНАЛОВ

Изобретение относится к импульсной технике и может быть использовано в формирователях импульсов, в частности для формирования задержанных импульсных сигналов. 5

Известно устройство задержки потенциальных сигналов по авт, св. ¹ 517151, содержащее элемент И вЂ” НЕ транзисторнотранзисторной логики, к одному из входов которого подключена времязадающая диод- (О но-конденсаторная последовательная цепь, у которой анод диода, соединенный с конденсатором, подключен к эмиттерному входу логического расширения элемента.

Одним из недостатком данного элемента (5 задержки является увеличение сквозного тока (тока перекрытия) при переключении элемента из состояния логического «О» в состояние логическую «1». При этом ток питания устройства быстро растет, вызы- 20 вая значительный выброс тока и выброс напряжения в шине питания относительно земли. Резкие выоросы тока B цепи питания устройства в сочетании с выбросами напряжения значительно сокращают срок 25 службы устройства и могут наводить на проводники, расположенные вблизи шины питания, паразитные сигналы, вызывающие ложные срабатывания устройства, что значительно ухудшает надежность работы эле- ЗО мента задержки, Государственный комитет (23) Пр ор

Другим недостатком элемента задержки о является то, что он позволяст реализовать функцию задержки только при одной полярности входного сигнала прп условии, что длительность входного сигнала будет превышать длительность выходного сигнала на величину задержки.

Целью предлагаемого изобретения является повышение надежности устройстга за счет устранения тока перекрытия íà Bblxoде элемента задержки и р".ñøèðåíèñ функциональных возможностей устройства путем реализации третьего логического состояния элемента «выключено» для произвольных уровней входных сигналов и реализации режима одновременной задержки и расширения входных импульсов.

Поставленная цель достигается тем, что в элементе задержки. содержащем элемент

И вЂ” -HF. транзисторно-транзисторной логики, к одному пз входов которого подключена времязадаюгцая диодно-конденсаторная последовательная цепь, у которой анод диода, соедипеппьш с конденсатором, подключен и эмиттерному входу логического расширения элемента И вЂ” НЕ, введены дополнительная времязадающая диодно-конденсаторная последовательная цепь и переменный резистор, подключенный параллельно конденсатору дополнительной времязадающей цепи, а анод диода дополнительной цепи соединен с коллекторным входом логического расширения элемента И вЂ” НЕ.

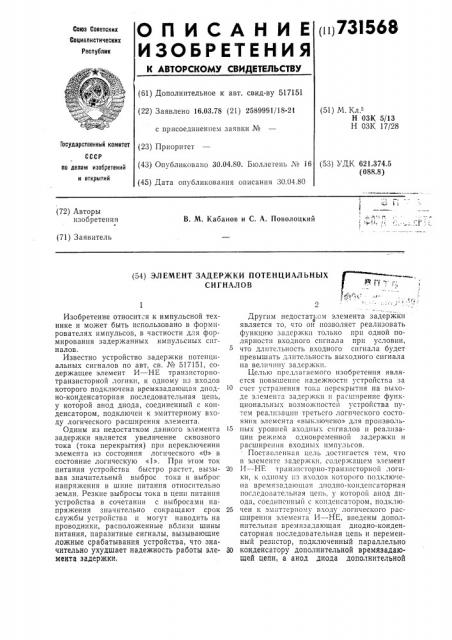

На чертеже приведена принципиальная схема элемента задержки потенциальных сигналов.

Элемент задержки состоит из элемента

И вЂ” НЕ 1 транзисторно-транзисторной логики (очерченного пунктирной линией на чертеже), содержащего транзисторы 2, 3, 4, 5, резисторы б, 7, 8, 9, диод 10 и имеющего эмиттерный (Э) и коллекторный (К) выводы логического расширения, времязадающие конденсаторы 11, 12, диоды 13, 14 и пер ем ен н ы и р ези стор 15.

Элемент работает следующим образом.

B исходном состоянии вход 1б логического элемента 1 имеет низкий потенциал, а выход 17 — высока! потенциал, что соответствует состоянию логической «1». 11ри подаче положите !ы!Ого перепада напряжения на вход 1б логического элемента l открывается транзистор 2, который затем открывает транзистор 3. Начинается заряд конденсатора 11 через резистор 7 и открытый транзистор 3. Прн этом на выходе 17 логического элемента 1 формируется третье логическое сОстОя, 11не «Вык.Iю«1сно>>, та» как базовые выводы транзпсторов 5 и 4 шунтпрованы конденсатором 11 и оба эти транзисторы находятся одноврсмспно в закрытом состоянии.

После заряда конденсатора 11 до потенциала отпирания транзистора 5, последний открывается, а транзистор 4 остается в закрытом состоянии. На,выходе 1i элемента

1 формируется Отрицатсльны Псрепад напряженияя, соответствующий состоянию лог. «0». При подаче отрицательного перепада напряжения на вход элемспта 1 происходит разряд конденсатора 11 через открытый диод 13, резистор 9 и базо-эмиттерный переход транзистора 5. При этом до окончания разряда конденсатора 11 транзистор 5 остается в открытом состо!шии.

При отсутствии дополнительно введенной времязадающей диодно-конденсаторной цепи (диод 14, конденсатор 12, резистор 15) одновременно с разрядом конденсатора 11 закрывались транзисторы 2 и 3 и открывался транзистор 4. Прп этом через последовательно включенные и одноьременно открытые транзисторы 4 и 5 будет протекать скзозной ток (ток перекрытия), уменьшающий надежность устройства.

ДЛЯ I!Pe!IOrrIPa!IIeHII: PeII

14. Так как время заряда конденсатора 12

1О

ЗО

60 значительно больше времени разряда конденсатора 11, то транзистор 5 закрывается при закрытии транзистора 4. С этого момента элемент задержки вторично находится в третьем логическом состоянии «выключено», которое соответствует новой полярности входного сигнала. Это состояние сохраняется до момента заряда конденсатора

1 до потенциала отпирания транзистора 4.

При этом на выходе 17 элемента формируется уровень напряженйя, соответствующий логической «1».

Переменный резистор 15 служит для плавного регулирования продолжительности логического состояния «выключено»для обо:Ix полярностей входных сигналов и в качестве цепи разряда для конденсатора 12.

Таким образом, суммарная задержка элемента возрастает на время логического состояния «выключено». Регулируя длительность входных сигналов, на выходе логического элемента можно формировать: только логическое состояние «выключено», задержанные импульсы с длительностью, меньшей длительности входных импульсов, задержанные импульсы с длительностью, большей длительности входных импульсов.

При расширении импульсов время первого состояния «выключено» используется в качестве задержки элемента, а время второго состояния «выключено» используется в качестве приращения расширяемого импульса. Таким образом после окончания входного сигнала, изменения на выходе элемента произойдут спустя время на состоянке «выключено». Варьируя длительностями входных импульсов и значениями номиналов времязадающих конденсаторов, можпо получать элемент задержки с различными функциональными возможностями.

; страненпе токов перекрытия повышает надежность устройства, а расширение фупкциональных возможностей делает элемент задержки более универсальным, что позволяет расширить область его использования.

Формула изобретения

Элемент задержки потенциальных сигналов 110 авт. свид. № 517151, отличающи и ся тем, что, с целью повышения надежности и расширения функциональных

Возможностеи, в него введены дополнительная врсмязадающая диодно-конденсаторная последовательная цепь и переменный резистор, подключенный параллельно конденсатору дополнительной времязадающей цепи, а анод диода дополнительной цепи соединен с коллекторным входом логи !еского расширения элемента И вЂ” НЕ, 731568

Составитель И. Редько

Техред В. Серикова

Корректор Л. Тарасова

Редактор Е. Караулова

Типография, пр. Сапунова, 2

Заказ 545/13 Изд. Хе 282 Тираж 995 11одписное

НПО «Поиск» Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5