Распределитель импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАН И Е(11731592

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕ ЕЛЬС ВУ (61) Дополнительное к авт. свид-ву (22) За51влеио 01.02.78 (21) 2575016,18-21 (51) М. Кл.-

Н ОЗК 17, 62 с присоединением заявки J¹

Государстве(IIIII комитет (23) Приоритет (43) Опубликовано 30.04.80. Бюллетень № !6 (45) Дата опублико Iàïè51 описания 30.0-1.80 (53) УДК 621.382 (088.8) ло делам изобретений н откр(нтий (72) Авторы изобретения

В. А. Исае:I o, В. А. 1халиничев и В. M. Тафель (71) Заявитель (54) РАСПРЕДЕЛИТЕЛЬ 14ИП(УЛЬСОВ

Изобретение относится к вычислите.(шгои технике и предназначено для полу lcllll51 сигналов, разиссснных во времени и пространстве.

Известен распределитель, IIOci13ocli III III ив кольцевом сдвиговом реп(стре с перекрестными связями (счетчик Д консона) 111.

Недостатком распределителя является переход в нерабочее состо" íèå ири соос, кроме того, иа выходах дешифратора уровней возможно появление ложных сигналов.

Известен распределитель сигналов, содержащий счетчик и дешифратор, выход младшего разряда счетчика соединен с входом младшего разряда дешифратора, выходы старших разрядов сосд1щены с входами старших разрядов дсшифрагора 121.

Недостатком этого распределителя является наличие на выходных дешифратора ложных сигналов при переходе счетчика в другое состояние.

С целью устранеш(я ложных с (гиалов на выходах дешифратора в распределитель, содержащий счстчик и дешифратор, выход младшего разряда счетчика соединен с входом младшего разряда дсшифратора, выходы старших разрядов с(етчика соединены с первой группой входов старинки разрядов дсшифратора, ввсдсп регистр памяти, динамический вход записи которого соедиlIc с выходом младшего разряда счетчика, «ыхолы старших разрядов которого подкл(о(спы к информационным в. одам реги.тра иамчт.l, coc;Iilllc(ного выходами с второй группой ((ходов ст(I(11iillx разрядов дешифратора.

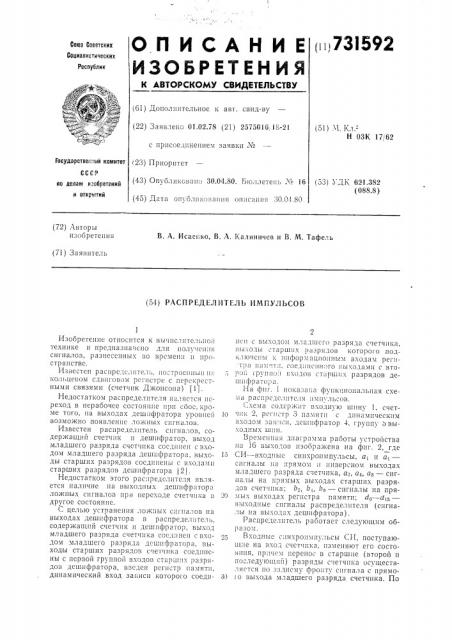

На фиг. 1 показана функциональная схема распределителя имп.,и,co«.

i.хема содержит входную шину 1, счет11 1ик 2, реп(стр 3 памяти с динамическим

«ходом заи.(си, дешифратор 4, группу 6Bblкодных шии.

Временная диаграмма раооты устройства

i1a 16 выходов изображена на фиг. 2, где

Б СИ вЂ” входные сиихроимпульсы, а, и а(— сигна.(ы иа прямом и инверсном выходах младшего разряда счетчика, а, а(, ав — сигналы на прямых выходах старших разрядов счетчика; (3g, (13, 6в — сигна lbl на пря20 мых. выхоДах РегистРа памЯти; dp — а(в—

«ыходныс cIII EIB;Ibl распределителя (сигналы иа выходаx. дешифратора).

Распределитель работает следу(ощим образом.

Вход ые c:1нхроимпульсы СИ, поступаюill. (е на вход счет шка. изменяют cl0 состояния, пр:гнем перенос в старшие (второй п последующий) разряды счетчика осуществляется Iio заднему фронту сигпа1а с прямозо .о выхода младшего разряда счетчика. По

731592

7 аг

Бг а„ бб — б ав

Бв

dî бгбб=а, Бг.Б 7 БВ

d, а, аг а4 а

7 б72

5бв

dг=аб.Б2 Б б. ТВ б7з=аб аг.p бб ав о = Бг Б Бв ав=аб.аг а а

PZ7z. 7

Поппббспое т р;;к- 09З

Изго ¹ 351

Заказ !202/6

Тппогвафбббп Ilj). Сап пбоаа, 2 заднему фронту сигнала с выхода младшего разряда счетчика производится запись текущего состояния старших разрядов счетчика в регистр памяти, благодаря чему состояния регистра памяти пов-.оряют состояния старших разрядов счетчика с задержкой на один такт входных синхроимпульсов.

На выходы дешифратора, выдсля7о7цис четные выходные сигналы (dp, dz, d.

dIp, dIg, dI4), 1IocTyIIaIoz сигна tIhI c инверсногоо выхода младшего разряда счетчика и с выходов регистра памяти. На входы дсшифратора, выделяющие печстпыс выходные импульсы (бб1 5 3, бб5 ".> 7 " ба!5) ступают сигналы с прямого выхода младшего разряда счетчика и с выходов старших разрядов счетчика. Благодаря этому переходные процессы для каждой пз двух групп дсшифратора (четной и нечетной) происходят в паузах между разрсшсппымп состояниями младшего разряда счетчика, вследствие чего появление на выходах устройства ложных сигналов исключено.

Формула изобретения

Распределитель импульсов, содержащий счетчик и дешифратор, выход младшего разряда счетчика соединен с входом младшего разряда дешифратора, выходы старших разрядов счетчика соединены с первой группой входов старших разрядов дешифратора, отличающийся тем, что, с целью устранения логкных сигналов на выходах дешифратора, в него введен регистр памяти, динамический вход записи которого соединен с выходом младшего разряда счетчика, выходы старших разрядов которого подключены к информационным входам pclilcTpd памяти, соединенного входами с второй группой входов старших разрядов дешифратора.

Источники информации, принятые во внимание при экспертизе

1. Лвторское свидетельство № 356768, кл. Н ОЗК 17бб62, 1972.

2. Букреев И. Н. и др. Микроэлектронные схемы цифровых устройств. М., 1975, с. 276, 2о рис. 6 — 11 (прототпп). си! ! ! ! 1 ! ! ! I ! ! ! !

77Ч

5 а Ьг Б4 б7в в а, агав ав

07 а bz Ббб бв в

= аб аг ав ав

bzБ4 b 7а

=а7 аг а ав

71, = d bz а4 be

72

=а7 аг а4 ав

7J g bä b

1бб а< .7г.а а

1В