Устройство тактовой синхронизации с пропорциональным регулированием

Иллюстрации

Показать всеРеферат

ОПИСАН И Е

И ЗО БР Е 1 Е Н И Я

1н1 73) 604

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву 314320 (22) Заявлено 22.09.78 (21) 2669572/! 8-09 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.04.80. Бюллетень № 16 (45) Дата опубликования описания 30.04,80 (51) М. Кл.

Н 04L 7/02

Государственный номнтет

СССР па делам изобретений н открытнй (53) УДК 621.394.662. .2 (088.8) (72) Автор изобретения

В. П. Ореханов (71) Заявитель (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

С ПРОПОРЦИОНАЛЬНЫМ РЕГУЛИРОВАНИЕМ

Изобретение относится к технике связи и может быть использовано в устройствах автоматической подстройки частоты.

По основному авт. св. № 314320 известно устройство тактовой синхронизации с пропорциональным регулированием при коэффициенте усреднения 2к, содержащее задающий генератор, делитель частоты, узел управления коэффициентом деления, фазо вый дискриминатор и узел выделения фрон- 1о тов, делитель частоты выполнен с дополнительным числом К разрядов, при этом выход К-го разряда делителя частоты подключен к входу фазового дискриминатора 11). 15

Однако такое устройство имеет невысокую помехоустойчивость.

Цель изобретения — повышение помехоустойчивости.

Для этого в устройство тактовой синхро- 20 низации с пропорциональным регулированием при коэффициенте усреднения 2", содержащее задающий генератор, делитель частоты, узел управления коэффициентом деления, фазовый дискриминатор и узел 25 выделения фронтов, делитель частоты выполнен с дополнительным числом К разрядов, при этом выход К-го разряда делителя частоты подключен к входу фазового дискриминатора, введен временной селектор 30 входных сигналов, выход которого подключен к узлу выделения фронтов, а вход соединен с выходом задающего генератора, временной селектор входных сигналов выполнен в виде двух цепей, каждая из которых состоит из последовательно соединенных элементов И, счетчика н дешифратора, выход которого через инвертор подкл|очеп к входу элемента И, выходы дешпфраторов обоих цепей подключены к входу триггера, причем второй вход элемента Й второй цепи соединен с выходом ннвертора, вход которого соединен с вторым входом элемента И первой цепи, причем второй вход элемента И первой цепи, третьи входы элементов И и третий вход триггера, а также выход триггера являются соответственно входамп и выходом временного селектора входных сигналов.

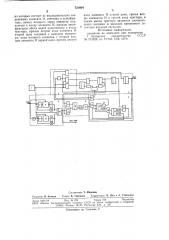

На чертеже дана структурная электрическая схема предложенного устройства.

Устройство содержит задающий генератор 1, делитель 2 частоты, узел 3 управления коэффициентом деления, фазовьш дискриминатор 4, узел 5 выделения фронтов и временной селектор 6 входных сигналов, который состоит нз элементов И 7, 8, счетчиков 9, 10, дешнфраторов 11, 12, пнверторов 13 — 15 и триггера 16.

731604

3

Устройство работает следующим образом.

Импульсы с задающего генератора 1 с периодом повторения 6 поступают на делитель 2 с коэффициентом 2 " +". На выходе делителя 2 вырабатывается последовательность стробирующих импульсов с периодом

Т (Т вЂ” длительность элементарной посылки принимаемого сигнала), синфазная с фронтами принимаемого сигнала. Входной сигнал поступает в временной селектор 6, где производится оценка входного сигнала по длительности. В качестве временных меток используются импульсы задающего генератора 1. Емкости счетчиков 9, 10 и число, на которое собраны дешифраторы

11, 12, определяются исходя из максимального значения длительности помехи. В отсутствие сигнала на входе счетчик 9 стоит в исходном состоянии, а со счетчика 10 снят сигнал «сброс». При появлении на входе элемента И 7 импульсных посылок со счетчика 9 снимается сигнал «сброс», а счетчик 10 устанавливается в исходное состояние. Счетчиком 9 производится подсчет импульсов задающего генератора 1 за время действия сигнала на входе, и, если этот сигнал по длительности превышает значение, установленное на счетчике 9, то на выходе дешифратора 11 появляется сигнал

«1», который поступает на вход 1 триггера

16 и через инвертор 13 запирает вход элемента И 7, при этом импульсом с задающего генератора 1 производится запись «1» г триггере 16. При снятии сигнала на входе включается счетчик 10, а счетчик 9 устанавливается в исходное состояние, на выходе дешифратора 12 появляется сигнал «0», который поступает на вход К триггера 16 и через инвертор 14 запирает вход элемента

И 8, при этом производится запись «0» в триггере 16. Выход триггера 16 является выходом принимаемой информации. С выхода триггера 16 информация поступает в узел 5. В узле 5 формируются передние и задние фронты посылок принимаемого сигнала и подаются на фазовый дискриминатор 4, в котором сравнивается момент прихода импульса фронта:t! с узла 5 и момент прихода импульса с выхода делителя 2 (t2).

На выходе фазового дискриминатора 4 вырабатывается пачка из 1 2 г — - к

î o-2 импульсов, которые поступают на узел 3, При этом происходит добавление f импульсов на вход делителя 2. Кроме того, с линии задержки фазового дискриминатора 4 на вход узла 3 поступает с приходом каждого фронта сигнал, вызывающий как бы исключение 2" — импульсов на входе делителя 2. Таким образом, в режиме синхронизма на выходе фазового дискриминатора 4 вырабатывается 2" — импульсов до5

ЗО

4 бавления, смещающих стробирующий импульс на время 2" — б. На эту же величину происходит сдвиг стробирующего импульса вследствие исключения одного импульса на входе (и — 1)-го разряда делителя 2.

Импульс с выхода К-го разряда делителя 2 переписывает информацию с триггера

16 через элементы И 17 и 18 в триггер 19.

Сигнал с триггера 19 непосредственно и через линию задержки 20 поступает на два входа полусумматора 21, на выходе которого образуется импульс фронта длительноЬ стью —, поступающий на фазовый дискри2 минатор 4.

Импульс с узла 5 поступает на триггер

22 через элемент И 23, в результате чего с выхода триггера 22 через линию задержки 24 подается разрешающий потенциал на элемент И 25.

Элемент И 25 запирается при поступлении на триггер 22 стробирующего импульса с выхода делителя 2. При отсутствии рассогласования стробирующий импульс расположен в середине принятой элементарной посылки. На элемент И 25 поступают с делителя 2 импульсы длительностью б и с периодом повторения 6.2к. На выходе элемента И 2о появляется пачка из тр !!.2 импульсов, где Тр — интервал времени между импульсом фронта и следующим за ним стробирующим импульсом. Импульс фронта с элемента И 23 поступает через элемент И 26 на установку триггера 27. На время Тр элемент И 26 блокируется подаваемым на него через линию задержки 28 потенциалом с триггера 22. Сигнал с триггера 27 через линию задержки 29 воздействует на узел 3, а через линию задержки

30 открывает элемент И 31. В результате этого очередной импульс с выхода (и — 1) -го разряда делителя 2 поступает не на и-й разряд, а на сброс триггера 27.

Импульсы добавления с выхода элемента И 25 подаются на вход узла 3.

Высокая помехоустойчивость устройства достигается за счет введения временного селектора 6, позволяющего предварительно контролировать входные сигналы по длительности.

Формула изобретения

1. Устройство тактовой синхронизации с пропорциональным регулированием по авт. св. № 314320, отл ич а ющееся тем, что, с целью повышения помехоустойчивости, введен временной селектор входных сигналов, выход которого подключен к узлу выделения фронтов, а вход соединен с выходом задающего генератора.

2. Устройство по п. 1, отличающееся тем, что временной селектор входных сигналов выполнен в виде двух цепей, каждая

731604

Составитель T. Маркина

Редактор Н. Коляда Техред В. Серякова Корректоры: В. Дод и А. Степанова

Заказ 1001/19 Изд. ¹ 276 Тираж 729 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 из которых состоит из последовательно соединенных элемента И, счетчика и дешифратора, выход которого через инвертор подключен к входу элемента И, выходы дешифраторов обоих цепей подключены к входу триггера, причем второй вход элемента И второй цепи соединен с выходом инвертора, вход которого соединен с вторым входом элемента И первой цепи, причем второй вход элемента И первой цепи, третьи входы элементов И и третий вход триггера, а также выход триггера являются соответственно входами и выходом временного селектора входных сигналов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 314320, кл. Н 041 7/02, 1970.