Преобразователь позиционного кода в код с большим основанием

Иллюстрации

Показать всеРеферат

О П И С А Н И Е <,„Va SS

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советск ин

Социалистические

Республик (61) Дополнительное к авт. свид-ву— (22)Заивлено 18.07.77 (21) 2508755/18 24 (51)М. КЛ. с присоединением заявки ¹G 06 F 5/02

Гоеудерственный комитет (2;3! Приоритет—

Опубликовано 05.05.80, Бюллетень №17 нв лелем изобретений н открытий (Ы) УЙК681 325 (088.8 ) Дата опубликования описания 08.05.80 (72) Авторы изобретения

О. В. Викторов, А. М. Романкевич и Т. Е. Файдова

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (7I) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ПОЗИИИОННОГО КОДА В КОД

С БОЛЬШИМ ОСНОВАНИЕМ

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении преобразователей позиционных кодов с одним произвольным основанием в коды с любым другим большим основанием, 5

Известен преобразователь двоичного кода в код с любым другим основанием, содержаший пирамидальные сумматоры значений всех разрядов числа с новым осно10 ванием, при этом число разрядов первого сумматора, на котором выделяется младший разряд числа с новым основанием, равно разрядности преобразуемого двоичного числа 111, Недостатком этого преобразователя являются большие аппаратные затраты. . Наиболее близким по технической сушности и схемному решению является преобразователь кода в код с большим основанием, содержаший регистр, двухразрядный вычитатель, блок управления, блок умножения на константу, вход которого coeAsses с выходом К-ого разряда регистра

2 (где К вЂ” число разрядов преобразуемого кода) и с первым входом двухразрядного вычитателя, второй вход которого соединен с выходом (К-1)-ого разряда регист ра, выходы блока умножения на константу соединены соответственно с третьим и четвертым входами двухразрядного вычитателя. Кроме того, преобразователь . содержит группу элементов И для сдвига кода в регистре (2).

Недостатком преобразователя является относительно низкое быстродействие, В нем преобразование К-разрядного .числа осушествляется за 2 К (К-2) + 1 тактов, Иель изобретения - увеличение скорости преобразования.

Это достигается тем, что преобразователь содержит первый, второй, третий и четвертый элементы И, первый и второй элементы ИЛИ, выходы которых соединены соответственно с входами К-ого и первого разрядов регистра, первые входы элементов ИЛИ соединены соответственно с выходами первого и второго элементов

7328

И, в вторые входы - с выходами третьего и четвертого элементов И соответственно, выходы старшего и младшего разрядов двухрвзрядного вычитателя соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены с первым выходом блока управления, выходы К-oro u (К-1)-oro разрядов регистра соединены соответственно с первыми входами третье-1О го и четвертого элементов И, вторые входы которых соединены с вторым выходом блока управления.

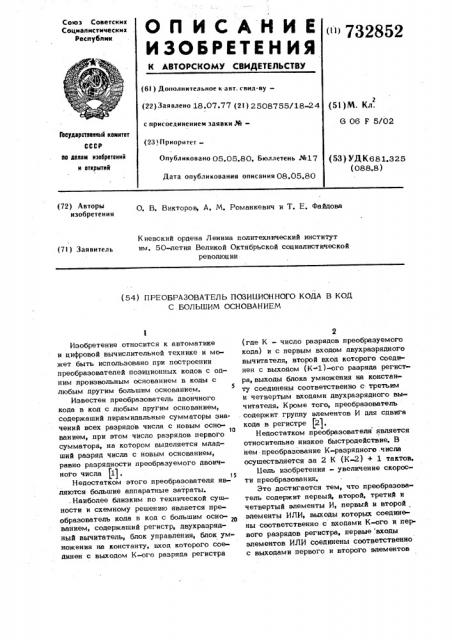

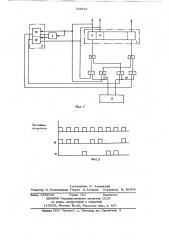

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг, 2 — диаграммы управляющих сигналов, вырабатываемые блоком управления устройства при преобразовании четырехрвзрядных кодов.

Преобразователь кода содержит К-разрядный R-ичный регистр 1, где основание системы счисления, в которую переводится код, двухрвзрядный вычитатель 2, блок 3 умножения на константу четыре элемента И 4, 5, 6, 7, блок 8 ,правления, Выход старшего (К-ого) рвз25 ряда 9 регистра 1 соединен с входами блока 3 умножения нв константу и младшим разрядом 10 вычитвтеля 2. Выход (К-1)-ого разряда 11 регистра 1 подключен к второму входу 12 вычитателя 2, Выход старшего разряда 10 вычитателя

2 через первый элемент И 4 и элемент

ИЛИ 13 связан с входом младшего разряда регистра. Выход младшего разряда

12 вычитвтеля через второй элемент И 5 и элемент ИЛИ 14 объединен с входом первого старшего разряда 9 регистра 1.

Выход разряда 9 через третий элемент

И 6 подключен к младшему разряду ре40 гистрв. Выход разряда 11 соединен че.рез четвертый элемент И 7 с разрядом 9 регистра 1. Блок 8 управления связан по шине 15 с элементами 6, 7, в по шине

16 с элементами 5, 4.

Работа преобразователя рассматривает ся на примере преобразования К вЂ” разрядных кодов при К = 4.

Все схемы, входящие в состав устройства, предназначены для работы с кодами чисел в системе счисления с тем основанием, с которым необходмо получить результат; К вЂ” разрядный код целого числа, которое необходимо преобразовать, помешают в регистр 1. Код цифры, хранящейся в разряде 9 регистра 1, поступает нв блок 3, где происходит умножение на константу, равную разности основвник систем счисления. На вычитвтеле 2 из

Нв четвертом такте на элементы И 6, 7 из блока 8 управления по шине 1 5 поступает разрешающий сигнал, в результате чего происходит сдвиг содержимого регистра 1 на один разряд влево, при этом код, хранящийся в старшем разряде 9 регистра 1, переписывается в младший разряд, а код, хранящийся в разряде 11, записывается в разряд 9 регистра 1, Нв пятом и шестом тактах из блоха

8 поступает по шине 15 управляющий сигнал нв элементы И 6, 7, в на седьмом и восьмом тактах управляющий сигнал по шине 16 посрпвет на элементы И 4., 5.

На (К-1) -ом такте в регистре 1 получается код числа с новым основанием системы счисления.

Ллгоритм преобразования построен таким образом, что нв каждых К шагах (на.чиная с первого) последовательно обрабатываются К-1, К-2 и т.д. разрядов преобразуем ого ч испа. П осл едующие К -(К-1 ), К-(К-2) и т.д. разряды промежуточного результата преобразования остаются без из м енен ия.

Пример, Перевести

<6612>п — (х>

10-7=3

6 3=18 66 12

8124 запись со сдвигом

8124

8х3=24 запись со сдвигом

7" 3=2 1,запись со сдвигом

0 сдвиг

4551 4551

12,4 3= 12,запись со сдвигом

52

4 двух старших разрядов кода числа, поступающих на регистр 1, вычитается код числа, поступающий с выходов блока 3.

На первых трех тактах из блока 8 по шине 16 на элементы И 4, 5 подается разрешающий потенциал, вследствие чего код разности с выхода вычитвтеля 2 записывается в регистр 1 таким образом, что содержимое старшего разряда 10 вычитателя 2 записывается в младший разряд регистра 1, в содержимое разряда 12 вычитвтеля 2 записывается в старший разряд регистра 1.

3513

Зх3 = 9 3513

732852 6 тип переводит за 241 такт, а предлагаемый преобразователь за 121 такт. запись со сдвигом

6132

«6132

0 сдвиг

1326

1326

1о сдвиг запись со сдвигом

3261

3261

09

2361

На временной диаграмме управляющих сигналов (фиг, 2), которые формируются блоком 8 управления, показано, что на первых четырех тактах (К=4) коды разрядов поступают на двухразрядный вычи- 2О татель 2 и блок умножения 3 (т.е. осуществляются арифметические .операции над кодами разрядов) только на первых трех тактах и четырех, управляющие сигналы с блока управления 8 на этих тактах? поступают на тактовую шину 16. На следующем такте (четвертом) управляющий сигнал поступает на шину 15, т.е. осуществляется только сдвиг промежуточного результата перевода без арифметической зо обработки разрядов. На следующих четырех тактах (5-8) сигналы с блока уцравления на шину 15 поступают уже дважды (на 7 и 8 тактах), т.е. осуществляется два сдвига без арифметической обработки з и т.д. Следовательно, количество "повторных сдвигов определяется алгоритмом перевода и равно 1 (где 1 — номер ц икла перевода) .

Предлагаемый преобразователь облада- 4о ет более высоким быстродействием по сравнению с известными устройствами. Он осуществляет перевод К-разрядного числа за (К-1) тактов, в то время как из2 вестное устройство переводит К-разряд- 45 ное число за 2К (К-2)+1 тактов. Например, 12-разрядный код устройство-протоФ о р м у л а и з о б р е т е н и я

Преобразователь позиционного кода в код с большим основанием, содержащий регистр, двухразрядный вычитатель, блок управления, блок умножения на константу, вход которого соединен с выходом

К-oro разряда регистра (где К - число разрядов преобразуемого кода) и с первым входом двухразрядного вычитателя, второй вход которого соединен с выходом (К-1)-ого разряда регистра, выходы блока умножения на константу соединены соответственно с третьим и четвертым входами двухразрядного вычитателя, о т л и- ч а ю ш и и с я тем, что, с целью уве- . личения скорости преобразования, oí co= . держит первый„ второй, третий и четвертый элементы И, первый и второй элементы ИЛИ„выходы которых соединены соответственно с входами К-ого и первого разрядов регистра, первые входы элементов ИЛИ соединены соответственно с выходами первого и второго элементов И, а вторые входы — с выходами третьего и четвертого элементов И соответственно,. выходы старшего н младшего разрядов двухразрядного вычитателя соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены с первым входом блока управления, выходы К-ого и (К-1)-ого разрядов регистра соединены соответственно с первыми входами третьего и четвертого элементов И, вторые входы которых соединены с вторым выходом блока управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N 315176, кл. G 06 F 5/02, 1970, 2, Авторское свидетельство СССР

No. 485444, кл. G 06 Г 5/02, 1974.

732852

/акмоле и глупьСы

Составитель М. Аршавский

Редактор О. Колесникова Техред И. Асталош Корректор В. Еут«а

Заказ 1554/10 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва. Ж--35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул, Проектная, 4