Преобразователь двоичного кода в двоично-десятичный и обратно

Иллюстрации

Показать всеРеферат

ОП ИСАКИИ и зоы рте н и я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсник

Социалистические

Республик

<" 732853 (61) Дополнительное к авт. свид-ву (22) Заявлено 03.10.77 (21)2529950/18 24 (51)М. Кл. с присоединением заявки .%G 06 F 5/02

Государственный комитет (23) Приоритет оо делам изобретений и открытий (53) УД К 681.325 (088.8) Опубликовано 05 05.80. Бюллетень Ле 17

Дата опубликования описания 08.05.80 (72) Авторы изобретения

А. В, Степанов и A. М. Горбань (71) Заявитель (54) ПРЕОБРАЗСВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНОДЕСЯТИЧНЫЙ И ОБРАТНО

Изобретение относится к цифровой вычислительной технике и может быль использовано при построении двоично-десятичных преобразователей кодов.

Известен преобразователь двоичного кода в двоично-десятичный и обратно, содержащий регистр двоичного числа, регистр двоично-десятичного числа, формирователь эквивалентов, переключатель эквивалентов, одноразрядный сумматор и блок управления (1).

Недостатком известного преобразователя является низкое быстродействие, что связано с последовательным принципом обработки значений разрядов.

Наиболее близким по технической сущности и схемному решению является преобразователь двоичного кода в двоичноЭ десятичный и двоично-десятичного кода в двоичный, содержащий двоичный регистр, регистр двоично-десятичных чисел, блок двоично-.десятичных эквивалентов, распределитель импульсов, генератор импульсов, первую, вторую и третью группы элементов И, первые входы которых соединены с группой выходов, распределителя импульсов, вторые входы первой группы элементов И соединены с выходами двоичного регистра, а выходы первой группы элементов И соединены с выходами третьей группы элементов И и со входами блока двт ично-десятичных эквивалентов, выходы второй группы элементов И соединены со входами двоичного регистра, выход генератора импульсов соединен со входом распределителя импульсов, выход которого соединен с первым входом генератора импульсов j2).

Кроме того, известный преобразователь содержит многовходовой реверсивный дво ично-десятичный счетчик, делитель частоты, триггер знака результата, Недостатком этого преобразователя является относительно низкая скорость преобразования, связанная с тем, что на суммирование или вычитание двоично-десятичного эквивалента поступает девять тактов, 732853

lIemü изобретения — увеличение скорости преобразования.

Это достигается за счет того, что преобразователь содержит двоично-десятичный сумматор, схему сравнения, четвертую группу элементов И, элемент ИЛИ, первый и второй элементы И, элемент НЕ, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И и вторыми входами всех элементов И второй группы, выход элемента ИЛИ соединен с первыми входами всех элементов И четвертой группы, вторые входы-которых соединены с выходами двоично-десятичного сумматора, подключенными к первой группе входов схемы сравнения, выходы элементов И четвертой группы соединены с входами регистра двоично-десятичных чисел, выходы которого соединены с первыми входами двоично-десятичного сумматора, вторые входы которого соединены с выходами блока двоично-десятичных эквивалентов, первый и второй выходы схемы срав25 пения соответственно соединены с первыми входами первого и второго элементов

И, вторые входы которых соединены с входом элемента НЕ и со вторыми входами всех элементов И четвертой группы, 30 выход второго элемента И соединен со вторым входом генератора импульсов, вторая группа входов схемы сравнения соединена со входами преобразователя.

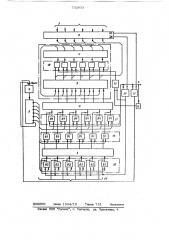

На чертеже изображена функциональная схема устройства.

Устройство преобразования разрядного двоичного числа в двоично-десятичное и обратно содержит двоичный регистр 1, блок 2 двоично- десятичных эквивалентов„ двоично-десятичный сумматор 3, регистр . 4 двоично-десятичных чисел, распределитель 5 импульсов, схему 6 сравнения, шины 7 двоично-десятичного числа, управляющую шину. 8, генератор 9 импульсов, первый и второй элементы И 10 и 11, элемент ИЛИ 12, элемент HE 13, шины

14 двоичного числа, первую, вторую, третью и четвертую группы элементов И 1518.

Выходы распределителя подключены на группы элементов И 15 и 17, на вторые входы которых подключены выходы разрядов двоичного регистра 1. Выходы элементов И из групп 15 и 17 подключены на входы блока 2 двоично-десятичных эквивалентов, выходы которого подключены на входы двоично-десятичного сумматора

3. Выходы сумматора подключены через вен-ипи группы элементов И 18 на входы сумматора, Выходы сумматора подключены также на входы схемы сравнения 6, на вторые входы которой подключены шины 7 двоично-десятичного числа, Выходы распределителя импульсов подключены также на входы элементов И 16 второй группы, на вторые входы которых подключен элемент И 10, выход сигчала " больше, равно схемы сравнения, Выход сигнала равенства схемы сравнения 6 через второй элемент И 11 подключен на вход сброс» генератора импульсов 9. Выход элемента

И 10 через элемен- ИЛИ 12 подключен не входы вентилей элементов И 18 четвертой группы. На элемент ИЛИ 12 поступает также сигнал с выхода элемента

HE 13.

Устройство рабстает следующим о6разом, В режиме преобразования двоичного числа в двоично-десятичное на управляющую шину 8 подается пулевой потенциал, Через шины 14 в двоичный регистр 1 записывается код преобразуемого двоичного числа. Затем включается генератор 9 импульсов. Превый импульс с первого выхода распределителя импульсов опрашивает старший разряд двоичного регистра. При единичном значении ра:-,ряда сигнал поступает на вход блока 2 двоично-десятичных эквивалентов, с выходов которого десятичный эквивалент старшего разряда заносит- ся в двоично-десятичный сумматор 3. Следуюшчй импульс со второго выхода распределителя импульсов опрашивает следующий разряд регистра . L и при наличии в нем единицы си.-нал с выхода элемента И из группы 15 поступает на вход блока эквивалентов. С выходов последнего десятичный эквивалент второго разряда гоступает в сумматор 3, где суммируется с предыдущим ",начениеьи и т,д, После or:— роса всех разрядов импульс с выхода распределителя вь1кл очает генератор импульсов, В режиме преобразования двоично-десятичного числа в двоичное на шину 8 подается единичный потенциал. На шину 7 подается потенциальный двоично-десятичный код преобразуемогс числа, триггеры регистра 1 устанавливаются в нуль, Затем включается генератор импульсов г и импульс с первого выхода распределителя импульсов через открытый элемент

И из группы 17 поступает на блок 2 эквивалентов. С выхода блока на сумматор поступает двоично-peñÿòè÷íèé зквива=

732853 б

Источники информации, принятые во внимание при экспертизе

Формула изобретения

1. Авторское свидетельство СССР

N 526886, zr, G 06 F 5/02,26.02.74.

Преобразователь двоичного кода в двоично-десятичный и обратно, содержащий двоичный регистр, регистр двоично-деся2. Авторское свидетельство СССР по заявке 34 2468249/24, 1876. лент старшего двоичного разряда. Если код на шинах 7 равен коду, поступающему с сумматора, сигнал с выхода равенства схемы 6 сравнения выключает генератор импульсов. Если код на шинах 7 больше кода, поступающего с сумматора, то открыты элементы И 18 четвертой группы, элемент И старшего разряда в группе 16. По окончании первого тактового импульса в регистр 4 двоично-десятичного числа (так же как и в случае равенства кодов) запишется десятичный эквивалент старшего двоичного разряда и единица в старший разряд двоичного регистра. Если код на шинах 7 меньше кода поступающего с выходов сумматора, то регистр 4 и регистр 1 после первого такта не изменяет своих значений. Второй тактовый импульс через открытый элемент И из группы 17 поступает на следующий вход блока эквивалентов 2, с выходов которого на сумматор поступает десятичный эквивалент следующего двоичного разряда. С выходов сумматора на схему 6 сравнения поступает сумма эквивалента второго разряда и содержимого регистра. Если код суммы равен коду на шинах 7, то сигнал со схемы 6 сравнения выключает генератор импульсов. Если код на шинах 7 больше кода, поступаюшеЗ0 го с выходов сумматора, то открыты элементы И из группы 18 и элемент И из группы 16. По окончании второго тактового импульса в регистр 4 двоично-десятичного числа запишется упомянутая сумма и единица во второй разряд регистра

1. В противном случае содержимое регистра сумматора и регистра 1 не изменится и т.д. Таким образом, после выключения

40 генератора выходным сигналом распределителя импульсов 5 (или ранее) в регистре 1 будет содержаться двоичный эквивалент преобразуемого двоично-десятичного числа, 45

Быстродействие устройства при прямом и обратном преобразовании остается одинаковым, поскольку число тактов работы устройства в обоих режимах равно числу разрядов преобразуемых чисел, что в 9

50 раз меньше количества тактов преобразователя. тичных чисел, блок двоично-десятичных эквивалентов, распределитель импульсов, генератор импульсов, первую, вторую и третью группы элементов И, первые входы которых соединены с группой выходов распределителя импульсов, вторые входы элементов И первой группы соединены с выходами двоичного регистра, а выходы элементов И первой группы соединены с выходами элементов И третьей группы и со входами блока двоично-десятичных эквивалентов, выходы элементов И второй группы соединены со входами двоичного регистра, выход генератора импульсов соединен со входом распределителя импульсов, выход которого соединен с первым входом генератора импульсов, о т л и ч аю шийся тем, что, с целью,увеличения скорости преобразования, он содержит двоично-десятичный сумматор, схему сравнения, четвертую группы элементов И, элемент ИЛИ, первый и второй элементы

И и элемент НЕ, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И и вторыми входами всех элементов И второй группы, выход элемента ИЛИ соединен с первыми входами всех элементов И четвертой группы, вторые

BxoAbI которых соединены с BblxoljBMB двоично-десятичного сумматора, подключенными к первой группе входов схемы сравнения, выходы элементов И четвертой группы соединены с входами регистра пр ично-десятичных чисел, выходы которо о соединены с первой группой входов два:чно-десятичного сумматора, вторая группа входов которого, соединена с выходами блока двоичнс -десятичных эквивалентов, первый и второй выходы схемы сравнения соответственно соединены с первыми входами первого и второго элементов И, втс>рые входы которых соединены с входом элемента HE и со вторыми входами всех элементов И четвертой группы, выход второго элемента И соединен со вторым входом генератора импульсов, вторая группа входов схемы сравнения соединена со входами преобразователя.