Синусно-косинусный функциональный преобразователь

Иллюстрации

Показать всеРеферат

Союз Соаетскик

Социалистическик

Республик

О П И С А Н И Е ()732884

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свкд-ву - (22) Заявлено 22.01.76 .(21) 2317241/18-24 () ) Щ. Кл. с присоединением заявки №

G 06 F 15/34

Государственный комитет (23) Приоритет— по делам иаобретеиий и открытии

Опубликовано 05.05,80. Бюллетень № 17

Дата опубликования описания 10.05.80 (53 ) Д К 68 1. 14 (088.8) Л. Я. Лапкин, Ю. Ф, Сергеев, Н. А. Амирджанян и Э. Э, Лазовская (72) Авторы изобретения (71) Заявитель (54) СИНУСНО-КОСИНУСНЫЙ ФУНКЦИОНАЛЬН6!Й

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к вычислитель. ной технике, в частности к. частотнэ-импульсным вычислительным устройствам.

Известен частотно-импульсный функциональный преобразователь, воспроизводящий

5 тригонометрические функции и построенный на основе двух двоичных умножителей схваченных отрицательной обратной связью (11 .

Указанный преобразователь обладает сравнительно низким быстродействием.

Наиболее близким к изобретению по технической сушности является синусно15 косинусный функциональный преобразователь, содержащий два преобразователя код-частота, схваченных отрицательной обратной связью, причем каждый преобразователь содержит счетчик результата, соединенный группой элементов И-ИЛИ.

Кроме того, имеется также регистр аргумента и развертывающий счетчик, соединенные с блоком сравнения 2).

Недостатком такого преобразователя является сравнительно низкое быстродействие, обусловленное спецификой работы частотно-импульсных вычислительных усъ. ройств.

Бель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что в синусно-косинусный функциональный преобразователь, содержащий регистр аргумента, выходы которого соединены с первой группой входов блока сравнения, вторая группа входов которого соединена с первой группой выходов развертывающего счетчика, вход которого соединен с первым выходом генератора тактовых импульсов, два основных преобразователя код-частота, .каждый из которых содержит счетчик результата и группу элементов

И-ИЛИ, причем выходы счетчика результата соединены с первыми входами элементов И-ИЛИ группы, вторые входы которых соединены с второй группой выхо732884 ф

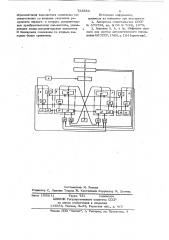

Схема содержит регистр 1 аргумента, лок 2 сравнения, развертывающий счетик 3, генератор 4 тактовых импульсов, лок 5 управления и установки начальных словий, основные преобразователи 6 и 7 од-частота (точного отсчета), дополительные преобразователи 8 и 9 кодастота (грубого отсчета) старшие 10

11 и младшие 12 и 13 разряды счетчиков результата, группы элементов

14-17 И, группы элементов 18-21И-ИЛИ элементы 22 И блокировки, дополнительные элементы 23 И блокировки.

Преобразователи код-частота выполнены по двухотсчетной многосимвольной схеме.

При подаче импульсов тактовой частоы на вход развертывающего счетчика 3 и на входы элементов 14-17 И групп в счетчиках результата начинается отсчет значений функций.

Работа преобразователя может быть описана системой дифференциальных уравнений 1-го порядка: î

Й1 2 2

7 2 о д = т 41 где М4- код счетчика результата, пер-, — вого преобразователя код-частота; и — код счетчика результата вто2. рого преобразователя код-частота; — частота генератора тактовых импульсов, ;

И вЂ” разрядность кодов аргумента и функции.

Решение данной cHcTBMbI дифференциальных уравнений при условии, что в начальный момент времени в счетчиках результата первого и .второго преобразователей кодчастота занесены числа соответственно

0 и 1, имеет вид:

При равенстве кодов в регистре аргумента B развертывающем счетчике блок сравнения выдает сигнал, который прерывает цепь обратной связи между преобразователями код-частота. дов развертывающего счетчика, выходы элементов И-NJlH группы первого и вто- б рого основных преобразователей код-час- ч тота через соответствующие элементы И б блокировки соединены соответственно с 5 у первыми входами счетчиков результата второго и первого основных преобраэоватен лей код-частота, управляющие входы ко- . ч торых соединены с выходами блока уп- и равления и установки начальных условий, управляющие входы элементов И блокировки соединены с первым выходом блока сравнения, введены два дополнительных преобразователя код-частота, каждый из которых содержит счетчик результата, группу элементов И-ИЛИ и группу элементов И, причем выходы старши.х и младших разрядов счетчика результата соединены соответственно с первыми входами элементов И группы и элементов И-ИЛИ группы, выходы элементов И-ИЛИ группы и элементов И группы первого и второго дополнительных преобразователей кодчастота через соответствующие дополнительные элементы И блокировки согдине25 ны соответственно со вторыми входами счетчика результата второго и первого основных преобразователей код-частота, в каждый из основных преобразователей

30 код-частота введена группа элементов И, причем выходы старших разрядов счетчика результата соединены с первыми вхсдами элементов И группы, вторые входы элементов И групп обоих основных и до35 полнительных преобразователей код-частота соединены со вторым выходом генератора TGKToBI,KK импульсов, выходы элементов И группы первого и второго основных преобразователей код-частота че4О рез соответствующие элементы И блокировки соединены с первыми входами счетчика результата соответственно второго и первого основных преобразователей код- частота, вторые входы элементов И-ИЛИ 45 группы обоих дополнительных преобраэсл вателей код-частота соединены с соответ ствующими выходами развертывающего счетчика, выходы переноса счетчика результата первого и второго основных пре5о образователей код-частота соединены соответственно со входами счетчиков результата первого и второго дополнительных преобразователей код-частота, управляошие входы дополнительных. элементов И

55 блокировки соединены со вторым выхсъдом блока сравнения, На чертеже изображена структурная схема предложенного устройства.

Формула изобретения

Синусно-косинусный функциональный преобразователь, содержаший регистр аргумента, выходы которого соединены с первой группой входов блока сравнения, вторая группа входов которого соединена с первой группой выходов развертываю-. шего счетчика вход которого соединен с первым выходом генератора тактовых им5 . 7328

При этом коды в счетчиках результата соответствуют значениям синуса и косинуса аргумента, записанного в регистре 1. . Преобразователь работает следуюшим образом.

Предварительно с помощью блока 5 осуществляется начальная установка счетчиков результата основных и дополнительных преобразователей код-частота.

Затем на регистр 1 аргумента записыва- 1О ется двоичный код аргумента Х, после чего включается генератор 4 тактовых импульсов.

Дальнейшая работа устройства проходит.в. два этапа.

На первом этапе — этапе обработки грубого отсчета (ГО) - многосимвольные частотно-импульсные последовательности с выходов основных и дополнительных преобразователей код-частота поступают соответственно на первые и вторые входы счетчиков результата основных преобразователей код-частота. Обработка ГО заканчивается по сигналу с блока

2 сравнения при совпадении кодов в раз25 вертываюшем счетчике 3 и в старших разрядах регистра 1 аргумента. По этому сигналу отключаются вторые входы счетчиков результата основных преобразователей код-частота с помошью элеЗо ментов 23 H и начинается второй этап— этап обработки точного отсчета (ТО).

При этом работают только преобразователи 6 и 7.

Работа устройства заканчивается по сигналу с блска сравнения при совпадении кодов в развертываюшем счетчике и в младших разрядах регистра 1 аргумента.

В результате в счетчиках результата имеется синус Х и косинус Х.

Таким образом, данный преобразователь обладает большим быстродействием примерно при тех же затратах оборудова45 . ния, вследствие чего значительно расширяется область применения предлагаемь1х . преобразователей.

84 пульсов, два основных преобразователя код-частота, каждый иэ кото рых содержит счетчик результата и группу элементов

И-ИЛИ, причем выходы счетчика результата соединены с первыми входами элементов И-ИЛИ группы, вторые входы ксторык соединены с второй группой выходов развертываюшего счетчика, выходы элементов И-ИЛИ группы первого и второго основных преобразователей кодчастота через соответствуюшие элементы

И блокировки соединены соответственно с первыми входами счетчиков результата второго и первого основных преобразователей код-частота, управляюшие входы которых соединены с выкодами блока управления и установки начальных условий, управляюшие входы элементов И блокировки соединены с первым выходом блока сравнения, о т л и ч а ю ш и и с я тем, что, с целью повышения быстродействия, в него введены два дополнительных преобразователя код-частота, каждый из которых содержит счетчик результата; группу элементов И-ИЛИ и группу элементов И, причем выходы старших и младших разрядов счетчика результата соединены соответственно с первыми входами элементов И группь| и элементов И-ИЛИ группы, выходы элементов И-ИЛИ группы и элементов И группы первого и второго дополнительных преобразователей код-частота через соответствующие дополнительные элементы И блокировки сое динены соответственно со вторыми входами счетчика результата второго и первого основных преобразователей код-частота, в каждый из основных преобразователей, код-частота введена группа элементов И, причем выходы старших разрядов счетчика результата соединены с первыми входами элементов И группы, вторые входы элементов И групп обоих основных и дополнительных преобразователей код-частота соединены со вторым выходом генератора тактовых импульсов, выходы элементов И группы первого и второго основных преобразователей код-частота через соответствуюшие элементы И блокировки соединены с первыми входами счетчика результата соответственно второго и первого основных преобразователей кодчастота, вторые входы элементов И-ИЛИ группы обоих дополнительных преобразователей код-частота соединены с соответствующими выходами развертываюшего счетчика, выходы переноса счетчика ре.зультата первого и второго основнык пре7 732884 8 образователей код-частота соединены со- Источники информации, ответственно со входами счетчиков ре- принятые во вниманче при экспертизе з льтата первого и второго допопнитель- 1, Авторское свидетельство СС

СССР ных преобразователей код-частота, управ- N. 373732, кл. б 06 G /

) ., 7 26 1973. ляющие входы дополнительных элементов 2. Воронов онов А. А. и др. цифровые анаИ блокировки соединены со вторым вылоги для систем л систем автоматического управходом блока сравнения. ления АН СССР, 1960, с. 1 84 (прототип) .

Составитель И. Хазова

Редактор С. Пыжова Техред Ж. Кастелевич Корректор М. немчик

Заказ 1555/11 Тираж 751 Подписное

UHHHlIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, -35, Раушская наб., д. 4/5

Филиал ППП "Патент, г» Ужгород, ул. Проектная, 4