Многоканальный преобразователь угла поворота вала в код

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

11ц 732956 (61) Дополнительное к авт. свид-ву (22) Заявлено 08. l2.77 (2 I ) 2552608/18-24 (51) М. Кл.

G 08 О 9/04 с присоединением заявки РЙ—

Гооударотввииый комитет (23) Пркоритет— (53) УДК 68l.325 (08&.8) о делам изооретеиий и открытий

Опубликовано 05.05.80. Бюллетень .% 17

Дата опубликования описания 08.05.80 (72) Авторы изобретения

А. А. Андреев, М. Я. Братчиков, B. В. Петров и Г. И, Трусов (7I ) Заявитель (54) М НОГОКАНА ЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА

ВАЛА В KOg

Изобретение относится к области ав« томатики и вычиспительной техники.

Известны преобразователи угла поворота вала в код, содержащие синусно-косинусные (СК) датчики, соединенные с входным коммутатором, выходы которого соединены через усилители с перекпючатепем квадрантов, блок уггравления, блок сравнения, преобразователь код-напряжение и аппроксимирующий узел flj

Наиболее близким к предлагаемому по

1О технической сущности является многоканальный преобразователь угла поворота вала в код, который содержит СК-датчики, подключенные через входной коммутатор

15 и развязывающие усилители к коммутатору октантов, соединенному со входом декодирующего преобразователя код-напряжение, со входом регистра октантов, с одним из входов. блока сравнения и с опним из входов распределитепьного блока.

Второй выход распределительного блока через регистр управления и декодирующий преобразователь код-напряжение подкпю2 чен к другому вход блока сравнения, выход которого подключен к регистру октантов и регистру управления. Бпокприэнака отсчета подключен к регистру управления. Входы блока автоматической синхронизации подключены к выходам парафаэных усилитепей, а его выход соединен со входом распределительного блока ) 2)

Наличие усилителей на входе коммутатора октантов, где производится опредепение фаз напряжений обмоток СК-датчика и сравнение их по амплитуде; наличие декодирующего преобразователя только водной цепи сигнала СК-датчика приводит к снижению точности известных преобразо вате лей.

Цепью изобретения является повышение точности преобразователя.

Поставленная цель достигается тем, что в многоканальном преобразователе угла поворота вала в код входной коммутатор соединен с коммутатором квадрантов, первый выход которого соединен со входом распределитепьного блока, à arn732956 рой и третий выходы через соответствующие развязывающие усилители соединены с третьим входом декодирующего преобразоватепя, другой вход блока сравнения соединен с нулевой шиной, 5

Многоканальный преобразователь угла поворота вала в код построен по принципу поразрядного взвешивания на основе компенсационной схемы, в которой в качестве измеряе мого и опорного напряжений > 0 испопьзуются синусное и косинусное напряжения СК-датчика.

Такое построение схемы позволяет упростить схему преобразователя и тем самым повысить точность его работы. 15

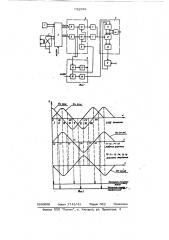

На фиг. 1 представлена структурная схема многоканального преобразователя угла поворота вала в код, на фиг, 2 амппитудная характеристика СК-датчика, а также рабочие участки синусоидального 20 напряжения, используемые для преобразования.

Многоканальный преобразователь угла вала в код содержит: СК-датчики 1, вход- 5 ной коммутатор 2, коммутатор квадрантов 3, декодирующий преобразователь 4, распределительный блок 5, блох ср авнения 6, развязывающие усилители 7.

СК/датчики 1 подключены к входному ц коммутатору 2 и к коммутатору квадрантов 3. Коммутатор квадрантов через раз-. вязывающие усипитепи 7 подсоединены непосредственно к декодирующему преобра- зователю 4 код-напряжение, который под. - з кпючен к блоку сравнения 6. Второй вход блока сравнения 6 заземлен. Распределительный бпок 5 подкпючен к коммутатору квадрантов 3 и к декодирующему преобразоватепю 4.

Коммутатор квадрантов 3 содержит согласующие масштабные усилите ш 8 на входе блока управления 9 электронными ключами и электронные ключи 10.

Декодирующий преобразователь 4 содержит A -разрядный регистр управления

11, электронные ключи разрядов 12, резисторный делитель напряжения 13 и выходные элементы 14.

Распределительный блок 5 задает режим работы преобразователя и содержит регистр квадрантов 15, блок синхронизации 16, блок 17 формирования кода двух старших разрядов, распредепитель им55 пульсов 18, обеспеч ивающий поразрядное уравновешивание.

Работа преобразователя депится на, два . BTQDB".

1. Определение квадранта;

2. Опредепение октанта и поразрядное кодирование в пределах октанта.

Для нахождения квадранта кодируемого угла поворота в предлагаемом преобразователе используется один такт кодирования, которым определяется фаза синусного и косинусного напряжений СК-датчика, Напряжения с синусной и косинусной обмоток одновременно поступают на входы согласующих масштабных усилителей 8 коммутатора квадрантов 3 и входы электронных ключей 10. Вход блока управления

9, где определяется база синусного и косинусного напряжений, соединен с выходом регистра квадрантов 15 распределительно го блока 5, где запоминается полярность напряжений обмоток СК-датчика., Регистр квадрантов 15 вырабатывает сигнал, пос тупающий на блок управления 9 коммутатора квадрантов 3. Бпок управления 9 переключает электронные ключи 10 таким образом, что в зависимости от фазы синусного и косинусного напряжений эти напряжения с выхода электронных ключей 10 поступают на прямой ипи инверсный входы развязывающих усилителей 7. На выходе развязывающих усилителей 7, которые под кпючены непосредственно к входам электронных ключей разрядов 12, управляющих резисторным делителем напряжения 13 декодирующего преобразователя 4, напряжения синусной и косинусной, обмоток СКдатчика находится в противофазе (см. фиг. 2), что необходимо для правильной работы предлагаемого преобразователя.

Выход регистра квадрантов 15 соединен с входом блока. 17 формирования кода двух старших разрядов, выходной сигнал которого характеризует квадрант угла поворота СКТ-датчика.

В момент перехода через нуль положительного напряжения питания СК-датчика блок синхронизации 16 распределительного бпбка 5 вырабатывает импульс, запускающий распределитель импульсов 18, который вырабатывает A тактов кодирования, необходимых для нахождения октанта и поразрядного уравновешивания в предепах октанта. Блок синхронизации 16 вырабатывает также эталонные частоты и импульс синхронизации с учетом фазовых сдвигов выходных напряжений различных типов CK-датчиков .относительно питающего напряжения датчиков, что обеспечивает временное согласование работы погических узпов предлагаемого преобразователя и уравновешивание измеряемого

732956 напряжения в момент достижения рабочих участков синусоидального напряжения (см. фиг. 2).

Первым тактом, поступающим с распределителя импульсов 18, триггер старшего разряда регистра управления ll u электронный ключ разряда 12 декодирующего преобразователя 4 устанавливаются в состояние, коммутирующее положительный полунериод напряжения, а остальные 10 разряды декодирующего преобразователя

4 устанавливаются в состояние, коммути рующее отрицательный полупериод напряжени я СК-датчика. Эти напрядения через электронные ключи разрядов 12 поступают на вход резисторного делителя напряженйя. 13 и при равенстве напряжений на выходе резисторного делителя напряжений

l3 формируется нулевой потенциал, который поступает на один из входов блока .сравнения 6. Другой вход блока сравнения ,6 подключен к нулевой шине предлагаемо;го преобразователя.

Если амплитуда положительного полу периода напряжения больше амплитуды напряжения отрицательного полупериода, то на выходе резисторного делителя напряжения 13 формируется амплитуда напряжения положительного полупериода. Аналогично формируется амплитуда напряжения отрицательного полупериода. .Выходное напряжение декодирующего преобразователя 4 поступает на вход блока сравнения 6 и сравнивается в нулевым потенциалом, поступающим на второй вход

35 блока сравнения; блок сравнения 6 вырабатывает HB tf -такте кодирования импульс, управляющий триггером A — разряда регистра управления 11 и отключает этот разряд декодирующего преобразователя 4 из процесса уравновешивания при условии

О,„) 0 (Uy — выходное напряжение декодируюшего преобразователя). При

U .n 0 блок сравнения 6 импульс управления не вырабатывает и и, - разряд декодирующего преобразователя 4 участвует в процессе уравновешивания.

В результате преобразования на регистре управления 1 1 установится код . угла поворота СК-датчика, который считывается с выходных элементов 14, уп. равляемых регистром управления 11.

И предлагаемом многоканальном преобразователе по сравнению с известным подключение обоих выходов коммутатора квадрантов непосредственно к декодирующему преобразователю код-напряжение позволит повысить точность преобразования,угол-код. В известном же устройстве декодируюший преобразователь код-напряжение расположен только в одной цепи синусного (или косинусного) сигнала цепи СК-датчика, что приводит к дополнительной погрешности преобразователя формула изобретения

Многоканальный преобразователь угла поворота вала в код, содержащий синусно-косинусные датчики, соединенные с входным коммутатором, коммутатор квадрантов, вход которого соединен с первым выходом распределительного блока, второй выход которого соединен с первым вхо- . дом декодирующего преобразователя, выход которого соединен с одним из входов блока сравнения, выход блока сравнения соединен с вторым входом декодирующего преобразователя, о т л и ч а ю щ и йс я тем, что, с целью повышения точности преобразователя, в нем входной коммутатор соединен с коммутатором квадрантов, первый выход которого соединен со входом распределительного блока, а второ и тре тий выходы через соответствующие развя,зываюшие усилители соединены с третьим входом декодирукйцего преобразователя, другой вход блока сравнения соединен с нулевой шиной.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N 36 7442, кл. Ci 08 С 9/04, 1970.

2. Авторское свидетельство СССР

N. 328493, кл. (т 08 С 9/04, 1970 (прототип) .