Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советские

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

iii)733018 (61) Дополнительное к авт. свнд-ву (22)Заявлено 12,10.77 (21)2533892/18:-24 (5$ ) Щ. Кл.

<д 11 С 9/06 т:т 06. F 7/10 с присоединением заявки М

Гаеудярстееняый камнтет (23) Приоритет е аеяем нзабретений н аткрытнй

Опубликовано 05.05.80. Бюллетень .Щ 17

Дата опубликования описания 08 05 80 (53 ) УД К 68 1. .327.26 (088,8) (72) Авторы изобретения

В. П. Бодня, Е, К. Мамонов и P А. Камалов (7l) Заявитель (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике, может быть использовано при обслуживании запросов абонентов в порядке их поступления.

Известно устройство для накопления поступающей информации, содержащее многоступенчатый сдвигающий накопитель, блок опроса и элементы И $1)

Входящий в схему дополнительный регистр для хранения информации, находящейся на обслуживании, снижает надежность устройства.

Известно буферное запоминающее устройство, содержащее последовательно соединенные группы запоминающих ячеек и управляющие ячейки, соответствующие каждой такой группе и состоящие из бистабильного элемента памяти, элемента совпадения и элемента задержки и

В таком устройстве передача информа ции к группе свободных запоминающих ачеек проводится через группы предшест. вующих ячеек, что снижает бьх:тродействие схемы.

Наиболее близким к данному техническому решению является буферное запоминающее устройство, содержащее матрицу запоминающих регистров, установочные входы которьас соединены с выходами

5 первых элементов И, первые входы которых подключены ко входным. шинам устройства, а вторые входы — к инверсным выходам регистра управления, установочные входы которого подключены к выходам первых элементов ИЛИ, входы которыХ соединены с инверсными выходами соответствующих запоминающих регистров $3)

Недостатком известного устройства авлается ограниченное быстродействие из-за последовательного срабатьванкя регистров и задержки обработки очередного запроса абонента.

Целью настоящего изобретения явля ется повьапеттие быстродействия и надежности устройства.

Поставленная цель достигается тем, что в буферное запоминающт <. устрой<-ТВо з

73 введены распределитель импульсов, формирователи импульсов, элементы И и элементы ИЛИ, прямые выходы регистра управления соединены с третьими входа ми первых элементов И соответствующих запоминаюших регистров и со входами второго элемента ИЛИ, выход которого подключен к управляющему входу распределителя импульсов, выходы которого под ключены ко входам соответствуюших формирователей импульсов и к первым входам вторых элементов И, вторые входы которых соединены с прямыми выходами соответствующих запоминающих регистров, а выходы вторых элементов И соединены со входами третьих элементов ИЛИ, выходы которых подключены к выходным шинам устройства, выходы формирователей импульсов соединены с соответствующими входами сброса запоминающих регистров и регистра управления, инверсный выход последнего разряда которого подключен к первым входам третьих элементов И,;.

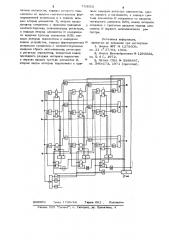

Вторые входы которых подключены к прямым выходам регистра управления, кроме первого и последнего, а выходы третьих элементов И соединены со входами четвертого элемента ИЛИ, выход которого соединен с третьими входами первых элементов И первого запоминаюшего регистра, На чертеже показана функциональная схема буферного запоминающего устройства.

Устройство содержит запоминающие регистры 1, первые элементы И 2, регистр управления 3, первые элементы

ИЛИ .4, причем запоминающие регистры

l выполнены на триггерах 5, второй элемент ИЛИ 6, распределитель импульсоВ 7, вторые элементы И 8, третьи элементы ИЛИ 9, формирователи импуль сов 1О, третьи элементы И 11 и четвертый элемент ИЛИ 12.

В исходном состоянии регистры 1 и

3 сброшены и первые элементы И 2 первого запоминающего регистра 1 открыты для. приема запроса, а поступление запроса на последующие запоминающие регистры 1 запрещено сигналами с прямых выходов регистра управления 3, которые запрещают и работу распределителя импульсов 7 через элемент ИЛИ 6. Посту- пивший запрос, изменив состояние управляющего регистра 3 через первые элементы ИЛИ 4, тем самым разрешает поступление следуюшего запроса на сле,дуюший запоминаюший регистр 1 и вклю3018

Д чает распределитель импульсов 7, сигналы на выходе которого последовательно начинают опрашивать запоминающие регистры 1 и передавать считанную с них информацию на выход устройства через вторые элементы И 8 и третьи элементы

ИЛИ 9. Сброс запоминаюших регистров и регистра управления после опроса происходит по заднему фронту сигнала с распределителя импульсов 7.

Если в этот момент на вход устройства поступят следуюшие запросы, они будут записаны в последующие запоминающие регистры 1, С целью исключения

I5 записи последуюших запросов в первый запоминающий регистр, который обнуляется после считывания с него информации, при отсутствии информации по запросам в последнем запоминающем регистре и

20 при наличии ее в промежуточных регистрах, т.е, для соблюдения очередности регистрации запросов, с инверсного выхода последнего разряда регистра управления 3 на первые входы третьих элементов И ll поступает сигнал, запрешаюший такую запись в первый запоминающий регистр 1, При наличии информации в последнем регистре 1 или при отсутствии ее в промежуточных запоминающих регистрах . запись запросов в первый запоминаюший регистр разрешается.

30 формула изобретения

Буферное запоминаюшее устройство, содержашее матрицу запоминаюших регистров, установочные входы которых соединены с выходами первых элементов И, первые входы которых подключены ко входным шинам устройства, а вторые входык инверсным выходам регистра управления, установочные входы которого подключены к выходам первых элементов

ИЛИ, входы которых соединены с инверсными выходами соответствуюших запоминаюших регистров, о т л и ч а ю ш е е— с я тем, что, с целью повышения его

l5 быстродействия и надежности, в него введены распределитель импульсов, формирователи импульсов,. элементы И и элементы ИЛИ, прямые выходы регистра управления соединены с третьими входами

55 первых элементов И соответствующих запоминаюших регистров и со входами второго элемента ИЛИ, выход которого подключен к управляюшему входу распреде733018

11НИИПИ Заказ 1 749/44 Тираж 662, Подписное филиал ППП "Патент", г, Ужгород, ул. Проектная, 4 лителя импульсов, выходы которого подключены ко входам соответствующих формирователей импульсов и к первым входам вторых элементов И, вторые входы которых соединены с прямыми выходами с соответствуюших запоминающих регистров, а выходы вторых элементов И соединены со входами третьих элементов ИЛИ, выходы. которых подключены к выходным шинам устройства, выходы формирователей импульсов соединены с соответствующими входами сброса запоминающих регистров и регистра управления, инверсный выход последиего разряда которого подключен к первым входам третьих элементов И, вторые входы которых подключены к пряМым выходам регистра управления, кроме первого и последнего, а выходы третьих элементов И соединены со входами четвертого элемента ИЛИ, выход которого соединен с третьими входами первых элементов И первого запоминающего ре гистра.

Источники информации, 10 принятые во внимание при экспертизе

1. Заявка фРГ No 1275609, кл. 21 а 37/64, 1968.

2. Заявка Великобритании N 1293032,. кл, 4 С, 1972.

3. Патент США No 3588847, кл..340-173, 1971 (прототип).