Запоминающий элемент

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<" > 733022 (61) Дополнительное к авт. свид-ву— (22) Заявлено 20.06.77 (21) 2497709/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл, 2 б 11 С 11/34

Государстееииый комитет

СССР

Опубликовано 05.05.80. Бюллетень № 17

Дата опубликования описания 15.05.80 (53) УДК 681.327 (088.8) ао делам изооретеиий и открытий (72) Авторы изобретения

А. С. Федонин и Ю. И. Кузовлев (71) Заявитель (54) ЗАПОМИНАЮЩИЙ ЭЛ ЕМЕНТ

Изобретение относится к интегральным запоминающим устройствам и может быть использовано в вычислительной технике и системах дискретной автоматики.

Известен запоминающий элемент, содержащий резистор, два р-и-р транзистора и два двухэмиттерных и-р-и транзистора с перекрестными связями (1j

Указанный запоминающий элемент позволяет надежно хранить записанную информацию, но для смены ее необходимо выключить одну пару транзисторов р-и-р и и-р- и типов, составляющих тиристорную структуру, и включить другую пару р-и-р и и-р-и тран исторов, что существенно снижает его быстродействие.

Кроме того, такой запоминающий элемент занимает большую площадь при реализации его в интегральном исполнении, в связи с чем он непригоден для построения больших интегральных схем запоминающих устройств емкостью 1024 бит и более.

Известен также запоминающий элемент, содержащий четыре р-и-р и два п-р-и транзистора, работающих в инверсном включении и перекрестно связанных между собой (2).

Связи между транзисторами осуществлены таким образом, что все транзисторы имеют одну общую область и-типа проводимости что позволяет весь запоминающий элемент реализовать в одной изолированной области.

Однако наличие большого количества элементов и перекрестных связей не дает возможности существенно снизить занимаемую элементом площадь и он не может быть использован также для построения больших интегральных схем запоминающих устройств.

19 Кроме того, известный запоминающий элемент обладает малым быстродействием при считывании информации и малым током считывания, что объясняется связью запоминающего элемента с информационными шинами через медленные р-и-р транзисторы.

Наиболее близким к предлагаемому является запоминающий элемент, содержащий транзистор р-и-р типа, первый и второй двухэмиттерные транзисторы и-р-и типа, адресную шину, шину опорного напряжения, причем коллектор и база р-и-р транзистора соединены соответственно с базой и коллектором первого транзистора п-р-л типа, эмиттер о-и-р транзистора соединен

733022 с адресной шиной, один эмиттер первого п-р-и транзистора соединен с шиной опорного напряжения, а другой — с первой информационной шиной; коллектор, база и один эмиттер второго и-р-и транзистора соединены соответственно с базой, коллектором и Эмиттером, соединенным с шиной опорного напряжения, первого и-р-и транзистора, второй эмиттер второго п-р-п транзистора соединен со второй информационной шиной (3).

Для записи информации в такой запоминающий элемент необходимо обеспечить большой перепад напряжения между адресной и информационной шинами, так как ток должен пройти через три р-и перехода (база эмиттер р-и-р транзистора, база-коллектор второго n-p-п транзистора и базаэмиттер первого и-р-и транзистора), в противном случае запись может быть неустойчивой и медленной.

Кроме того, такой запоминающий элемент занимает в интегральном виде большую площадь из-за наличия четырех эмиттеров и-р-и транзисторов и перекрестной связи между и-р-и транзисторами.

Цель изобретения — повышение быстродействия запоминающего элемента.

Указанная цель достигается тем, что база и эмиттер второго транзистора и-р-п типа соединены соответственно с эмиттером и коллектором транзистора p-n-p типа, коллектор — со второй информационной шиной.

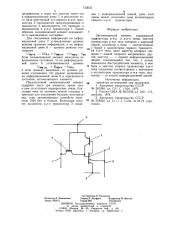

На чертеже представлена электрическая схема предлагаемого запоминающего элемента.

Запоминающий элемент содержит транзистор 1 р-п-р типа, двухэмиттерный транзистор 2 и-р-и типа, транзистор 3 и-р-и типа, адресную шину 4, шину опорного напряжения 5 и информационные шины 6 и 7.

Эмиттер р-п-р транзистора 1 подключен к адресной шине 4, база и коллектор транзистора 1 соединены соответственно с коллектором и базой п -р-п транзистора 2, один из эмиттеров транзистора 2 подключен t шине опорного напряжения 5, второй— информационной шине 6, эмиттер и база и-р-и транзистора 3 подключены соответственно к коллектору и эмиттеру р-и-р транзистора 1, а коллектор транзистора 3 — к информационной шине 7.

Предлагаемый запоминающий элемент работает следующим образом.

В режиме хранения информации потенциал шины опорного напряжения 5 поддерживается на уровне

Uon.ш. = U4Ap.à. Uocx., где U< — напряжение на опорной шине 5, U p.< — напряжение на адресной шине 4;

U — суммарное падение напряжения на совмещенной структуре, состоящей из транзистора 1 р-n-p типа и транзистора 2 и — p — и типа, когда эта структура включена.

Потенциал на информационной шине 6 поддерживается на уровне

U инф;, щ. >11ддр.щ, — 21-1б.э., где U,, — напряжение на информационной шине 6;

U6a, — прямое падение напряжения на р-п переходе база эмиттер n-p-u транзистора.

Потенциал на информационной шине 7 поддерживается на уровне

1-) )ииф.д щ, 1-"ддр а. — U6.ê., где U6к. — прямое падение напряжейия на р-п переходе база-коллектор п-р-и транзистора.

При этом, если запоминающий элемент выключен, возможно протекание тока из адресной шины 4 через коллекторный р-п переход и-р-п транзистора 3 в информационную шину 7, в зависимости от установленного на информационной шине 7 уровня напряжения. Если запоминающий элемент включен, то ток из адресной шины 4 через совмещенную (тиристорную) структуру, состоящую из р-и-р транзистора 1 и и — р- п транзистора 2, протекает в шину опорного напряжения 5, обеспечивая тем самым сохранение включенного состояния.

Для записи информации в запоминающий элемент необходимо понизить уровень напряжения на информационной шине 6 до уровня 1-"икр. щ. (1-1ддр. — 2(.3б.э . При этом ток из адресной шины 4 потечет через р-и переход база-эмиттер и-P n транзистора 3, через р-и переход база-эмиттер и-р-и транзистора 2 в информационную шину 6.

Этот ток вызывает протекание коллекторного тока в п-р-и транзисторе 2. который, являясь базовым током р-и-р транзистора 1, вызывает протекание коллекторного тока в р-п-р транзисторе, который, в свою очередь является базовым током и-р-и транзистора 2. Если сумма коэффициентов передачи тока транзисторов 1 и 2 больше 1, то оба транзистора входят в насыщение и остаются в открытом состоянии. При этом прямое падение напряжения на такой структуре

U = U6ç. + 1 к.и,, где U„напряжение коллектор-эмиттер насыщенного р-и — р транзистора 1.

На информационной шине 6 устанавливается напряжение

U щ — — 11ддр,щ, — U

Для выключения запоминающего элемента (смены информации) необходимо повысить напряжение на информационной шине 6 до уровня Бил,щ >Uwp. — Пост,, а на информационной шине 7 понизить до уровня 1 1иифр,щ, (UA4p, — U6.ê

При этом ток из адресной шины потечет через р-и-переход база-коллектор п-р-и транзистора 3 в информационную шину 7. Транзистор 3 в этом случае включен в инверсном

733022 ь нен с информационной шиной, роль этой шины может исполнять сама коллекторная область п-р-п транзистора.

Запоминающий элемент, содержащий транзисторы р-п-р и п-р-п типов, эмиттер транзистора р-п-р типа соединен с адресной шиной, коллектор и база — соответственно с базой и коллектором первого транзистора и-р-п типа, один эмиттер которого соединен с шиной опорного напряжения, другой эмиттер — с первой информационной шиной, отличающийся тем, что, с целью повышения быстродействия элемента, в нем база и эмиттер второго транзистора и-р-и типа соединены соответственно с эмиттером и коллектором транзистора р-и-р типа, коллектор — со второй информационной шиной.

Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 381098, кл. G11 С 11/34, 1972.

2. Патент США № 3815106, кл. 340 — 173, опублик. 1974.

3. Авторское свидетельство СССР № 378955, кл. G 11 С 11/34, 31.01.72 (прототип).

5 направлении и через его эмиттер течет ток в информационную шину 7, в результате чего база-эмиттерный р-и-переход и-р-п транзистора 2 оказывается зашунтированным и транзистор 2 выключается, что приводит к выключению и р-и-р транзистора 1. Таким Формула изобретения образом, запоминающий элемент оказывается в выключенном состоянии.

Для считывания информации на информационной шине 7 устанавливают уровень режима хранения информации, а на информационной шине 6 — уровень режима счи î тывания

U .ù. — 2Ug э. (Uèöô., щ, (U .ù — 1./од

Если запоминающий элемент находится во включенном состоянии, то на информационной шине 6 устанавливается уровень 1имр,1щ. = 1 ар.я. — Uon; а если элемент выключен, то уровень режима считывания.. По уровню напряжения на информационной шине 6 и определяется состояние запоминающего элемента.

Предлагаемый запоминающий элемент содержит всего три элемента, кроме того в нем отсутствуют перекрестные связи, благодаря чему он занимает малую площадь и пригоден для построения больших интегральных схем запоминающих устройств емкостью 1024 бит и больше. Благодаря тому, что коллектор и-р-и транзистора 3 соедиСоставитель Н. Бочарова

Редактор А.Маковская Техред К. Шуфрич Корректор М. Вигула

Заказ 1563/13 Тираж 662 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «патент», г. Ужгород, ул. Проектная, 4