Распределитель импульсов

Иллюстрации

Показать всеРеферат

ка 9F ю 733105

ОП ИСАНМЕ

Союз Советскии

Социалистические

Республик

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 12.10.77 (21) 2530841/18-21 с присоединением заявки №вЂ”

" (23) Приоритет— (51) М. Кл.;

Н 03 К 17/62

Гасударственный комитет

Опубликовано 05.05.80. Бюллетень №17

Дата опубликования описания 15.05.80 (53) УДК 681.372 (088.8) до делам иэобретеиий и открытий (72) Авторы изобретения

А. Г. Андрущенко, А. Д. Дубовых, А. В. Королев, В. П. Белоус и И. В. Ткачев (71) Заявитель (54) РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к автоматике и телемеханике и может использоваться при коммутации электрических сигналов.

Известны распределители импульсов, выполненные на кольцевом регистре, содержащем триггеры и элементы И (1) .

Недостаток этих устройств — низкая помехоустойчивость в работе.

Известны также распределители импульсов, содержащие и — триггеров и 2п — элементов И, соединенные по кольцевой схеме, причем прямые и инверсные выходы каждо10 триггера подключены к соответствующим входам соответственно К вЂ” ого и (К+и — 1)oro, а также (К вЂ” 1) — ого и (К+п)-ого элементов И (2) .

Недостаток этого устройства — низкая помехоустойчивость в работе при воздействии перекрестных помех по цепям управления и питания.

С целью повышения помехоустойчивости в распределитель импульсов, содержащий и-триггеров и 2п-элементов И, соединенных по одному из входов по кольцевой схеме, прямой выход К-ого триггера (где К = 1..n) соединен с соответствующими входами К-ого и (К+ n — 1) -oro элементов И, а инверсный

2 выход — с соответствующими входами (К вЂ” 1)-«о и (К+п)-ого элементов И, введено и-блоков управления и элемент задержки, причем прямой выход каждого К-ого триггера соединен с первым входом К-ого и вторым входом (К+п)-ого блоков управления, а инверсный выход — с третьим входом К-ого и четвертым входом (К+ l ) блоков управления, при этом первый, второй и третий выходы каждого К-ого блока управления подключены соответственно к единичному входу, входу синхронизации и нулевому входу К-oro триггера, информационный вход каждого триггера, кроме первого, соединен с прямым выходом (К вЂ” 1)-ого триггера, а первого триггера — с инверсным выходом п-oro триггера, кроме того, входная шина подключена к пятым входам и через элемент задержки — к шестым входам каждого блока управления, а каждый блок управления содержит элементы И-НЕ, инвертор и элемент запрета, причем первый вход блока управления соединен с первыми входами первого и второго элементов И вЂ” НЕ второй вход — с первым входом третьего элемента И вЂ” НЕ, второй вход которого и первый вход четвертого элемента И вЂ” НЕ под733105 ключены к третьему входу блока управления, при этом четвертый вход блока управления соединен со вторым входом первого элемента И вЂ” НЕ, третий вход которого подключен к третьему входу третьего элемента

И вЂ” НЕ и выходу элемента запрета, прямой вход которого соединен с шестым входом блока управления, а инверсный — с выходом пятого элемента И вЂ” НЕ и через инвертор — со вторым выходом блока управления, кроме того, первый выход блока управления соединен с выходом второго элемента И вЂ” НЕ и первым входом пятого элемента И вЂ” НЕ, а третий выход — с выходом четвертого элемента И-НЕ и вторым входом пятого элемента И вЂ” НЕ, третий вход которого подключен к пятому входу блока управления, при этом выходы первого и третьего элементов И вЂ” НЕ соединены со вторыми входами соответственно второго и четвертого элементов И вЂ” НЕ.

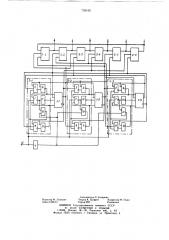

На чертеже представлена функциональная схема распределителя импульсов для и — 3.

Распределитель содержит потенциальные триггеры 1 — 1 — 1 — 3, элементы И 2 — 1—

2 — 6, соединенные по одному из входов по кольцевой схеме, блоки 3 — 1 — 3 — 3 управления, элемент 4 задержки. Каждый из блоков управления 3 — 1 — 3 — 3 состоит из элементов И вЂ” НЕ 5 — 9, элемента 10 запрета и инвертора 11. Входная шина (вход)

12 соединена со входом элемента 4 задержки.

Устройство работает следующим образом.

В начале работы, до подачи входных импульсов на входную шину 12, подается установочный импульс, при котором все триггеры 1 устанавливаются в исходное состояние.

Прн этом на прямых выходах триггеров

1 устанавливается низкий уровень напряжения, а на инверсных выходах — высокий уровень напряжения. На всех выходах элементов И 2, кроме последнего, имеется высокий уровень напряжения, а на последнем— низкий уровень напряжения. На всех информационных входах триггеров 1, кроме первого, имеется низкий уровень напряжения, а на информационном входе триггера

1 — 1 — высокий уровень напряжения.

Состояния элементов, входящих в блоки

3 управления соответствуют состоянию элементов, входящих в блок 3 — 1 управления.

В начальный момент времени на единичных входах всех триггеров 1 имеется высокий уро- > вень напряжения, а на нулевых входах — низкий уровень напряжения. Это приводит к тому, что перекрестные помехи, воздействующие по цепям управления и питания, практически не могут изменить состояния триггеров I.

Состояние любого из триггеров 1 не изменится и при воздействии входных импульсов в том случае, когда уровень напряжения на прямом выходе триггера 1 соответствует уровню напряжения на его информационном входе. Во всех других случаях состояние триггера 1 изменится под воздействием входного импульса при условии, что на его установочных входах имеется высокий уровень напряжения.

При появлении низкого уровня напряжения на выходе элемента 4 задержки и на выходе элемента 10 запрета блока 3 — 1 управления появляется высокий уровень напряжения, который переводит элементы

И вЂ” НЕ 8, 9 в такое состояние, при котором на нулевой вход триггера 1 — 1 подается высокий уровень напряжения. Одновременно подается разрешение на вход элемента

И вЂ” НЕ 7.

В таком состоянии только триггер 1 — 1 подготовлен к воздействию входных импульсов, так как на его установочных и информационном входах имеется высокий уровень напряжения, а на прямом выходе — низкий уровень напряжения.

С поступлением первого входного импульса через элемент И вЂ” НЕ 7 и инвертор 11 блока 3 — 1 управления триггер 1 — 1 переходит во второе устойчивое состояние, а на выходе элемента И†HE 6 появляется низкий уровень напряжения, который удерживает триггер 1 — 1 в установившемся состоянии (в единичном состоянии). Одновременно элемент И 2 — 6 срабатывает и на его выходе возникает высокий уровень напряжения. Срабатывает элемент И2, так как с него снимается запрет на его выходе появляется низкий уровень напряжения.

По окончании действия первого импульса на входе 12 и выходе элемента 4 задержки происходит подготовка блока управления 3 — 2.

С приходом второго входного импульса переключается триггер 1 — 2, блокмрующийся выходным сигналом элемента И вЂ” НЕ

6 блока 3 — 2 управления, который работает аналогично блоку управления 3 — 1. Одновременно срабатывает элемент И 2 — 1, на выходе которого появляется высокий уровень напряжения, а, следовательно, снимается запрет с элемента И 2 — 2. Последний срабатывает и на его выходе появляется низкий уровень напряжения с задержкой относительно появление высокого уровня напряжения на выходе элемента И 2 — 1 и т.д.

Величина времени задержки определяется временем срабатывания выбранного типа микросхем и лежит в пределах от нескольких наносекунд до одной микросекунды, что вполне достаточно для временной коммутации сигналов.

Таким образом, блок 3 — 1 управления подготавливается по окончанию шестого и третьего импульсов, а работает по началу первого и четвертого импульсов за цикл работы. Блок 3 — 2 управления подготавливается по окончанию первого и четвертого

733105 импульсов, а работает по началу второго и пятого импульсов за» цикл работы и т.д.

В распределителе импульсов исключаются сбои триггеров в статическом режиме работы за счет удержания триггеров в установившемся состоянии низким уровнем напряжения на одном из установочных входов и повышается помехоустойчивость в динамическом режиме работы за счет уменьшения времени, в течение которого на установочных входах триггеров одновременно имеется высокий уровень напряжения. р

Формула изобретения

1. Распределитель импульсов, содержащий и-триггеров и 2п-элементов И, соединенных по одному из входов по кольцевой схеме, прямой выход К-ого триггера (где

К = 1...n) соединен с соответствующими входами К-oro и (К+и — 1)-ого элементов И, а инверсный выход — с соответствующими 2о входами (К вЂ” 1) — ого и (К+и) — ого элементов И, отличающийся тем, что, с целью повышения помехоустойчивости, введено и-блоков управления и элемент задержки, причем прямой выход каждого К-ого триггера соединен с первым входом К-ого и вторым входом (К+ 1) -ого блоков управления, а инверсный выход — с третьим входом

К-ого и четвертым входом (К+1) блоков управления, при этом первый, второй и третий выходы каждого К-ого блока управле- sp ния подключены соответственно к единичному входу, входу синхронизации и нулевому входу К-ого триггера, информационный вход каждого триггера, кроме первого, соединен с прямым выходом (К вЂ” 1) — ого триггера, а первого триггера — с инверсным зю выходом n-oro триггера, кроме того, входная шина подключена к пятым входам и через элемент задержки — к шестым входам каждого блока управления.

2. Распределитель по п.1, отличающийся тем, что каждый блок управления содержит элементы И вЂ” НЕ, инверстор и элемент запрета, причем первый вход блока управления соединен с первыми входами первого и второго элементов И вЂ” НЕ, второй вход— с первым входом третьего элемента И вЂ” НЕ, второй вход которого и первый вход четвертого элемента И вЂ” НЕ подключены к третьему входу блока управления, при этом четвертый вход блока управления соединен со вторым входом первого элемента И вЂ” НЕ, третий вход которого подключен к третьему входу третьего элемента И вЂ” НЕ и выходу элемента запрета, прямой вход которого соединен с шестым входом блока управления, а инверсный — с выходом пятого элемента

И вЂ” НЕ и через инвертор — со вторым выходом блока управления, кроме того, первый выход блока управления соединен с выходом второго элемента И вЂ” НЕ и первым входом пятого элемента И вЂ” НЕ, а третий выход с — с выходом четвертого элемента И вЂ” НЕ и вторым входом пятого элемента И вЂ” НЕ, третий вход которого подключен к пятому входу блока управления, при этом выходы первого и третьего элементов И вЂ” НЕ соединены со вторыми входами соответственно второго и четвертого элементов И вЂ” НЕ.

Источники информации, принятые во внимание при экспертизе

1. Букреев И. Н., Мансуров Б. М., Горячев В. И. Микроэлектронные схемы цифровых устройств. М., «Советское радио», 1973, с. 231, рис. 625.

2. Авторское свидетельство СССР № 569029, кл. Н 03 К 17/62, 07.04.75 (прототип) .

733105

Составитель Л. Захарова

Реда ктор М. Л и к о в нч Техред К. КУФР"" Корректор М. Пожо

Заказ 1564/14 Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

I 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент» г. Ужгород, ул. Проектная, 4