Устройство для обнаружения сигналов

Иллюстрации

Показать всеРеферат

Союз Соаетскик

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (111 734590 с (61) Дополнительное к авт. свид-ву (51) М. Кп. (22) Заявленоi1909.77 (21) 2528847/18-09 с присоединением заявки ¹ (23) Приоритет

Опубликовано 1505.80. Бюллетень ¹ 18

Дата опубликования описания 1505.80

G 01 S 7/28

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 621. 396. 96 (088. 8) (72) Авторы изобретения

Ф, N. Андреев и Н. Н. Шишов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ СИГНАЛОВ

Изобретение относится к радиотехнике и может. использоваться в Радиолокационной аппаратуре.

Известно устройство для обнаружения сигналов, содержащее элемент задержки и первый ранговый обнаружитель (1), Однако в данном устройстве слабые сигналы подавляются сильным при его 10 появлении в диапазоне элементов разрешения за слабым сигналом.

Цель изобретения — повышение вероятности правильного обнаружения.

Это достигается тем, что в устройство для обнаружения сигналов, содержащее элемент задержки и первый ранговый обнаружитель, введены И-1 ранговых обнаружитилей и логический блок, при этом входы N ранговых «бнаружителей соединены с соответствующим из И входов логического блока, N + 1 выходов которого соединены с соответствующими из N + 1 входов каждого из ранговых обнаружителей, (N + 2)-ые входы которых соединены между собой и с входом з. емента задержки, выход которого соединен с (N + 3)-м входом каждого из )и ранговых обнаружителей, при этом ранговый обнаружитель выполнен в виде N каналов, каждый иэ которых содержит блок запрета, вентиль, формирователь им пульсов и элемент памяти, причем выход каждого предыдущего блока запрета соединен с первым входом по"ледующего блока запрета и с одноименным входом регистра сдвига, N выходов которого соединены с первым входом вентиля канала и первым входом формирователя импульсов, соседнего с ним канала, выход вентиля каждого из N каналов соединен с элементом памяти этого же канала и с соответствующим иэ N входов распределителя импульсов, каждый из N выходов которого соединен с вторым входом элемента памяти одноименного канала, выход формирователя импульсов каждого из N каналов соединен с третьим входом элемента памяти одноименного канала, выход которого соединен с соответствующим из N входов решающего блока, вторые входы вентилей каждого из N каналов соединены между собой, пои этом второй вход соответствующего блока запрета является одноименНым из N входов рангового обнаружителя, третьи входы .формирователей

734590

S (О

2О

30 соединены между собой и являются (N + 1) -ым входом рангового обнаружителя, (N + 2)-ым входом которого является первый вход первого блока запрета, четвертые входы формирователей соединены между собой и явля.ются (И + 3) -им входом рангового обнаружителя,выходом которого является выход решающего блока.

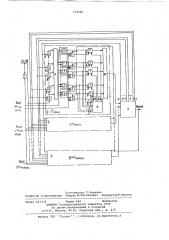

На чертеже изображена структурная электрическая схем» поедложенного устройс тв а.

Устройство для обнаружения сигналов содержит элемент 1 задержки, ранговыз обнаружители 2, логический блок 3. Ранговый обнаружитель 2 состоит из блоков запрета, вентилей 5, формирователей б импульсов и элементов 7 памяти, регистра 8 сдвига, распределителя 9 импульсов и решаюrrrerо блока 10.

Предложенное устройство работает следующим образом, С помощью импульсов сдвига Гс, в осуществляется последовательный сдвиг предварительно записанной в регистр

8 единицы. При этом импульсы сдвига проходят на входы разрядов регистра

8 через блоки 4 запрета, которые открыты при отсутствии обнаруженного сигнала, а при наличии обнаруженного сигнала, на один из которых подается импульс запрета с соответствующегo выхода рзшающего блока 10, Поочередное появление импульса на выходах разрядов регистра. 8 обеспечивает также поочередное подключение входного сигнала через вентили 5 ко входам элементов памяти 7, в которых осуществляется запоминание выборочного значения из входного процесса, а также производится опе.рация сравнения запомненного выборочного значения с текущим значением, подаваемым на элемент памяти 7 через,.распределитель 9, Результаты сравнения в виде единиц или нулей поступают на вход решающего блока 10, .который на основании применения одного из ранговых критериев выдает сигнал, свидетельствующий о наличии в данном канале обнаруженного сигнала.

B логическом блоке 3 производится принятие решения о наличии полезного сигнала во входном колебании на основании анализа информации, постуПающей от всех ранговых обнаружителей 2.

Логический блок 3 вырабатывает импульсы управления для блока 4 запре аричем и) и отсутствии обнар женчого сигнала на всех соответствующих выходах логического блока 3 подклю- . ченных ко вторым входам блока запрета 4, будет разрешающий потенциал.

Полезный сигнал будет обнаружен в том случае, когда в К из И ранговых обнаружителей 2 будет принято решение о наличии сигнала, т.е. амплитуда сигнала в К-ом элементе 7 памяти превышает амплитуду сигналов в определенном количестве остальных элементов памяти. В этом случае на

К-ом выходе логического блока 3 бу.дет выработан запрещающий импульс, который подается на К-ые блоки 4 запрета, Формирователи б осуществляют выработку импульса сброса для установки в исходное состояние элементов

7 памяти. Причем, при отсутствии .обнаруженных сигналов поочередное обнуление элементов 7 производится непосредственно перед записью текущего значения входного процесса, При обнаружении полезного сигнала логическим блоком 3 при помощи формирователей б обеспечивается повторная установка в исходное состояние элемента 7 памяти, в котором присутствует сигнал, Входной процесс воздействует на первые входы вентилей 5. На вход регистра 8 подаются импульсы, под воздействием которых на выходах, например первого, второго и третьего разрядов регистра 8 последовательно во времени появляются импульсы, йодаваемые на вторые входы вентилей 5.

Задержанные импульсы сдвига, снимаемые с выхода элемента 1 задержки, подаются в качестве импульсов сброса на четвертые входы формирователей б, Задержка этих импульсов обусловлена необходимостью получения последовательности импульсов Й „, используемой для выработки импульсов сброса элементов 7 памяти, опережающей исходную последовательность f

Каждый К-ый элемент 7 памяти, в который записывается информация, должен быть предварительно обнулен, С этой целью используются импульсы с выхода формирователей б, При отсутствии полезного сигнала во входном колебании с помощью импульсов, снимаемых с выходов регистра 8, обеспечивается поочередное открывание вентилей 5 и запоминание текущего значения входного процесса в элементах 7 памяти, Таким образом, в элементах 7 памяти будет записана информация о входном процессе на некотором интервале наблюдения

Т„ц„ --- — . В каждый текущий момент времени йа каждый из элементов 7 памяти через распределитель 9 подается текущее выборочное значение входного процесса. В случае превышения текущим значением процесса значения, записанного в элементе 7 памяти, на выходе этого элемента 7 памяти будет единичный сигнал (т .е. будет присутствовать стандартный импульс), В противном случае выдается нулевой ,сигнал, Вследствие отсутствия полезного сигнала во входном колебании на интервале времени (t<, t<) результаты сравнения в каждом из r4 ранговых обнаружителей 2 будут пред734590

1Î

Формула изобретения ставлять случайный набор единиц и нулей, число которых можно считать примерно равным, В соответствии с используемым в устройстве ранговым критерием логика обнаружения выполняться не будет, Следовательно, сигнал обнаружения на выходе решающего блока 10 будет отсутствовать.

При наличии во входном колебании полезного сигнала до его обнаружения логическим блоком 3 происходит поочередное открывание вентилей 5 и запо минание текущего значения входного процесса в элементах 7 памяти. При этом в момент времени t предшествующий появлению полезного сигнала, формирователь 6 вырабатывает импульс, устанавливающий элемент, 7 памяти н исходное состояние. Появление импуль-. са с регистра 8 приводит к запоминанию амплитуды полезного сигнала н элементе 7 памяти. При выполнении логики обнаружения логический блок 3 вырабатывает импульс обнаружения, В результате воздействия этого импульса на третий вход формирователя

6, последний вновь вырабатывает в момент времени, импульс сброса, под воздействием которого элемент 7 памяти в этот момент времени не вырабатывается. Одновременно с соответствующего выхода логического блока 3 подается импульс на соответствующий блок 4 запрета, запоещая прохождение через него импульса сдвига. Поэтому длительность импульса на выходе данного разряда регистра 8 увеличится на величину Т=1/Е и, следовательно, в момент времени в элемент 7 памяти будет записано новое значение входного процесса.

При невыполнении логики обнаружения в этот и последующие моменты времени работа устройства будет продолжаться как приведено выше.

Применение предлагаемого устройства позволяет повысить вероятность правильного обнаружения сигналов за счет исключения из состава анализируемой выборки обнаруженного сигнала.

Благодаря такому исключению достигается равенство распределений анализируемых выборочных значений и, следовательно, рангового вектора будет равномерным.

3Q

3S

1. устройство для обнаружения сигналон, содержащее элемент задержки и первый ранговый обнаружитель, о т личаюшеесятем,что,с

Целью повышения вероятности правильного обнаружения, введены М-1 ранговых обнаружителей и логический блок, при этом входы М ранговых обнаружителей соединены с соответствующим из N в хxо д оoв л оoг иnч еeс к о г о o б л о к а, N + выходов которого соединены с соответствующим из N + 1 входов каждого .:из рангових обнаружителей,. (N+2) -ые входы которых соединены между собой и с входом элемента задержки, выход которого соединен с (N + 3)-м входом каждого из t1 ранговых обнаружителей.

2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что ранговый обнаружитель выполнен в ниде N каналов, каждый из которых содержит блок запрета, вентиль, формиронатель импульсов и элемент памяти, причем выход каждого предыдущего блока запрета соединен с первым входом последующего блока запрета и с одноименным входом регистра сдвига, N выходов которого соединены с первым входом вентиля канала и первым входом формирователя импульсов одновременного канала и вторим входом формирователя импульсов, соседнего с ним канала,выход вентиля каждого из N канадов соединен с элементом памяти этого же канала и с соответствующим из N входов распределителя импульсов, каждый из N выходов которого соединен с вторым входом элемента памяти одноименного канала, выход формирователя импульсов каждого из N каналов соединен с третьим входом элемента памяти одноименного канала, выход которого соединен с соответствующим и- N входов решающего блока, вторые входы вентилей каждого из N каналов соединены между собой,при этом второй вход соответствующего блока запрета является одноименным из N входов рангового обнаружителя, третьи входы формирователей соединены между собой и являются (N + 1) -ым входом рангового обнаружителя, (N + 2) -ым входом которого является первый вход первого блока запрета, четвертые входы формирователей соединены между собой и являются (N +3)-им входом рангового обнаружителя, выходом которого яв-. ляется выход решающего блока, Источники информации, принятые во внимание прн экспертизе

1. Авторское свидетельство. СССР

Р 535739, кл. Н 04 В 1/10, 1976 (прототип).

Вход и

Уая0

Составитель Т.Маркина

Редактор Н.Шильникова Техред Ж.Кастелевич ХорректорМ,вигула

Заказ 2217/8 Тираж 649 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35,. Раушская наб., д. 4/5

Филиал ППП Патент, г,Ужгород, ул,Проектная, 4