Встроенный мультиплексный канал

Иллюстрации

Показать всеРеферат

ОП ИКАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Совхоз Советских

Социалистических

Республик (!!)734649 (61) Дополнительное к авт. свид-ву— (22) Заявлено 06.12.77 (21) 2551069/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

G 06 Г 3/04

Гасударственный камитет до делам изобретений и атнрытий

Опубликовано15.05.80. Бюллетень № 18

Дата опубликования описания 25.05.80 (54) УДК 681.327 (088.8) (72) Авторы изобретения

P. И. Заславский и А. П. Шередин

Киевский ордена Трудового Красного Знамени (71) Заявитель завод электронных вычислительных и управляющих машин (54) ВСТРОЕННЫЙ МУЛЬТИПЛЕКСНЫЙ КАНАЛ

Изобретение относится к вычислительной технике и может быть использовано при конструировании мультиплексных каналов ввода-вывода встроенного типа, использующих в своей работе оборудование процессора.

Известен встроенный канал, содержащий регистр данных, регистр управляющего слова, соединенные по входу и выходу с инфОрмационной магистралью оперативной памяти, блок управления, соединенный с регистрами данных и управляющего слова (1).

Недостатком этого канала является загрузка процессора на все время логического подключения устройства к каналу.

Известен также мультиплексный .канал, содержащий информационный регистр, блок управления, ключи, элемент И причем первые входы ключей подключены к выходам информационного регистра, вторые входы ключей подключены к блоку управления, вход элемента И подключен к блоку управления (2) .

Недостатком этого канала является также загрузка процессора на все время логического подключения устройства к каналу.

Цель изобретения — расширение функциональных возможностей канала.

Указанная цель достигается тем, что в канал, содержащий информационный регистр, блок управления. ключи, первые входы которых подключены к первой группе выходов информационного регистра, вторые входы ключей подключены к блоку управления, первый элемент И, первый вход которого подключен к блоку управления, а щ второй вход первого элемента И подключен к шине управления интерфейса, вторая группа выходов информационного регистра и первая группа его входов являются соответственно входами и выходами канала, подключенными к информационной магистрали процессора, вторая группа входов информационного регистра является входами устройства, а выходы ключей — выходной информационной шиной интерфейса, управляющие входы информационного регистра и управляюшие входы блока управления являются входными шинами микроопераций процессора, дополнительно введены триггер, второй, третий и четвертый элементы И, первый и второй элементы ИЛИ, первый и

73464!) 10

15 го

2$ зо зз второй ипвсрторы, элемент ", täcðæêtt, причем первый вход первого элемента ИЛИ и вход элемента задержки обьединены с управляющими входами блока управления, второй вход первого элемента ИЛИ подключен к блоку управления, входы первого и второго инверторов подключены к шинам управления интерфейса, первый вход второго элемента И объединен со входом первого инвертора, а его второй и третий входы подключены соответственно к выходу элемента задержки и выходу второго инвертора, единичный вход триггера подключен к выходу второго элемента И, а его нулевой вход — к выходу первого элемента ИЛИ, первый вход третьего элемента И подключен к единичному выходу триггера, а его второй вход подключен к шине управления интерфейса, первый вход четвертого элемента И подключен к единичному выходу триггера. и его второй вход подключен к ны ходу первого и нвертора. входы второго элемента ИЛИ подключены к выходу третьего элемента И и первого элемента И.

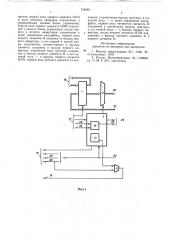

На фиг. и 2 при(3едена блоксхема.

С;сма устройства. содержит информационный регистр 1, клк>чи 2, блок 3 управления, первый элемент 4 И, второй элемент

5 И, третий элемент 6 И. четвертый элемент

7 И, первый элеме t3 8 И.1И, второй элемент

9 ИЛИ. первый инвертор (0, второй инвертор 11, элемен-, задер кки 12, триггер 13, триггер 14 управления передачей, триггер

15 занятости капала, информационная магист(таль 16 процессора, входные шины 17 мпкроопераций процессора, линии 18 условий ветвления процессора, линия 19 микропрерываний процессора, выходная информашц>нная шина 20 интерфейса, входы 21 устройств. выходные линии 22 управления интерфейса, линия 23 подтверждения приема-выдачи байта, входные шины 24 — 27 (тинии) управления интерфейса, линии 28 — 29 микроопераций процессора.

Устройство работает следующим образом.

1хогда канал свободен. триггер 15 нахо тится в нулевом состоянии и блок 3 управления вырабатывает сигнал выборки, который поступает в одну из линий 22 и последовательно опрашивает подключенные к интерфейсу внешние устройства (BY). То из них, которое готовое принять из канала либо передать в канал данные, устанавливает на шинах 21 свой адрес и вырабатывает сигнал управления установлением связи, который поступает в канал по линии 26.

От этого сигнала срабатывает первый элемент 4 И, (13ормиру3оццсй пс рвый сигнал микропрерывания, который проходит через второй элемент 9 ИЛИ и по линии !9 поступает в процессор. Последний, находившийся до этого момента и режиме с чета. переключается в режим ввод-вывода, и в работу вызывается мик(топрограмма обслуживания канала. В местной памяти сохраняется содержимое регистров процессора, используемых этой микропрограммой. Микропрограмма устанавливает триггер 15, который. оставаясь в единичном состоянии до момента прекращения связи с данными ВУ, блокирует на это время формирование сигнала выборки и повторное возбуждение первого сигнала микропрерывания. Затем в регистр

1 принимается с шин 21 адрес ВУ, который далее поступает по шинам 16 в процессор и используется там для формирования адреса управляющего слова устройства (УСУ) в памяти подканалов. УСУ содержит код операции (чтение или запись), а также адрес и счет, определяющие расположение данных в оперативной памяти. УСУ считывается из памяти подканалов и размещается в регистрах процессора. Блок 3 вырабатывает и устанавливает на одной из линий 22 сигнал подтверждения приема адреса ВУ.

Далее микропрограмма анализирует входной сигнал управления передачей данных по линии 25. С появлением этого сигнала производится прием либо выдача байта данных. Если выполняется операция чтения, байт данных с шин 21 принимается в регистр 1 и далее по магистрали 16 передается в оперативную память для зап33си.

Если выполняется операция записи, байт данных считывается из оперативной памяти, помещается в регистр 1 и через открытые ключи 2 устанавливается на шина.; 20. 3атем сигналом микрооперации на линии 28 устанавливается триггер 14. формирующий выходной сигнал управления передачей данных. Этот сигнал поступает в интерфейс по линии 23 и уведомляет внешнее устройство, что байт данных принят либо выдан каналом.

Одновременно производится коррекция на единицу адреса и счета в УСУ. Скорректированное УСУ возвращается в память подканалов, в регистрах процессора остается

его копия. После этого микропрограмма опять анализирует сигнал на линии 25. Когда он исчезнет, сигналом микрооперации на линии 29 сбрасывается триггер 14, сигнал на линии 23 снимается. Сис нал микрооперации на линии 29 поступает также через задержку 12 на вход второго элемента 5 И, формир(3ощего Ht Hà, Ibl ) ста нонки триггера 13.

Далее мпкроttð(!ãðàA!ìà анализирует сигналы на линияi 26, 27 и 25. Если BY установило связь с каналом для передачи одпог0 байта, (. ;. r(. л HB линии 26 снимается.

Задержка, »! .((.!.;:ая элементом 12, имеет такую вели ину. что сигнал на линии 26 снимается д(;At(!, как появится сигнал на выходе задержки. с.ле.(ов Зте.т»но, на входе

3 lEMQHT3 5 11 CO 3tH3;;. ННН !(«ча,l HE возникает и триггер 13 oc (;!ñ".(::. в ну.tct3(r..t состоянии. Микропрограх":ма: отсутс; вш > сигнала на линии 26 про3»(,«дпг сбр (с тппггера ! - г

1,.> и восстановле33пс: — рс 3д;ст р,", . пог»сессоI

73-1649

1S

3О

30

Формула изобретения

35 аа

55 ра информации, хранившейся та.; в момент микропрерывания. Процессор возвра LUàется в режим счета для продолжения вычислений, канал освобождается.

Если сигнал на линии 26 не успевает сброситься до появления сигнала на выходе задержки 1, срабатывает элемент 5 И и устанавливается триггер 13. По сигналу на линии 27 микропрограмма восстанавливает информацию в регистрах процессора, но не сбрасывает триггер 15. Процессор возврашается в режим счета, канал остается занятым. Когда сигнал на линии 26 снимается, сработает элемент 7 И, выходной сигнал которого сбрасывает триггер 15. Сигнал с нулевого выхода последнего проходит через элемент 8 ИЛИ и сбрасывает триггер 15.

Канал освобождается и устанавливается в исходное состояние.

Если BY установило связь с каналом для передачи в монопольном режиме группы байтов, сигнал на линии 26 сохраняется.

Сигнал на линии 25, которым запрашивается прием либо выдача следующего байта, может появиться до либо после возникновения сигнала на выходе задержки !2. Первый случай характерен для работы с относительно высокоскоростными BY, у которых период следования запросов соизмерим с временем, затрачиваемым каналом на передачу байта. В этом случае передача данных происходит без возврата процессора в режим счета. Срабатывание элемента 5 И блокируется нулевым уровнем на выходе второго инвертора 11, триггер 13 остается в нулевом состоянии. Восприняв сигнал на линии 25, микропрограмма выполняет передачу байта и сопутствующие действия.

Если быстродействие BY существенно ниже скорости канала в монопольном режиме, сигнал на выходе задержки 12 появляется до возникновения запроса на линии 25. B этом случае передача данных происходит с возвратом процессора в режим счета на время ожидания запроса. От сигнала на выходе задержки 12 срабатывает элемент

5 И и устанавливается триггер 13. По сигналу на линии 27 микропрограмма восстанавливает информацию в регистрах процессора, но не сбрасывает триггер 15. Микропрограмма также сохраняет в местной памяти текущее значение УСУ либо адрес памяти подканалов, где она хранится. Процессор возвращается в режим счета, канал остается занятым. Когда возникает сигнал на линии 25, сработает третий элемент 6 И, формирующий второй сигнал микропрерывания, который проходит через элемент 9 ИЛИ и по линии 19 поступает в процессор. Г1роцессор вновь переключается в режим ввода-вывода, микропрограмма обслуживания канала сохраняет содержимое регистров и далее, разветвившись по наличию сигнала на линии 27, выходит на продолжение монопольной передачи данных. На основании информации, храияшейся в местшгй памят;:., сть.

КНВНрТсН и помещается в регистры УСХ.

Затем выполняется передача байта и связанные с этим действия. Попутно сигнало .: микрооперации на линии 28 сбрасывается триггер 13.

Величиной задержки определяется граница диапазонов скоростей BY, которым соответствует монопольная работа с возвратом либо без возврата процессора в режим счета. В частности, при нулевой задержке всегда имеет место возврат. Конкретное значение задержки устанавливается B зависимости от скоростей передачи данных реальными ВУ с учетом времени, затрачиваемого каналом на передачу байта и сохранение-восстановление регистров и УСУ.

Предложенный канал обеспечивает экономию машинного времени при выполнении монопольной передачи данны. с внешними устройствами, что достигается переключением процессора в ре жим счета на время ожидания каждого очередного вопроса. ак. при быстродействии внешнего i стройства

64 тыс. байтов в секунду и пропускной способности канала 300 тыс. байтов в сe êóHëó экономится 79% времени выполнения опер,.ции ввода-вывода.

Предложенное техническое решение с с;— дает экономию машинного времени и в мультиплексном режиме работы в теi случаях, когда внешнее устройство разрывает связь с каналом с большим запаздыванием по отношению к моменту передачи байта данных.

Встроенный мультиплексный канал, содержаший ключи, первые входы Koropblx подключены к первой группе выходов информационного регистра, вторые входы ключей подключены к блоку управления, первый элемент И, первый вход которого подкгиочен к блоку управления, а второй вход первого элемента И, подключен к шине управления интерфейса, вторая группа выходов информационного регистра и первая группа его входов являются соответственно входами и выходами канала, подключенными к информационной магистрали процессора, вторая группа входов информационного регистра является входами устройства, а выходы ключей — выходной информационной шиной интерфейса, управляюший вход информационного регистра и управляющие входы блока управления являются входными шинами микроопераций процессора, отличающийгч тем, что, с целью расширения функциональных возможностей канала в него введены триггер, второй, третий и четвертый элементы И, первый и второй элемент И;1И, r!ервый и второй инверторы, элемент задержки, 734649 причем первый вход первого элемента ИЛИ и вход элемента задержки подключены к управляющим входам блока управления, второй вход первого элемента ИЛИ подключен к выходу блока управления, входы первого и второго инверторов подключены к шине управления интерфейса, первый вход второго элемента И соединен со входом первого инвертора, а его второй и третий входы подключены соответственно к выходу элемента задержки и выходу второго инвертора, единичный вход триггера подключен к выходу второго элемента И, а его нулевой вход — к выходу первого элемента

ИЛИ, первый вход третьего элемента И подключен к единичному выходу триггера, а его второй вход — к шине управления интерфейса, первый вход четвертого элемента И подключен к единичному выходу триггера, а его второй вход — к выходу первого инвертора, входы второго элемента ИЛИ подключены к выходу третьего элемента И и первого элемента И.

Источники информации, принятые во внимание при экспертизе

1. Каналы ввода-вывода ЕС вЂ 10, М., «Статистика», 1976.

2. Патент Великобритании № 1108804. кл. G 06 F 1971 (прототип).

734649

Фи 2-2

Составитель А. Ш м ид

Техред К. Шуфрич Корректор Г. Назарова

Тираж 751 Подписное

IlHHHllH Государственного комитета СССР по делам изобретений и открытий

I 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП сПатенть г. Ужгород, ул. Проектная, 4

Редактор О, Колесникова

Заказ 2219/IО