Адаптер канал-канал

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (111 734661

Скиоз Советских

Социвлистическкх

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 01.02.78 (21) 2575050/18 — 24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 15.05.80. Бюллетень № 18

G 06 F 3/04

Государстоеииый комитет

СССР (53) УДК681.14 (088.8) по делом изобретеиий и открытий

Дата опубликования описания 17.05.80 (72) Авторы изобретения

В. А. Исаенко, В. А. Калиничев и В. М. Тафель (71) Заявитель (54) АДАПТЕР КАНАЛ-КАНАЛ

Изобретение относится к вычислительной технике и, в частности, может использоваться как системное устройство для связи цифровых вычислительных машин (ЦВМ) в многомашинном вычислительном комплексе.

Известны устройства, позволяющие сопрягать ЦВМ машинного комплекса (1).

Однако обмен информацией между ЦВМ производится под непосредственным управлением процессором сопрягаемых UBM, ито значительно снижает производительность вычислительного комплекса.

Наиболее близким к изобретению по технической сущности является адаптер каналканал (устройство EC-4060), состоящий из буферного регистра, входами и выходом подключенного к двум идентичным блокам связи с каналом. Каждый блок связи с каналом обслуживает канал, подключенный к нему через интерфейс ввода-вывода и содержит узел входных сигналов, регистр команд, дешифратор команд, регистр адреса, узел сравнения адресов, узел управления, узел выход- 20 ных сигналов и регистр байта состояния.

Блок 4 связи с каналом соединены между собой несколькими управляющими линиями (2).

Недостатком этого устройства является снижение производительности вычислительного комплекса при межмашинном обмене за счет обязательного программного анализа кода команды, требующей согласования, и непроизводительных простоев мультиплексных каналов, участвующих в обмене.

Цель изобретения — повышение производительности вычислительного комплекса за счет сокращения непроизводительного времени при межмашинном обмене.

Поставленная цель достигается тем, что в адаптер, содержащий буферный регистр, два блока связи с каналом, каждый из которых содержит узел входных сигналов, регистр адреса, регистр команд, узел сравнения адресов, дешифратор команд, узел управления, регистр байта состояния, узел выходных сигналов, выход которого является первым выходом адаптера, первый вход узла выходных сигналов каждого блока связи с каналом объединен соответственно с первыми входами буферного регистра, выход которого подключен ко второму входу узла выходных сигналов в каждом из блоков связи с каналом, вход узла входных сигналов является первым входом устройства, а выход

734661 узла входных сигналов подключен к первому входу узла сравнения команд, первому входу узла выходных сигналов и первому входу регистра команд, выход которого соединен со входом дешифратора команд, выход которого соединен с первым входом узла управления, первый выход которого подключен к третьему входу узла выходных сигналов, четвертый вход которого соединен с выходом регистра байта состояния, вход которого соединен со вторым выходом узла управления, второй вход которого подключен к выходу узла сравнения адресов, второй вход которого соединен с третьим выходом узла управления, четвертые выходы узла управления в каждом из блоков связи с каналом соединены между собой, пятые выходы узла управления из каждого блока связи с каналом подключены соотвеТственно ко вторым входам буферного регистра, шестой выход узла управления является вторым выходом адаптера, седьмой выход узла управления соединен со вторым входом регистра команд, третий вход узла управления является вторым входом адаптера, третий вход узла сравнения адресов подключен к выходу регистра адреса, введены блок сравнения команд и блок задания режима, выходы которого подключены соответственно к четвертым входам узла сравнения в каждом из блоков связи с каналом, пятые входы узлов управления в каждом из блоков связи с каналом соединены с выходом блока сравнения команд, входы которого соединены соответственно с выходами регистров команд в каждом из блоков связи с каналом.

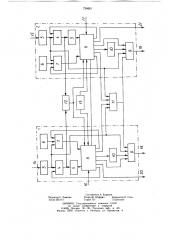

На чертеже приведена функциональная схема предлагаемого устройства.

Адаптер какал-канал состоит из двух блоков 1 и 2 связи с каналом, каждый из которых содержит блок 3 входных сигналов, регистр 4 команд, дешифратор 5 команд, регистр 6 адреса, блок 7 сравнения адресов, блок 8 управления, блок 9 выходных сигналов, регистр 10 байта состояния. Блоки связи с каналом соединены между собой несколькими управляющими линиями и через общие буферный регистр 11, блок 12 сравнения команд и блок 13 задания режима.

Адаптер связан с сопрягаемыми каналами с помощью информационных линий 14 и 15 каналов, управляющих линий 16 и 17 каналов, информационных линий 18 и 19 абонентов, управляющих линий 20 и 21 абонентов.

Адаптер работает следующим образом.

Канал (например, первый) выбирает адаптер в соответствии с принципами организации ввода-вывода. При этом адрес от канала по информационным линиям 14 канала через блок 3 входных сигналов поступает в блок 7 сравнения адресов для срав-. нения с адресом адаптера, хранимым в регистре 6 адреса. Результат сравнения адресов выдается в блок 8 управления. Если адреса совпадают, из блока 7 сравнения адресов выдается ответный адрес адаптера на информационные линии 18 абонента и далее в канал.

Регистр 4 команд и дешифратор 5 команд служат соответственно для хранения и декодирования команды, полученной из канала. После расшифровки команды первого канала, требующей соответствующей команды второго канала, адаптер помещает команду в буферный регистр 11 и выдает во второй канал байт состояния с указателем «Внимание», а ответ на который второй канал посылает в адаптер команду уточнения состояния. По этой команде адаптер передает второму каналу содержимое буферного регистра 11, т.е. команду, присланную первым каналом. Программа второго канала определяет, какая ответная команда долж24 на быть послана в адаптер, и затем посылает эту команду. После того, как обе команды приняты адаптером, продолжается их совместное выполнение до завершения. В отличие от известного в предлагаемом устройстве существует возможность устанавливать соответствие между командами каналов аппаратно с помощью блока 12 сравнения команд, что позволяет в некоторых случаях выполнять команды без программного анализа (например, независимый выход

Зо двух каналов на связь согласованными командами). Формат команды обмена содержит два поля: поле основной команды и поле модификаторов. Информация в поле основной команды определяет направление

3$ передачи данных (запись, считывание и т.д.) и расшифровывается как каналом, так и внешним устройством, Информация в поле модификаторов расшифровывается только внешним устройством и используется для модификации основной команды. В предла@ гаемом устройстве эта информация используется для установления ссютветствия между командами каналов. Сигнал соответствия вырабатывается на выходе блока 12 сравнения команд при совпадении информации в полях модификаторов команд каналов и поступает

os в блоки 8 управления обоих блоков связи с каналом. Если команды соответствуют друг другу (команде записи соответствует команда считывания с теми же модификаторами), адаптер выполняет их до завершения. При этом байт информации, полученный из канала, производящего запись, помещается в буферный регистр 11, а затем передается в канал, производящий считывание.

В том случае, если от канала поступает несогласованная команда, ему посылается байт состояния с указателем занятости, адаптер остается в ожидании согласованной команды.

Блок 8 управления вырабатывает внутренние управляющие сигналы и сигналы на

734661

5 линиях 20(21) управления абонента в соответствии с кодом команды, сигналами, поступающими из каналов по линиям 16(17) управления каналов,и сигналами, поступающими из блока 13 задания режима. В монопольном режиме выборка адаптера и передача всего массива информации производитS ся за один сеанс связи. В мультиплексном режиме после получения из мультиплексного канала (например, первый канал) команды, требующей согласования, и при условии, что от второго канала не поступает согласованная команда, адаптер помещает команду первого канала в буферный регистр

11 и отключается от первого канала. С этого момента первый канал может обмениваться с другими внешними устройствами.

После получения согласованной команды из второго канала адаптер выдает в первый канал сигнал требования на обслуживание и после установления связи с первым каналом передает весь массив информации на один сеанс связи.

Формирование разрядов регистра 10 байта состояния производится по сигналам блока 8 управления. Узел 9 выходных сигналов служит для выдачи на информациоНные линии 18(19) абонента адреса адаптера, байта состояния и данных. и

Предлагаемое устройство позволяет повысить общую производительность многомашинной вычислительной системы. в результате выполнения встречных согласованных команд каналов без прерывания работы

ЦВМ и возможности организации мультизо плексного режима межмашинного обмена.

Обмен в мультиплексном режиме особенно эффективен для систем, в которых ЦВМ обмениваются небольшими кадрами информации, так как в этом случае время межмашинного обмена соизмеримо с временем ожидания согласованной команды, и для управляющих систем, в которых недопустима задержка обмена с абонентами мультиплексного канала.

Формула изобретения

Адаптер канал-канал, содержащий буферный регистр, два блока связи с каналом, каждый из которых содержит узел входных сиг43 налов, регистр адреса, регистр команд, узел сравнения адресов, дешифратор команд, узел управления, регистр байта состояния, 6 узел выходных сигналов, выход которого является первым выходом адаптера, первый вход узла выходных сигналов каждого блока связи с каналом объединен соответственно с первыми входами буферного регистра, вь|ход которого подключен ко второму входу узла выходных сигналов в каждом из блоков связи с каналом, вход узла входных сигналов является первым входом устройства, а выход узла входных сигналов подключен к первому входу узла сравнения команд, первому входу узла выходных сигналов и первому входу регистра команд, выход которого соединен со входом дешифратора команд, выход которого соединен с первым входом узла управления, первый выход которого подключен к третьему входу узла выходных сигналов, четвертый вход которого соединен с выходом регистра байта состояния, вход которого соединен со вторым выходом узла управления, второй вход которого подключен к выходу узла сравнения адресов, второй вход которого соединен с третьим выходом узла управления, четвертые выходы узла управления в каждом из блоков связи с каналом соединены между собой, пятые выходы узла управления из каждого блока связи с каналом подключены соответственно ко вторым входам буферного регистра, шестой выход узла управления является вторым выходом адаптера, седьмой выход узла управления соединен со вторым входом регистра команд, третий вход узла управления является вторым входом адапетра, третий вход узла сравнения адресов подключен к выходу регистра адреса, отличаюи ийся тем, что с целью повышения быстродействия, в него введены блок сравнения команд и блок задания режима, выходы которого подключены соответственно к четвертым входам узла управления в каждом из блоков связи с каналом, пятые входы узла управления в-каждом из блоков связи с каналом соединены с выходом блока сравнения команд, входы которого соединены соответственно с выходами регистров команд в каждом из блоков связи с каналом.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Мо 525078, кл. G 06 F 3/04, 1975.

2. Антонов В. С. и Соловьев С. П. Электронная вычислительная машина ЕС вЂ” 1050.

М., «Статистика», 1976, (прототип).

734661

Составитель А. Баранов

Редактор С. Лыжова Техред К.Шуфрич Корректор Н. Стец

Заказ 2221/11 Тираж 751 Подпи сное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб.„д. 4/5 филиал ППП <Патент> г. Ужгород, ул. Проектная, 4