Преобразователь правильной двоичной дроби в двоично- десятичную дробь и целых двоично-десятичных чисел в двоичные

Иллюстрации

Показать всеРеферат

ЮО.". 4.

О Il И"С A. Н И Е 734669

ИЗОБРЕТЕН ИЯ

Совхоз Советскик

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 27.01.78 (21) 2574812/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

G06 F 5/02

Гееударстееннмй комитет

Опубликовано 15.05.80. Бюллетень № 18

Дата опубликования описания 17.05.80 до делам иэебретений и атнрытий (53) УДК 681.325 (088.8) (72) Автор изобретения

В. И. Омельченко

Таганрогский радиотехнический институт им. В. Д. Калмыкова (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ПРАВИЛЬНОЙ ДВОИЧНОЙ ДРОБИ

В ДВОИЧНО-ДЕСЯТИЧНУЮ ДРОБЬ И ЦЕЛЫХ ДВОИЧНОДЕСЯТИЧНЪ|Х ЧИСЕЛ В ДВОИЧНЫЕ

Изобретение отсносится к автоматике и вычислительной технике и может быть использовано при построении преобразующих устройств.

Известен преобразователь двоичного кода в двоично-десятичный, содержащий блок управления, переключатель эквивалентов, запоминающее устройство, два формирователя двоичных эквивалентов, два регистра сдвига, блок элементов И, шифратор и двоичный вычитатель (1).

Недостатком известного устройства яв- 1о ляется низкое быстродействие.

Наиболее близким к изобретению по технической сущности и схемному решению является преобразователь, содержащий двоично-десятичнй сдвигающий регистр, разделенный на и тетрад, где п — число двоично-десятичных разрядов преобразуемого числа, двоичный регистр, элемент И, блок управления коррекцией, блок коррекции, блок управления, одноразрядный суматор, выход которого соединен с входом младшей m тетрады сдвигающего регистра, выход которой соединен с первым входом одноразрядного сумматора, выход блока коррекции соединен с первым входом элемента И, вто2 рой вход которого соединен с выходом блока управления коррекцией, а выход элемента

И соединен со вторым входом одноразрядного сумматора (2).

Кроме того, известное устройство содержит дополнительный регистр, коммутатор кода операции, два-элемента задержки и группу элементов И.

Недостаток этого устройства — относительно низкая скорость преобразования, связанная с тем, что число проводимых коррекций пропорционально числу тетрад преобразуемого числа.

Цель изобретения — увеличение скорости преобразования.

Цель достигается тем, что коррекцию чисел осуществляют одноразрядные сумматоры, включенные в каждую преобразующую тетраду сдвигающего регистра. Предлагаемый преобразователь отличается тем, что дополнительно содержит (п — 1) одноразрядных сумматоров, (п — 1) блоков управления коррекцией, (и — 1) элементов И, входной и выходной коммутаторы, первые группы входов которых соединены с группой выходов блока управления, первый и второй выходы блока

734669

1о

tS го

30 и

4о

se

SS управления соответственно соединены со вторыми группами входов входного и выходного коммутаторов, выходы входного коммутатора соединены со входами двоичного регистра, выходы которого соединены с третьей группой входов выходного коммутатора, выход i-огo (i = - —:н) одноразрядного сумматора соединен со входом i-ой тетрады сдвигающего регистра, выход которой соединен с первым входом i-ого одноразрядного сумматора, второй вход i-ого одноразрядного сумматора соединен с выходом

i-ого элемента И, первый вход которого соединен с выходом (i — 1)-ого блока управления коррекцией, вторые входы всех элементов И соединены с выходом блока коррекции, второй выход (i — 1)-ой тетрады сдвигающего регистра соединен с первым входом

i-oro блока управления коррекцией, вторые входы всех блоков управления коррекцией соединены с третьим выходом блока управления, четвертый выход которого соединен с входом блока коррекции, первый выход первого блока управления коррекцией соединен с выходом выходного коммутатора, выход л-ой тетрады сдвигающего регистра соединен с третьей группой входов входного коммутатора.

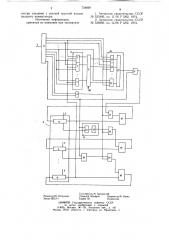

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство включает управляющую шину

1, блок 2 управления, двоично-десятичный сдвигающий регистр 3, разделенный на тетрады 4, шины 5 десятичной информации, входной коммутатор 6, элементы 7 И, блок

8 коррекции двоичный регистр 9, шины 10 двоичной информации, блоки 11 управления коррекцией, элемент 12 И, элемент 13 памяти, выходной коммутатор 14, элементы 15 и

16 И, элемент 17 ИЛИ, одноразрядные сум- маторы 18.

Управляющая шина 1 предназначена для пуска всего устройства в целом. Блок управления 2 вырабатывает признаки, и сигналы, необходимые для функционирования преобразователя. Двоично-десятичный сдвигающий регистр 3 хранит и сдвигает содержащуюся в нем информацию. Тетрады 4 сдвигающего регистра хранят исходную или промежуточную информацию. На чертеже они расположены в порядке убывания десятичных разрядов сверху вниз. Шины 5 десятичной информации- служат для записи информации, подлежащей преобразованию.

Входной коммутатор 6 предназначен для записи значения, появляющегося на выходе. младшего разряда младшей тетрады в каждом цикле преобразования. Блок 8 коррекции, представляющий собой двухвходовый элемент ИЛИ, вырабатывает код коррекции в каждом цикле преобразования. Двоичный регистр 9 хранит либо исходную двоичную дробь при прямом преобразовании, либо искомое двоичное число при обратном преобразовании. Шины 10 двоичной информации служат для записи преобразуемой

Ь двоичной дроби в двоичный регистр 9. Блоки 11 управления коррекцией:,вырабатывают признаки коррекции, если при сдвиге вправо из предшествующих (более старших) тетрад поступает перенос. Элементы 12 И. служат для записи переносов в элементы 13 памяти. Выходной коммутатор 14 передает и-разрядный код двоичного регистра 9 по одному разряду в каждом цикле преобразования. Элементы 16 И передают корректирующий код в зависимости от состояния блоков 11 управления коррекцией. Одноразрядные двоичные сумматоры 18 суммируют содержимое тетрад 4 сдвигающих регистров с корректирующим кодом.

Преобразование как правильной двоичной дроби так и целого двоичного-десятичного числа осуществляется методом сдвига исходного числа (а затеьг промежуточных результатов) на один разряд вправо с последующей одновременной коррекцией содержимого всех тетрад сдвигающего регистра, если из младшего разряда двоичного регистра или младшего разряда старшей тетрады поступает в блок управления коррекцией единица, являющаяся признаком коррекции.

Кодом коррекции является двоичное число

0101.

При преобразовании правильной двоичной дроби, в двоично-десятичную дробь по сигналу, поступающему с управляющей шины 1, запускается блок 2 управления, вырабатывающий потенциал двоичного преобразования и такты,. необходимые для сдвига и коррекции содержимого тетрад 4 двоичнодесятичного регистра 3. Одновременно ло шинам 10 двоичной информации записывается в двоичный регистр 9 исходная двоичная дробь. При этом i тетрад 4 и i одноразрядных двоичных сумматоров 18 образуют i последовательных сумматоров для сложения четырехразрядных чисел. В первых четырех тактах каждого цикла произ-. водится сдвиг содержимого всех тетрад 4 сдвигающего регистра на один разряд вправо и считывается младший разряд двоичного регистра 9. При этом этот разряд и переносы из предшествующих тетрад 4 запоминаются блоками 11 управления коррекцией.

В следующих четырех тактах производится одновременное суммирование содержимого всех тетрад 4 сдвигающего регистра с кодом

0101 (если признак коррекции 1) и установка в нулевое состояние всех старших разрядов тетрад 4 в пятом такте. По окончании первого цикла все тетрады 4 сдвигающего регистра хранят промежуточный результат.

Двоичный регистр 9 лишь хранит исходную двоичную дробь, а съем его разрядов (ло одному в каждом цикле) последовательно осуществляет выходной коммутатор 14, представленный трехвходовыми элементами 15 И и входовым элементом 17 ИЛИ. Вторые входы выходного коммутатора 14 опрашивают последовательно сигналы номера цикла, а

734669

3f разования, и необходимое число циклов и тактов в каждом цикле. Одновременно по шиhaM 5 десятичная информация записывается в тетрады 4 сдвигающего регистра (двоично-десятичное число). Сдвиг и коррекция содержимого двоично-десятичного сдвигающего регистра 3 осуществляется одновременно, для всех тетрад. При этом коррекции на третьи его входы- поступает признак дно ичного преобразования. Описанный процесс сдвига и коррекции производится п циклов по 8 тактов каждый. После окончания и циклов преобразования искомая двоичная-де сятичная дробь снимается с тетрад 4 сдвигающего регистра 3.

При преобразовании целого двоично-десятичного числа метод сдвига и коррекции заключается в том, что исходное двоичнодесятичное число сдвигается в сторону младшах разрядов с запоминанием разрядов переноса из младших разрядов каждой предшествующей тетрады в последующую (младшую) тетраду и записью единицы переноса младшей тетрады в двоичный регистр 9.

При этом те тетрады, в которых есть перенос, корректируются кодом 0101.

Работа в этом режиме производится следующим образом.

Сигнал, поступающий по управляющей шине 1, запускает блок 2 управления, вырабатывающий потенциал десятичного преобподлежат те тетрады, в схемах управления которых есть единица переноса из предыдущей тетрады. Информационный двоичный разряд, появляющийся на выходе младшей тетрады 4, записывается в младший разряд двоичного регистра 9. Описанный процесс сдвига вправо и коррекции на 0101 производит К циклов, с той лишь разницей, что значение выдвигаемого из младшей тетрады

4 разряда записывается в соответствующий разряд двоичного регистра 9 входным коммутатором 6, состоящим из и элементов 7 И.

Вторые и третьим входы опрашиваются сигналами номера цикла и потенциалом десятичного преобразования.

Для выявления технико-экономических показателей сравним предлагаемое устройство с известным по быстродействию. В обоих устройствах каждый сигнал преобразования обусловлен временем сдвига и коррекции, с той разницей, что время сдвига и коррекции в известном преобразователе прямо пропорционально числу тетрад двоично-десятичного регистра

Т вЂ” — 4 п.k-t + 4.п.Ы = 8.п.kt, где T» — время преобразования в прототипе;

i — число тетрад двоично-десятичного регистра; и — число циклов преобразования;

t — длительность тактирующего импульса;

4 — число разрядов тетрады.

Оценим время преобразования в предлагаемом устройстве

Т=4 И+-44 t =8-И. зз

SO

Выигрыш в быстродействии составит

В= — — =п раз т

Если число разрядов двоично-десятичного регистра равно 10, то скорость преобразования возрастает на порядок. Такое повышение быстродействия особенно важно, в случаях совмещения операций, когда производится решение одной задачи и готовятся данные для ввода другой задачи, что позволяет в целом повысить производительность специализированной вычислительной машины.

Формула изобретения

Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные, содержаший двоично-десятичный сдвигающий регистр, размеленный на п тетрад, где и — число двоично-десятичных разрядов преобразуемого числа, двоичный регистр, элемент И, блок управления коррекцией, блок коррекции, блок управления, одноразрядный сумматор, выход которого соединен с входом младшей тетрады сдвигающего регистра, выход которой соединен с первым входом одноразрядного сумматора, выход блока коррекции соединен с первым входом элемента

И, второй вход которого соединен с выходом блока управления коррекцией, а выход элемента И соединен со вторым входом одноразрядного сумматора, отличающийся тем, что, с целью увеличения скорости преобразования, он дополнительно содержит (и — 1) одноразрядных сумматоров, (и — 1) — блоков управления коррекцией, (n — 1) элементов И, входной и выходной коммутаторы, первые группы входов которых соединены с группой выходов блока управления, первый и второй выходы блока управления соответственно соединены со вторыми группами входов входного и выходного коммутаторов, выходы входного коммутатора соединены со входами двоичного регистра, выходы которого соединены с третьей группой входов выходного коммутатора, выход i-ого (i=2,n) одноразрядного сумматора соединен со входом

i-ой тетрады сдвигающего регистра, выход которой соединен с первым входом i-ого одноразрядного сумматора, второй вход

i-ого одноразрядного сумматора соединен с выходом i-oro элемента И, первый вход которого соединен с выходом (i — 1) -ого блока управления коррекцией, вторые входы всех элементов И соединены с выходом блока коррекции, второй выход (i — 1)-ой тетрады сдвигающего регистра соединен с первым входом i-ого блока управления коррекцией, вторые входы всех блоков управления коррекцией соединены с третьим выходом блока управления, четвертый выход которого соединен с входом блока коррекции, первый выход первого блока управления коррекцией соединен с выходом выходного коммутатора, выход и-ой тетрады сдвигаю цего ре734669 гистра соединен с третьей группой входов входного коммутатора.

Источники информации, принятые во внимание при эксепртизе

1. Авторское свидетельство СССР № 523406, кл. G 06 F 5/02, 1974.

2. Авторское свидетельство СССР

¹ 552266888855, кл.-G, 06 F 5/02, 1974.

Составитель М. Аршавский

Редактор Ю. Петрушко Техред К. Шуфрич Корректор М. Пожо

Заказ 2221/11 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4