Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

Ссиоз Советских

Социалистических

Республик ю 734687

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву K 439811 (22) Заявлено 28.11.77 (21) 2547395/18-24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 15.05.80. Бюллетень № 18 (5!) М. Кл.

G 06 F 9/16

Государственный комитет (53) УДК 681.326 (088.8) по делам изобретений и открытий

Дата опубликования описания 25.05.80 (72) Автор изобретения

В. В. Сыров

Ордена Ленина институт кибернетики АН Украинской ССР (71) Заявитель (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике.

Наиболее близким к данному изобретению техническим решением является микропрограммное устройство управления, содержащее первый блок памяти, дешифратор, выход которого через блок ключей соединен с выходом устройства, сумматор, выходом соединенный со входом дешифратора, блок управления сумматором, выходом соединенный с управляюшим входом сумматора, а входом — с первым выходом признаков блока ключей, генератор импульсов, выходом соединенный с управляющими входами блока ключей, коммутатор, выходами соединенный со входами первой группы элементов

ИЛИ, первая группа выходов которой соединена с соответствующими входами первого блока памяти, первая группа выходов которого соединена с первым входом сумматора, второй выход признаков блока ключей соединен с управляющим входом коммутатора, входы которого являются входами устройства (1) .

Принцип работы устройства заключается в том, что сумматор осуществляет сложение (вычитание) кода, считанного из блока памяти, с кодом предыдущей, уже реализованной микрокоманды. Полученный код дешифрируется, и на выходах ключей появляются управляюшие сигналы. Признаки выполняющихся микрокоманд поступают на логический коммутатор, который через блок схем ИЛИ осуществляет считывание кода из блока памяти, представляющего собой разность между кодом выполняющейся микрокоманды и кодом следуюшей микрокоманды. Количество отличающихся разностей ко 0 дов может быть при соответствующем кодировании достаточно малым, что дает возможность сократить объем памяти. Можно существенно уменьшить оборудование известного устройства, если принять во внимание следующее. Пусть в блоке памяти требует>s ся хранить N различных разностей разрядности п. Требуемый объем памяти при этом

W — — N n. Зададим некоторую разность

m < n. В этом случае все слова, хранящиеся в блоке памяти, можно разделить на две части N1,и N q с разрядностями и, и п 2, 20 причем п <тп и п,y па) m. Если хранить теперь N< слов в запоминающем устройстве разрядностью m, à Ма слов во втором запоминающем устройстве разрядностью и, то

734687

Таким образом, при обращении к блоку памяти 9 считанный m-разрядный код поступает на второй вход сумматора 1 через вторую группу элементов ИЛИ 10. При обращении к блоку памяти устройства 8 старшие (и — m) разрядов поступают на первый вход сумматора 1 непосредственно, а младшие m разрядов через вторую группу элемен тов ИЛИ 10.

Выборка разностей кодов из блоков памяти осуществляется путем подачи сигнала от многовыходных последовательных схем коммутатора 5 через элементы ИЛИ блока

4 первого или второго блоков памяти. На входы схем, управляющих выборкой кодов из запоминающих устройств, по шинами, подключенным ко входу 11, поступают признаки условных переходов, а по шинам 12 от схем И-ИЛИ блока 3 — признаки выполняющихся микрокоманд. Признак выполнения той или иной микропрограммы, поступающей по шинам, подключенным ко входу

13, выбирает для работы ту или иную схему коммутатора 5.

4$

$e

$$ суммарный объем памяти в этом случае потребуется

W = N m+ N$,-п, вегда Wa (Ъ » и выигрыш в объеме памяти равен

W< — Ъ а = N (n — m).

Целью изобретения является увеличение быстродействия устройства.

Поставленная цель достигается тем, что устройство содержит второй блок памяти и вторую группу элементов ИЛИ, первые входы которых соединены со второй груп- $о пой выходов первого блока памяти, а вторые входы — с выходами второго блока памяти, выход второй группы элементов ИЛИ соединен со вторым входом сумматора, входы второго блока памяти соединены со второй группой выходов первой группы элементов ИЛИ.

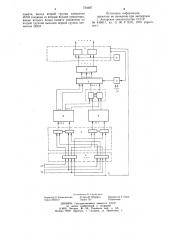

На чертеже представлена блок-схема устройства.

Устройство содержит сумматор 1, дешифратор 2, блок ключей 3, первую группу элементов ИЛИ 4, коммутатор 5, генератор импульсов 6, блок управления сумматором

7, первый и второй блоки памяти 8, 9, вторую группу элементов ИЛИ 10.

Устройство работает следующим образом. ы

Сумматор 1 осуществляет суммирование (вычитание) кода, поступающего из блока памяти, с кодом предыдущей, уже реализованной микрокоманды. При этом второй блок памяти 9 хранит разности микрокоманд, для кодирования которых достаточно m (п разрядов, где п — количество разрядов, необходимое для представления кода максимальной разности между двумя следующими друг за другом микрокомандами. Первый блок памяти 8 хранит остальные и-разрядные коды.

Через блок 7 последние микрокоманды каждой микропрограммы устанавливают сумматор 1 в нулевое состояние.

Последней микрокомандой выполненной микропрограммы устройство устанавливается в исходное состояние. На выходе дешифpampa 2 сигналы отсутствуют. Поступающий на вход 15 устройства признак выполнения опеределенной микропрограммы включает в работу соответствующую схему коммутатора 5, которая через элементы ИЛИ блока 4 выдает сигнал на один из выходов первой группы. Из блока памяти 8 считывается код первой микрокоманды, который подается на счетные входы триггеров сумматора

1 (младшие разряды через элементы ИЛИ блока 10), складывается с нулевым кодом, хранящимся в сумматоре, и с его выхода поступает на входы дешифратора 2. С приходом тактового импульса от генератора 6 микрокоманда с выходов блока 3 поступает на выход устройства. Признаки выполняющихся микрокоманд с выхода блока 3 по шинам

12 поступают на коммутатор 5. На выходе коммутатора 5 появляется сигнал, который по одному из выходов второй группы осуществляет считывание кода из первого блока памяти или второго блока памяти 9 соответственно

При этом считанный код представляет . собой разность между кодом выполняющейся микрокоманды и кодом следующей микрокоманды. Сумматор 1 осуществляет сложение (вычитание) и формирует код следующей микрокоманды. Полученный код дешифрируется, и после прихода тактового импульса на выходе устройства появляются управляющие сигналы. Такие процессы продолжаются до тех пор, пока на выходах устройства не появляются признаки последней микрокоманды. Они поступают на блок 7, на управляющие входы которого со входа 13 устройства подается признак выполнения данной микропрограммы. С выхода блока 7 снимается сигнал установки сумматора 1 в нулевое состояние.

Выигрыш в общем объеме микропрограммной памяти в устройстве по сравнению с известным, содержащим один блок памяти, будет тем больше, чем больше величина

N i (п —;m), где N — количество m-разрядных кодов, хранящихся во втором блоке памяти, а и-разрядность сумматора и кода в первом блоке памяти.

Формула изобретения

Микропрограммное устройство управления по авт. св. № 439811, отличающееся тем, что, с целью увеличения быстродействия устройства, оно содержит второй блок памяти и вторую группу элементов ИЛИ, первые входы которых соединены со второй группой выходов первого блока памяти, а вторые входы — с выходами второго блока

734687

Составитель В. Евстегнеев

Редактор О. Колесникова Техред К. Шуфрич Корректор Е. Папи

Заказ 2223/12 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Г1атент», г. 1 жгород, ул. Проектная, 4 памяти, выход второй группы элементов

ИЛИ соединен со вторым входом сумматора, входы второго блока памяти соединены со второй группой выходов первой группы элементов ИЛИ. ( (Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Хо 439811, кл. G 06 F 9!16, 1974 (прототип) .