Устройство для проверки функционирования цифровых схем

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Совхоз Советских

Социалистических

Республик ()734693 (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.01.78 (21) 2567885/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл 2

G 06 F 11/04

Гееудеротееииый комитет

СССР (53) УДК 681.325 (088.8) Опубликовано 15.05.80. Бюллетень № 18

Дата опубликования описания 25.05.80 ао делам изобретений и открытий

3. С. Джоджуа и А. А. Кванталиани (72) Авторы изобретения (71) Заявитель

Тбилисское научно-производственное объединение «ЭЛВА» (54) УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ФУНКЦИОНИРОВАНИЯ

ЦИФРОВЫХ СХЕМ

Изобретение относится к вычислительной технике и предназначено для функционального и параметрического контроля цифровых схем.

Известно программное устройство для обнаружения неисправностей в цифровых вычислительных машинах, содержащее блок коммутации, блок анализа и регистрации сигналов, матрицы регистрации сигналов, дешифратор, счетчик, блок выдачи контрольных кодов, блок управления и блок ввода (1).

Недостаток этого устройства — низкая достоверность контроля.

Наиболее близким по техническому решению к изобретению является устройство для проверки функционирования логических схем, содержащее блок ввода данных, блок входных и эталонных выходных сигналов, блок сравнения, блок индикации, блок управления, коммутатор, блок контролируемых выходов, блоки контрольных регистров, при 1 этом блок ввода данных соединен с входом блока входных и эталонных выходных сигналов, выполненного в виде магазинного запоминающего устройства, выход которого подключен через коммутатор сигналов к конт ролируемой логической схеме и через блок сравнения к блоку индикации, выходы блока управления подключены к блоку ввода данных, блоку входных и эталонных выходных сигналов, коммутатору и к блоку индикации, блок контролируемых выходов, выполненный в виде магазинного запоминающего устройства переменного объема, блоки контролируемых выходов, подключенные к второму входу схемы сравнения, один выход — к выходу блока ввода, другой — к выходу блока управления, вход одного блока контрольных регистров подключен к выходу блока входных и эталонных выходных сигналов, а вход другого блока контролируемых выходов, выходы блока контрольных регистров подключен к соответствующим входам блока индикации и к входам блока управления, управляющие входы которого соединены с выходами блока управления, а выходы сравнения — к соответствующим выходам блока ввода (2).

Недостатками известного устройства является ограниченная область применения и недостаточный уровень автоматизации.

734693

Цель изобретения — увеличение быстродействия и расширение класса решаемых задач.

Эта цель достигается тем, что в устройство, содержащее блок ввода, блок памяти, блок управления, коммутаторы, блок сопряжения, блок эквивалентных нагрузок, аналого-цифровой преобразователь, блок сравнения, причем вход блока ввода является входом устройства, первый выход блока управления подключен к первым входам блока эквивалентных нагрузок, блока сопряжения, блока сравнения и первого коммутатора, второй выход блока управления подключен к первому входу блока регистрации, второй вход которого соединен с выходом блока сравнения, первый вход блока сопряжения подключен к выходу второго коммутатора, второй вход блока сопряжения подключен к выходу блока эквивалентных нагрузОк, введены программные формирователи параметров, блок памяти и формирователи напряжения, причем каждый программный формирователь параметров содержит регистр и цифроаналоговые преобразователи, при этом входы цифроаналоговых преобразователей подключены к выходу регистра, второй выход блока управления подключен к входу регистра и к соответствующему входу каждого цифроаналогового преобразователя, выходы которых подключены ко второму входу второго коммутатора, третий, четвертый и пятый входы которого соединены с выходами соответствующих программных формирователей параметров, первые входы которых подключены к входу блока ввода, к первому выходу блока памяти и к первым входам каждого формирователя напряжений, каждый из которых содержит регистр и цифроаналоговый преобразователь, причем вход регистра является первым входом формирователя напряжений, вторые входы формирователей подключены к первому входу блока управления, выход регистра формирователя напряжения соединен со входом цифроаналогового преобразователя формирователя напряжения, выход каждого цифроаналогового преобразователя является выходом каждого формирователя напряжения, выход каждого формирователя напряжения подключен к соответствующим входам первого коммутатора, выход которого соединен с третьим входом блока сопряжения, первый выход которого подключен ко входу проверяемой схемы, выход которой соединен с четвертым входом блока сопряжения, второй выход которого соединен с первым входом аналого-цифрового преобразователя, второй вход которого подключен к первому выходу блока управления, выход аналогоцифрового преобразователя соединен со вторым входом блока сравнения, третий вход которого подключен ко второму входу блока эквивалентного напряжения и ко второму выходу блока памяти.

1»

29

И

3$

46

»5

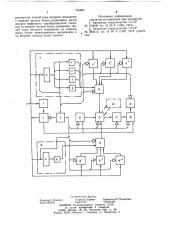

На чертеже представлена схема предложенного устройс;ва.

Устройсгво содержит блок 1 ввода (программный); блок 2 памяти, блок 3 управления, программные формирователи 4, 4, 4" и 4 " параметров, каждый из которых содержит цифроаналоговый преобразователь; циф роаналоговый преобразователь 5, служащий в качестве цифроуправляемого источника напряжения высокого уровня (+- 5 — 15 В); цифроаналоговый преобразователь 6 в качестве цифроулравляемого источника напряжения низкого уровня (+Π— 5 В); цифроаналоговый 7 преобразователь, служащий в качестве цифроуправляемого источника тока; цифроаналоговый преобразователь 8, служащий в качестве цифроуправляемого сопротивления; регистр 9; формирователи

10, 10, 10" и 10 " напряжения, каждый из которых содержит регистр 11, цифроаналоговый преобразователь 12, служагций в .качестве цифроулравляемого источника напряжения высокого уровня (+.5 — 15 В), коммутаторы 13 и 14, блок 15 сопряжения, блок

16 эквивалентных нагрузок, аналого-цифровой преобразователь 17, блок 18 сравнения, блок 19 регистрации, проверяемую схему 20.

Блок 1 ввода подключен к блоку 2 памяти, информационные шины которого подсоединены к программным формирователям

4, 4, 4" и 4 " параметров, формирователи питания 10, 10, 10" и 10 " — к блоку 16 эквивалентных нагрузок и блоку 18 сравнения.

Блок 3 управления подсоединен ко всем блокам устройства, кроме проверяемой схемы. Регистр 9 подсоединен к блоку 2 памяти.

Выходные шины регистра 9 подсоединены к цифроаналоговым преобразователям 5 — 8 программного формирователя параметров, выходы которых в виде выхода программного формирователя параметров через коммутатор 14 и блок 15 сопряжения подключаются ко входам проверяемой схемы.

Аналогично выходы программных формирователей параметров 4, 4" и 4 " подсоединены к проверяемой схеме 20. Входы регистра ll подсоединены к входам блока

2 памяти, а его выход ко входам цифроаналогового преобразователя 12. Выход 12. т. е. формирователи 10 напряжений, через коммутатор 13 и блок 15 сопряжения соединен с входами проверяемой схемы 20. Аналогично формирователи 10, 10" и 10 " напряжения подключаются к проверяемой схеме 20.

Блок 15 подключен к блоку 16 эквивалентных нагрузок, а через аналого-цифровой преобразователь 17 и блок 18 сравнения связан с блоком !9 регистрации.

Устройство работает следующим образом.

Кнопкой «Сброс» предварительно производится очистка всех операционных устройств комплекса. Затем нажатием кнопки

«Пуск» на пульте управления (на чертеже

734693

5 не показан) производится запись исходных данных с блока 2 памяти в регистровую память (на чертеже не показана). После этого производится последовательно выборка из блока 2 памяти кодовой информации, соответствующей параметрам воздействия.

Данная информация поступает на регистры Формула изобретения программных формирователей 4, 4, 4" и

4» параметров. Последовательность поступления этой информации управляется с блока

3 управления. С помощью цифроаналоговых преобразователей на выходах блоков 4, 4, 4 и 4 " вырабатываются требуемые параметры

Коммутатор 14, управляемый блоком 3 управления, обеспечивает подачу выработанных сигналов с выходов формирователей 4, 4, 4" и 4 " параметров на соответствующие входы проверяемой схемы через блок 15 сопряжения.

Уровни питания вырабатываются в формирователях 1О, 10, 10 " и 10 " напряжения, в которые поступает кодовая информация из блока 2 памяти. В упомянутых блоках с помощью цифроаналоговых преобразователей (например, 12) вырабатываются уровни питания, которые аналогично параметрам воздействия через коммутатор 13 и блок 15 сопряжения подаются на входы питания проверяемой схемы.

zs

Кроме вышеуказанных функций коммутаторы 13 и 14 определяют программно входы и выходы проверяемого объекта.

Кодовая информация, соответствующая эквивалентным нагрузкам, из блока 2 па-. мяти поступает в блок 16 эквивалентных нагрузок, где формируется соответствующая величина активной нагрузки.

Таким образом, предлагаемое устройство подготовлено к режиму контроля проверяемой схемы. В устройстве предусмотрено два з$ режима контроля работоспособности объекта: во-первых, проверка «до конца», т. е. проверка параметров на всех выходах проверяемого объекта с фиксацией ошибок, вовторых, проверка «до обнаружения первой ошибки». Соответствующие режимы ус- 40 танавливаются на пульте управления с помощью переключателей.

Проверка сигналов на выходах объекта производится последовательно.

Цифровое значение фактического параметра, полученное с аналого-цифрового пре4$ образователя 17, на выходе объекта сравнивается с эталонным значением в схеме

18 сравнения. При несовпадении соответствующих кодов- фиксируется номер выхода, признак «Не годен», номер входного алфа- $o вита и т. д. в блоке 19 регистрации.

В случае неисправности всех выходов проверяемого объекта режим проверки заканчивается индикацией (регистрацией) «Годен».

Использование предложенного устройства позволяет снизить срок разработки средств вычислительной техники, повысить

6 качество изделия и уменьшить номенклатуру контрольно-диагностической аппаратуры, необходимой для производства средств вычислительной техники.

Устройство для проверки функционирования цифровых схем, содержащее блок ввода, блок памяти, блок управления, коммутаторы, блок сопряжения, блок эквивалентных нагрузок, аналого-цифровой преобразователь, блок сравнения, причем вход блока ввода является входом устройства, первый выход блока управления подключен к первым входам блока эквивалентных нагрузок, блока сопряжения, блока сравнения и первого коммутатора, второй выход блока управления подключен к первому входу блока регистрации, второй вход которого соединен с выходом блока сравнения, первый вход блока сопряжения подключен к выходу второго коммутатора, второй вход блока сопряжения подключен к выходу блока эквивалентных нагрузок, отличающееся тем, что с целью увеличения быстродействия и расширения класса решаемых задач, в устройство введены программные формирователи параметров, блок памяти и формирователи напряжения, причем каждый программный формирователь параметров содержит регистр и цифроаналоговые преобразователи, при этом входы цифроаналоговых преобразователей подключены к выходу регистра, второй выход блока управления подключен к входу регистра и к соответствующему входу каждого цифроаналогового преобразователя выходы которых подключены ко второму входу второго коммутатора, третий, четвертый и пятый входы которого соединены с выходами соответствующих программных формирователей параметров, первый входы которых подключены ко входу блока ввода, к первому выходу блока памяти и к первым входам каждого формирователя напряжений каждый из которых содержит регистр и цифроаналоговый преобразователь, причем вход регистра является первым входом формирователя напряжений, вторые входы формирователей напряжения подключены к первому выходу блока управления, выход регистра формирователя напряжения соединен со входом цифроаналогового преобразователя формирователя напряжения, выход каждого цифроаналогового преобразователя является выходом каждого формирователя напряжения, выход каждого формирователя напряжения подключен к соответствующим входам первого коммутатора, выход которого соединен с третьим входом блока сопряжения, первый выход которого подключен ко входу проверяемой схемы, выход которой соединен с четвертым входом блока сопряжения, второй выход которого соединен с первым входом аналого-цифрового преоб734693

Составитель Н. Быкова

Техред К. Шуфрич Корректор Ю. Макаренко

Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент> г. Ужгород, ул. Проектная, 4

Редактор С. Лыжова

Заказ 2223/12 разователя, второй вход которого подключен к первому выходу блока управления, выход аналого-цифрового преобразователя соединен со вторым входом блока сравнения, третий вход которого подключен ко второму входу блока эквивалентного напряжения и ко второму выходу блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 370609, кл. G 06 F 11/04, 1973.

2. Авторское свидетельство СССР № Ь54415, кл. G 06 F 11/00, 1972 (прототип).