Система для обработки данных в реальном масштабе времени

Иллюстрации

Показать всеРеферат

ю

q у Т;,=;,,:... ";, 11

g- о на А

ИЗОБВЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублик (11)734698 (61) Дополнительное к авт. свид-ву— (22) Заявлено 10.01.78 (21) 2587768/18-24 с присоединением заявки №вЂ” (51) М. Кл.

G 06 F 15/16 (23) Приоритет—

Госудерстеенный комитет

Опубликовано 15.05.80. Бюллетень ¹ 18

Дата опубликования описания 25.05.80 (53) УДК 681.323 (088.8) по делам изобретений и открытий (72) Авторы изобретения

E. А. Дроздов, С. В. Назаров и В. А. Титов (71) Заявитель (54) СИСТЕМА ДЛЯ ОБРАБОТКИ ДАННЫХ В РЕАЛЬНОМ

МАСШТАБЕ ВРЕМЕНИ

Изобретение относится к вычислительной технике.

Известна вычислительная система, содержащая управляющую и управляемые вычислительные машины, группы элементов И, дешифратор, регистр управления, коммутатор, регистр приращений. В этой системе обеспечивается независимое решение отдельных задач в отдельных вычислительных машинах, которое предусматривается программой управляющей машины (11.

Однако данная система не может работать в реальном масштабе времени.

Наиболее близкой по технической сущности к изобретению является система для обработки данных, содержащая устройство для обмена данными, соединенное двусторонними связями с цифровой вычислительной машиной и периферийными устройствами, формирователь задержки и формирователь циклов решения задачи, входы которого подключены к управляющему входу системы и выходу формирователя задержки, . выход соединен со входом формирователя задержки и с управляющим входом цифровой вычислительной машины (2).

В реальных системах управления процессами имеются задачи, решение которых проводится с различными циклами, а также задачи, решение которых происходит не в реальном масштабе времени (например, задачи контроля и самодиагностики подсистем системы управления процессом и др.). При этом значительно усложняется операционная система, и вычислительные мощности используются неэффективно. Кроме этого, система малонадежна, так как при неисправности любого блока в системе из строя выходит вся система. Применение дублирования в системе приводит к неоправданному росту объема оборудования.

Цель изобретения — повышение надежности и эффективности использования оборудования.

Поставленная цель достигается тем, что в систему, содержащую устройства обмена, каждое из которых соединено двусторонними связями с периферийным устройством

20 и с соответствующей вычислительной машиной, введены генератор тактовых импульсов, управляющий процессор и формирователи циклов по числу вычислительных машин, причем первый и второй входы формирователей

734698 циклов соединены соответственно с выходом управляющего процессора и с выходом генератора тактовых импульсов, выход каждого формирователя циклов соединен со входом соответствеющей вычислительной машины, каждое устройство обмена соединено двусторонними связями с управляющим процессором.

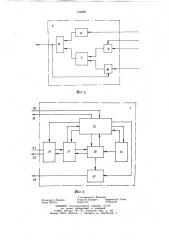

Кроме того, в системе формирователь циклов содержит схему. сравнения, элементы И, ИЛИ, счетчик тактов и регистр, выход которого подключен к первому входу схемы сравнения, второй вход которой соединен с выходом счетчика тактов, выход схемы сравнения соединен с выходом формирователя циклов и с первым входом элемента ИЛИ, входы счетчика тактов соединены соответственно с выходами элемента ИЛИ и элемента И, вход регистра, первый вход элемента И, второй вход элемента ИЛИ соединены с первым входом формирователя циклов, второй вход элемента И подключен ко второму входу формирователя циклов.

Это дает возможность осуществлять рещение задач с различными циклами, что существенно снижает сложность операционной системы, время ее работы по организации вычислительного процесса, тем самым повышая эффективность использования оборудования, а также возможность в динамике функционирования системы перераспределять нагрузку между исправными машинами в случае выхода из строя одной (или несколь25 зо ких) из них. Это достигается благодаря централизованному управлению в системе, при котором циклы решения задач могут меняться управляющим процессором в динамике

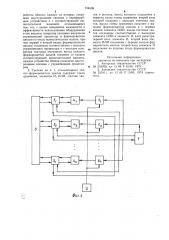

На фиг. 1 представлена структурная схема си стем ы; н а ф и г. 2 — структур н а я схем а формирователя циклов; на фиг. 3 — пример схемы реализации управляющего процессора.

Система содержит управляющий процессор 1, генератор 2 тактовых импульсов, периферийное устройство 3, вычислительные машины 4 — 4n, устройства 5 — 5n обмена, формирователи 6 < — 6n циклов, счетчик 7 тактов, регистр 8, элемент 9 И, элемент 10 ИЛИ, схема 11 сравнения, устройство 12 управления, арифметическое устройство 13, постоянное запоминающее устройст40

45 во (ПЗУ) 14 для хранения управляющих программ, оперативная память 15, коммутатор !

6 и выходной регистр 17, выходы 18 и 19, .подключаемые к формирователям циклов, входы 20 и 21 и выход 22, подключаемые к устройствам обмена.

Функционирование системы определяется управляющими программами, записанными в ПЗУ процессора 1, и сигналами, поступающими в устройство 12 управления, процессора 1 от устройств обмена. Коммутатор

16 по сигналам устройства управления проработы системы путем смены кода в регистре.

35 цессора обеспечивает обмен информацией между вычислительными машинами через оперативную память!5. При выходе из строя некоторой вычислительной машины обеспечивается передача задач, решаемых на ней, на другие машины. Осуществляется это через коммутатор 16 и оперативную память 15.

При этом меняется цикл решения задач в исправных вычислительных машинах путем выдачи в их формирователи 6 новых кодов с выходного регистра 17 управляющего процессора 1.

Система работает следующим образом.

Управляющий процессор 1 в исходном состоянии системы устанавливает на регистры 8 формирователей циклов коды, соответствующие циклам работы вычислительных машин. Этот код соответствует некоторому целому числу тактовых импульсов генератора 2 и составляет цикл решения всех задач. Инициация работы вычислительной машины происходит от управляющего процессора 1 путем подачи управляющего сигнала на устройство 5 обмена. Этот же сигнал подается и на вход элемента 10 ИЛИ формирователя 6 циклов, тем самым сбрасывается в нулевое состояние счетчик 7 тактов. На вход элемента 9 И от управляющего процессора 1 подается разрешающий сигнал, а на второй вход элемента 9 И поступают импульсы с генератора 2. Таким образом начинается цикл работы вычислительной машины. Счетчик 7 тактов формирователя 6 начинает отсчет импульсов, поступающих с генератора 2 через элемент 9 И. Б схеме 11 сравнения происходит сравнение содержимого счетчика 7 с кодом, установленным на регистре 8. Импульс сравнения этих кодов передается на вычислительную машину и сбрасывает в нулевое состояние счетчик 7, таким образом формируется цикл решения задач.

Обмен информацией (при необходимости) отдельными вычислительными машинами в системе происходит посредством управляющего процессора 1, оперативная память которого рассматривается как общая оперативная память системы. При решении задач не в реальном масштабе времени управляющий процессор 1 прекращает подачу разрешающего сигнала на вход элемента 9 И и устанавливает код на регистре 8, отличный от кода на счетчике 7 тактов.

Цикл решения задач может меняться в динамике управления процессом путем смены кода в регистре. Это свойство системы может быть использовано для оперативного перераспределения решаемых задач в случае выхода из строя любой вычислительной машины, тем самым для повышения надежности в системе не требуется дублирования аппаратуры.

Формула изобретения

1. Система для обработки данных в реальном масштабе времени, содержащая уст734698

5 ройства обмена, каждое из которых соединено двусторонними связями с периферийным устройством и с соответствующей вычислительной машиной, отличающаяся тем, что, с целью повышения надежности и эффективности использования оборудования в нее введены генератор тактовых импульсов управляющий процессор и формирователи циклов по числу вычислительных машин, причем первый и второй входы формирователей циклов соединены соответственно с выходом управляющего процессора и с выходом генератора тактовых импульсов, выход каждого формирователя циклов соединен со входом соответствующей вычислительной машины, каждое устройство обмена соединено двусторонними связями с управляющим процессором.

2. Система по п. 1, отличающаяся тем, что формирователь циклов содержит схему сравнения, элементы И, ИЛИ, счетчик так6 тов и регистр, выход которого подключен к первому входу схемы сравнения, второй вход которой соединен с выходом счетчика тактов, выход схемы сравнения соединен с выходом формирователя циклов и с первым входом элемента ИЛИ, входы счетчика тактов соединены соответственно с выходами элемента ИЛИ и элемента И, вход регистра, первый вход элемента И, второй вход элемента ИЛИ соединены с первым входом фор мирователя циклов, второй вход элемента И подключен ко второму входу формирователя циклов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

2. Авторское свидетельство СССР № 523411, кл. G 06 F 15/00, 1974 (прототип) .

734698

4 иг 2

Составитель А.Жеренов

Редактор С. Лыжова Техред К.Шуфрич Корректор Е. Папп

Заказ 2223/12 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4