Цифровой интегратор

Иллюстрации

Показать всеРеферат

ОП И

ИЗОБ

К АВТОРСКО

Союз Советских

Социалистических республик (1 1)7<34745 (6! ) ?????????????????????????? (22) ???????????????? 1 ??. 0 (51) m. ????, g 06 3>

Государственный комитет (23) Приоритетйо делам изобретений н открытий

Опубликовано

Дата опубли (53) УДК 681.14 (088. 8) (72) Авторы изобретения

E. E. Едиткин и P. Е. Пекуровская (71) Заявитель (54) ЦИФРОВОЙ ИНТЕГРАТОР

Изобретение относится к цифровым дифферейциальным анализаторам и пред назначено для использования в устрой . ствах вычислительной техники, в частности в системах автоматического регу лирования.

Известны цифровые интеграторы, со» держащие регистр остатка, сумматоры, регистры подынтегральный функции, умножители $1j.

Недостатком известных устройств является значительная конструктивная сложность

Наиболее близким по технической сущности к данному изобретению является цифровой интегратор, содержащий генератор тактовых импульсов, соеди» ненный с IIBpBbIMH входами формирова теля переполнений и генератора сдвиговых имтгулъсов, выход которого соединен с первыми входами регистра подйнтегрального выражения и накопительного регистра, выход регистра подынФ тегрального выражения соединен с первым входом первого сумматора, вьгход которого подключен ко второму входу накопительного регистра, первый выход накопительного регистра соединен со вто рым входом первого сумматора, а вто5 рой выход - со вторым входом формиро вателя переполнений, выход которого соединен через элемент задержки с третьим входом накопительного регистра, . второй вход генератора сдвиговых импуль

1О сов и третий вход первого сумматора HB ляются управляющими входами устройст ва (21.

Однако такой интегратор не позволяет производить интегрирование переменно 5 го подынтегрального выражения.

Бель изобретения — расширение функциональных возможностей за счет реали зации интегрирования с переменным подын20 тегральным выражением при участии в процессе интегрирования независимой внешней составляюшей.

Поставленная цель достигается тем, что в интегратор введен второй суммаTop, первый вход которого соединен с выходом регистра подынтегрального выражения, а второй вход - с выходом формирователя переполнений, третий вход второго сумматора соединен со входом устройства, выход второго сумматора ,соединен с вторым входом регистра подын тегрального выражения.

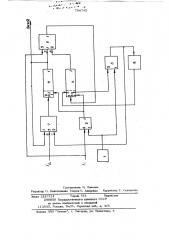

На чертеже представлена блок-схема цифрового интегратора. 10

Схема цифрового интегратора содержит генератор 1 тактовых импульсов, генератор 2 сдвиговых импульсов, регистр 3 подынтегрального выражения, накопительный регистр 4, формирователь 15

5 переполнений сумматоры 6 и 7, элемент задержки 8.

Выход регистра 3 подынтегрального выражения является выходом устройства.

Устройство работает следующим обра- 20 зом.

В исходном состоянии регистр 3 подынтегрального выражения и накопительный регистр 4, разрядность которых (И+ 1), обнулены. Генератор 1 тактовых импульсов задает частоту сдвига информации регистра 3 подынтегрального выражения и накопительного регистра 4.

Генератор 2 сдвиговых импульсов вырабатывает серии импульсов, причем коли чество импульсов в серии равно числу разрядов регистра 3 подынтегрального выражения и накопительного регистра 4, т. е. (Irl+ 1). C приходом каждого импульса частоты интеграций происхо1 дит вычислительный цикл, в течении которого производится полный сдвиг информации в регистрах 3 и 4. Входные импульсы с частотой следования В„ поI ступающие синхронно с частотой итерации, причем „ » „,, и с весом, раиным, например, единице, поступают со зьаком плюс на третий вход сумматора

7, на первый вход которого поступает содержимое регистра 3. подынтеграль45 ного выражения. Сумма вновь вводится в регистр 3 подынтегрального выражения, т. е. с приходом каждого импульса с частотой следования В содержимое регистра 3 подынтегрального выражения увеличивается на единицу. С по помщью сумматора 6 содержимое регист. ра 3 подынтегрального выражения складывается с содержимым накопительного регистра 4 во время каждой итерации,, а сумма с выхода сумМатора 6 вновь вводится в накопительный регистр., 4.

Так как содержимое регистра 3 подын745 4 тегрального выражения определяется И. значащими разрядами и (41+1)-й разряд регистра 4 обнулен, то наличие единицы в {МЯ+1)-м разряде накопительного регистра 4, в который вводится сумма с выхода сумматора 6, используется для формирования переполнения. С выхода формирователя 5 переполнений, синхронизированного импульсами генератора 1 тактовых импульсов, импульс переполнения, пройдя через элемент 8 задержки обнуляет (0+1)-й разряд накопительного регистра 4. Непосредственно с выхода формирователя 5 переполнений импульсы с час. тотой переполнений f>, имеющие вес, равный единице, и со знаком минус поступают на второй вход сумматора 7.

Частота переполнений f „ îïðåäeëÿåò- ся формулой

1 (1) где 1 - содержимое регистра 3 подынтегрального выражения, К емкость значащей части накопи-. тельного регистра 4, равная

2 " -1.

Так как входные импульсы с частотой следования К непрерывно увеличивают содержимое в регистре 3 подынтегрального выражения, являющееся одним из слагаемых суммы, поступающей в накопительный регистр 4, то частота переполнений с выхода формирователя

5 переполнений также будет увеличива, ся. Ввиду того, что импульсы с часто той следования 5 1 поступают на вто рой вход сумматора 7 с отрицательным знаком и уменьшают содержимое регистра 3 подынтегрального выражения, то увеличение содержимого регистра 3 подынтегрального выражения будет происходить до тех пор, пока частоты 1 и %p не сравняются, т. е.

И В (2) следовательно R R (=Хи К„= %.

Обозначим — = Т - время по истече%1 ю нии которого частоты д и $ В1, сТВН Т равными, тогда = ЗВ1, ь (4)

Таким образом, код,. содержащийся в регистре подынтегрального выражения,. будет отображать величину входной частоты Х В1, а время преобразования частоты в код равно Г .

Точность преобразования частоты в код зависит оот величины Г . Чем меньше величина +, тем меньше будет точность преобразования. Величину Г можно регулировать путем изменения емкости значащей части накопительного регистра 4, равной, или величины частоты итераций f .

Если за выход устройства принять выход формирователя 5 переполнений, 10 то предлагаемый цифровой дифференциальный интегратор может быть использован для формирования разгона и замедления в устройствах автоматического управления станками контурного или позиционного типа.

Цифровой интегратор позволяет производить интегрирование кода во времени и преобразовывать частоту в код. Регулирование постоянной времени интегрирования интегратора позволяет использовать его для управления станками, имеющими различные динамические харак-теристики. За счет экономии дорогостоящих- микросхем сокращения монтажных и технологических работ, ожидаемый экономический эффект от использования предлагаемого устройства составляет. около

200 руб. на одно устройство.

Формула изобретения

Цифровой интегратор, содержащий генератор гактовых импульсов, соединен35 ный с первыми входами формирователя переполнений и генератора сдвиговых

45 б импульсов, выход которого соединен с первыми входами регистра подынтегрального выражения и накопительного регистра, выход регистра подынтегрального выражения соединен с первым входом первого сумматора, выход которого подключен ко второму входу накопительного ре гистра, первый выход накопительного регистра соединен со вторым входом первого сумматора, а второй выход - со вторым входом формирователя переполнений, выход которого соединен через элемент задержки с третьим входом накопи» тельного регистра, второй вход генератоРа сдвиговых импульсов и третий вход первого сумматора являются управляющими входами устройства, о т л и ч а ю щи и с я тем, что, с целью расширения функциональных возможностей за счеу реализации интегрирования с переменным подынтегральным выражением при участии в процессе интегрирования независимой внешней составляющей, в него введен вто рой сумматор, первый вход которого сое динен с выходом регистра подынтегрального выражения, а второй вход — с выхо» дом формирователя переполнений, третий вход второго сумматора соединен со вхо» дом устройства, выход второго сумматора соединен с вторым входом регистра подынтегрального выражения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 519735 кл. G 06 2Г 1/00, 1974.

2. Патент США № 3701890 кл. 235-150.31, 1973.

Составитель H. Полеева

Редактор О. Колесникова Техред О. Андрейко Корректор Т. Скворцова

Заказ 2227/14 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, ЖЭ5, Раушская наб., д, 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4