Матричный накопитель для постоянного запоминающего устройства

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<»> 734807

Сыоз Советскик

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 27.12.77 (21) 2560542/18-24 (5! ) М. Кл.

G 11 С 17/00 с присоединением заявки №вЂ” (28) Приоритет—

Опубликовано 15.05.80. Бюллетень № 18

Гасударственный комитет (53) УДК 681.327. .67 (088.8) ао делам изобретений и открытий

Дата опубликования описания 25.05.80

В. И. Овчаренко и А. А. Кассихин (72) Авторы изобретения (71) Заявмтевь (54) МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

Изобретение относится к вычислительной технике и может быть использовано в постоянных запоминающих устройствах (ПЗУ) с электрическим перепрограммированием, сохраняющих информацию при отключении источника питания, в качестве элементов ламяти которых использованы МДП-транзисторы с лавинной инжекцией.

Известны матричные накопители для

ПЗУ на МДП-транзисторах с и-каналом и лавинной инжекцией. Они содержат полупроводниковую подложку, разрядные шины, числовые управляющие шины и истоковые шины. Числовые шины расположены ортогонально разрядным и изолированы от них

-диэлектриком. На пересечении этих шин рйснОложены элементы памяти, которые выполнены в виде МДП-транзисторов с лавинной инжекцией с изолированным (плавающим) и управляющим затворными электро. дами. Числовые шины выполнены из поликристаллического кремния, одновременно являются управляющими электродами транзисторов: Истоковые диффузионные шины являются истокамй транзисторов, а диффузионные области — стоками. Разрядные шины выполнены металлическими, Соединены

2 с диффузионными областями смежных транзисторов с помощью контактного соединения металл-полупроводник. Истоковые шины постоянно соединены с шиной нулевого потенциала (1J и (2J.

Недостаток этих накопителей — большая площадь занимаемая элементом памяти на кристалле, что ограничивает их информационную емкость.

Наиболее близким техническим решением является матричный накопитель, в ко10 тором металлические разрядные шины заменены на диффузионные и исключены контактные соединения металл=полупроводник, что позволило уменьшить площадь, занимаемую на кристалле (3).

К недостаткам этого устройства следует отнести большую площадь, занимаемую на кристалле, необходимость травления V-образных углублений с малым размером щели, малое расстояние между смежными диффузионными шинами, что может приводить к замыканию их, наличие операции подлегирования областей между . разрядными шинами, с целью исключения паразитных связей.

734807

Цель изобретения — повышение степени интеграции накопителя.

Поставленная цель достигается тем, что в матричный накопитель для ПЗУ, содержащий полупроводниковую подложку, на поверхности которой расположены параллельные эпитаксиальные области с диффузионными разрядными шинами, на поверхности которых расположен первый слой диэлектрика, на котором размещены первые изолированные электроды, на поверхности которых расположен второй слой диэлектрика, на котором размещены параллельные адрес ные шины, перпендикулярные диффузионным -разрядным шинам и совмещенные с управляющими электродами элементов памяти, введены вторые изолированные электроды, размещенные на первом слое диэлектрика между первыми изолированными электродами с перекрытием их краев по поверхности второго слоя диэлектрика, причем изолированные электроды расположены между управляющими электродами элементов памяти и параллельными эпитаксиальными областями с диффузионными разрядными шинами.

Кроме того, в полупроводниковой подложке между элементами памяти под адресными шинами могут быть выполнены углубления, предпочтительно трапецеидальные, при этом изолированные электроды желательно выполнять Л -образными.

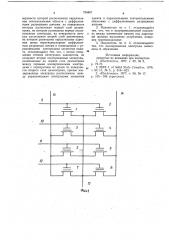

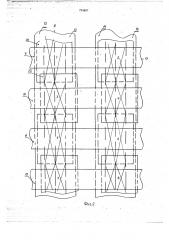

На фиг. 1 изображена электрическая схема накопителя; на фиг. 2 — топологическая схема накопителя; на фиг. 3 — продольное сечение части накопителя; на фиг. 4 — поперечное сечение с углублениями трапецеидальной формы; на фиг. 5 — поперечное сечение части накопителя.

Накопитель состоит из и-канальных

МДП-транзисторов 1 — 8 с лавинной инжекцией с V-oáðàçíûìè, например изолиро ванными и управляющими, электродами, адресных шин 9 — 12, диффузионных разрядных шин 13 — 14, являющихся стоками элементов йамяти, и полупроводниковой подложки 15, выполняющей роль истоков элементов памяти и постоянно подключенной к шине нулевого потенциала.

Подложка 15 выполнена низкоомной, легированной сурьмой, кремниевой и -типа, на

"ее поверхности расположены параллельные эпитаксиальные области кремния 16, слабо легированные бором, нижние части которых

17 легированы бором в большей степени.

Толщина и степень легирования бором этой

= =частй определяют длину канала и пороговое

"напряжение транзисторов с лавинной инжекцией.

В эпитаксиальных областях выполнены диффузионные разрядные шины 13, 14 и+-типа проводимости. Толщина и степень легирования бором верхней части 16 определяют емкость разрядных шин 13, 14 и напряжение пробоя их р-п переходов. Первый слой диэлектрика выполнен из двуокиси кремния 18, и выращен с использованием методов локального окисления.

Верхняя часть эпитаксиальной области под этим окислом 19 подлегирована бором для предотвращения образования инверсных каналов между разрядными шинами. Первый слой диэлектрика 18 одновременно изолирует разрядные шины от адресных шин 20 и является подзатворным диэлектриком 21, на котором размещены первые изолированные электроды 22 из легированного поликристаллического кремния, являющиеся плавающими затворами транзисторов 1, 2, 5, 6.

10

Формула изобретения

1. Матричный накопитель для постоянного запоминающего устройства, содержащий полупроводниковую подложку, на поВторые изолированные электроды 23 выполнены также из поликристаллического кремния и являются плавающими затворами транзисторов 3, 4, 7, 8. Эти электроды 23 перекрывают первые изолированные электроды 22 смежных транзисторов с минималь ным технологически возможным заЗором по поверхности второго слоя диэлектрика 24 на -участках 25.

Накопитель работает обычно в режиме считывания, а запись информации производится после стирания под действием ультрафиолетового облучения через крышку с кварцевым стеклом, что приводит все элементы памяти в единичное, проводящее состояние.

Запись нулевого, непроводящего состояния проводится в данный элемент памяти nos0 дачей на адресную шину 9 и разрядную шину 13 высоких положительных напряжений. За счет протекания тока стока через транзистор 1, разогрева электронов в канале под действием продольного электрического поля стока, инжекции горячих электронов из канала под действйем поперечного электрического поля затвора, происходит вытягивание и захват электронов на плавающий затвор, в результате происходит увеличение порогового напряжения только у

4g транзистора 1.

Считывание информации проводится подачей на разрядную и адресную шины данного элемента памяти положительных считывающих напряжений и фиксацией протекающих токов в разрядной шине.

4s Основными преимушествами данных конструкций накопителя являются повышение в 1,5 — 2 раза информационной емкости накопителя при одинаковой площади на кристалле, уменьшение вероятности замыкания между затворами смейных транзисторов и сокращение времени стирания информации за счет уменьшения экранировки плавающих затворов адресными шинами.

734807 верхности которой расположены параллельные эпитаксиальные области с диффузионными разрядными шинами, на поверхности которых расположен первый слой диэлектрика, на котором размещены первые изолированные электроды, на поверхности которых расположен второй слой диэлектрика, на котором размещены параллельные адресные шины перпендикулярные диффузионным разрядным шинам и совмещенные с управляющими электродами элементов памяти, отличающийся тем, что, с целью повышения степени интеграции накопителя, он содержит вторые изолированные электроды, размещенные на первом слое диэлектрика между первыми изолированными электродами с перекрытием их краев по поверхности второго слоя диэлектрика, причем изолированные электроды расположены между управляющими электродами элементов памяти и параллельными эпитаксиальными областями с диффузионными разрядными шинами.

2. Накопитель по п. 1, отличающий ся тем, что, что в полупроводниковой подложке между элементами памяти под адресны-мй шинами выполнены углубления, например трапецеидальные.

3. Накопитель по п. 2, отличающийся тем, что изолированные электроды выполнены Л -образными.

1О

Источники информации, принятые во внимание при экспертизе

1. «Electronics», 1977, ч. 50, № 2, р. 72-73.

2. IEEE J. of 3olid 3tate Cirenits», 1976, ч. SC-11, № 5, р. 616 — 621.

3. «Electronics», 1977, ч. 50, № 17, р. 105 †1 (прототип).

734807

Составитель Ю. Ушаков

Редактор С. Патрушева Техред К.Шуфрич Корректор Т. Скворцова

Заказ 2234(16 Тираж бб2 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5.

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4