Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

пв;те к. ннъе„ - „- +а б 76 и и втоц„- г1 Я фСоюз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 03.01.78 (21) 2566739/18-24 (51) М. Кл.2 с присоединением заявки №вЂ”

G 11 С 21/00

Государственный комитет

СССР (23) Приоритет—

Опубликовано 15.05.80. Бюллетень № 18

Дата опубликования описания 25.05.80 (53) УДК 628.327..6 (088.8) до делам изобретений и открытий (72) Авторы изобретен и я.

Е. А. Евсеев, А. Н. Горбунов и Ю. А. Плужников (71) Заявитель (54) БУФЕРНОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Буферное зайоминающее устройство относится к автоматике и вычислительной технике и может быть использовано в импульс ных и цифровых устройствах.

Известны буферные зайоминающие устройства последовательного действия, которые имеют недостаточно высокое быстродействие, так как позволяют производить сЧитывание информации только после окончания записи и не позволяют производить считывание одновременно с записью (1).

Наиболее близким к предложенному является буферное зайоминающее устройство, содержащее двоичный счетчик, выход которого через элемент памяти соединен с шиной выходных импулЬсов, шину опроса, соединенную с другим входом элемента памяти. Шина входных импульсов и шина вы: ходных импульсов подключены ко входам первого элемента И и через элемент задержки к первым входам соответственно второго и. третьего элементов И. Выход первого элемента И через блок формирования сигнала запрета соединен со вторыми входами второго и третьего элементов И. Выход второго элемента И подключен к суммирующему входу счетчика, а выход третьего элемента И вЂ” ко входу узла управления, выход которого подключен к вычитающему входу счетчика (2).

Недостатками известного буферного запоминающего устройства являются ограниченный частотный диапазон работы устройства и недостаточно высокое быстродействие. Так как двоичный счетчик работает с суммарной частотой двух сигналов — входных сигналов и сигналов опроса, то устройство надежно работает при условии, что су1 1марная частота не превышает предельную рабочую частоту счетчика. В связи с этим частоты двух сигналов выбирают от-. носительно невысокими и, следовательно, быстродействие устройства также недостаточно высоко. Кроме того, данное устройство характеризуется относительно невысокой разрешающей способностью, обусловленной тем, что в некоторых случаях при перекрывании входных сигналов и сигналов onроса схема запрета не вырабатывает выход-ной сигнал, и перекрывающиеся импульсы действуют на счетчик.

734810

10 входных импульсов, шину 11 опроса, выходную шину 12.

Работает устройство следующим образом.

В исходном состоянии счетчик 1 и триггер 7 находятся в нулевом состоянии. Элемент 4 И закрыт по первому входу низким (запрещающим) потенциалом шины 10 входных импульсов и открыт по второму вхо- 30

SS

Цель изобретения — повышение быстродействия и разрешающей способности устройства.

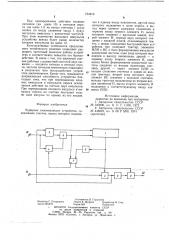

Поставленная цель достигается тем, что в устройство введены триггер, элементы ИЛИ и НЕ и блок формирования импульсов разностной частоты, один вход которого подключен к выходу накопителя, другой — к первому входу второго элемента И, один выход блока формирования разностной частоты соединен со входом вычитания счетчика, другой — через элемент ИЛИ со входом сложения счетчика и одним из входов триггера, второй вход которого через элемент НЕ соединен с выходом счетчика, выходы триггера подключены ко вторым входам элементов И, выход второго элемента И подключен к соответствующему входу элемента ИЛИ.

На чертеже приведена блок-схема буферного запоминающего устройства.

Буферное запоминающее устройство содержит счетчик 1, накопитель 2, блок 3 формирования импульсов разностной частоты, элементы 4, 5 И, элемент 6 ИЛИ, триггер 7, элемент 8 НЕ, элемент 9 задержки, шину ду высоким (разрешающим) потенциалом нулевого выхода триггера 7. Элемент 5 И закрыт по обоим входам. Элемент 9 задержки выбран . из расчета, что время задержки (тз д равно или больше суммарного времени задержки сигнала на блоке 3 формирования импульсов разностной частоты, на первом разряде счетчика 1, на элементе 8 НЕ и на триггере 7.

Блок 3 формирования импульсов разностной частоты работает таким образом, что на обоих его выходах сигналы отсутствуют, если на первый и на второй входы сигналы поступают поочередно. Если после поступления сигнала на первый вход, на второй вход поступят два и более сигналов подряд,то первым из них блок подготавливается для прохождения сигналов по второму каналу, а второй и последующий сигналы проходят на второй выход устройства. С приходом затем сигнала на первый вход блок подготавливается для прохождения последующих сигналов по первому каналу и т. д.

Входные импульсы (импульсы записи) с шины 10 поступают на первый вход блока 3 формирования импульсов разностной частоты и на первый вход элемента 4 И.

Первый импульс подготавливает блок 3 формирования импульсов разностной частоты для прохождения последующих импульсов

ie

1S

20 по первому каналу (на первый выход) и, открывая элемент 4 И, поступает через элемент

6 ИЛИ на единичный вход триггера 7 и на вход сложения счетчика 1, записывая в него число 1. При этом на выходе счетчика 1 появляется высокий потенциал, в результате чего в накопитель 2 записывается единица. По переднему фронту импульса с выхода элемента 6 ИЛИ устанавливается в единичное состояние триггер 7. При этом высоким потенциалом единичного выхода триггера открывается по второму входу элемент

5 И, низким (запрещающим) потенциалом нулевого выхода триггера закрывается по второму входу элемент И 4. Последующие входные импульсы проходят через блок 3 формирования импульсов разностной частоты на ее первый выход и затем через элемент 6 ИЛИ на вход сложения счетчика 1, увеличивая каждый раз его содержимое на единицу.

Импульсы опрашивающей частоты, поступающие с шины 11 на вход накопителя 2 вызывают появление импульсов на его выходе до тех пор, пока в накопителе 2 записана единица. Импульсы с выхода накбпителя 2 поступают на второй вход блока 3 формирования импульсов разностной частоты и через элемент 9 задержки — на вход элемента 5 И. При этом первый выходной импульс накопителя 2, поступив на второй вход блока 3 формирования импульсов разностной частоты, не пройдет на второй выход, а только подготовит его для прохождения последующих импульсов. Одновременно первый импульс, задержанный элементом 9 задержки, пройдет через элемент

5 И на выходную шину 12 устройства. Второй импульс с выхода накопителя 2 пройдет через блок 3 формирования импульсов разностной частоты (по второму каналу) на вход вычитания счетчика 1, уменьшив на единицу его содержимое, и поступит снова на выход устройства и т. д. N+1 импульс опрашивающей частоты с выхода накопителя 2 (где N — количество входных импульсов, поступающих с шины 10 на вход сложения счетчика 1), пройдя через блок 3 формирования импульсов разностной частоты на вход вычитания счетчика 1, обнуляет его. При этом на выходе счетчика 1 появляется запрещающий потенциал, а на выходе элемента 8 НŠ— соответственно разрешающий потенциал, по переднему фронту которого триггер 7 возвращается в исходное (нулевое) состояние. Запрещающий потенциал единичного выхода триггера 7 закрывает по второму входу элемент 5 И, поэтому N+1 импульс с выхода накопителя

2 задерживается элементом 9 задержки, на выход устройства не пройдет. Таким образом, количество импульсов, поступивших на выходную шину 12 устройства равно количеству входных импульсов на шине 10.

734810

Составитель В. Гордонова

Редактор С. Патрушева Техред К. Шуфрич Корректор Н. Стец

Заказ 2234/16 Тираж 662 Подписное

° ЦНИИ ПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4

При одновременном действии входных сигналов (на шине 10) и сигналов опроса (на шине 11) на входы счетчика 1 после записи по входу сложения числа 1 будут поступать импульсы с разностной частотой.

При этом количество выходных имлульсов устройства всегда будет равно количеству входных импульсов на шине 10.

Конструктивные особенности предлагаемого технического решения позволяют расширить частотный диапазон работы устройства и соответственно повысить его быстродействие. В связи с тем, что двоичный счетчик работает с разностной частотой двух сигналов — входного сигнала и сигнала опроса, частоты сигналов значительно повышают, в результате чего быстродействие устройства увеличивается. Кроме того, повышается разрешающая способность устройства благодаря тому, что при перекрывании входных импульсов и импульсов опроса исключается действие на счетчик двух импульсов.

При перекрывании входного импульса и импульса опроса на счетчик поступает только один импульс по одному из его входов.

Формула изобретения

Буферное запоминающее устройство, содержащее счетчик, выход которого подключен к одному входу накопителя, другой вход которого подключен к шине опроса, а выход через элемент задержки подключен к первому входу первого элемента И, выход которого соединен с выходной шиной, втою рой элемент И, первый вход которого соединен с входной шиной, отличающееся тем, что, с целью повышения быстродействия устройства оно содержит триггер, элементы

ИЛИ и НЕ и блок формирования импульсов разностной частоты, один вход которого подключен к выходу накопителя, другой — к первому входу второго элемента И, один выход блока формирования разностной частоты соединен со входом вычитаний счетчика, другой — через элемент ИЛИ со входом сложения счетчика и одним из входов триггера, второй вход которого через элемент НЕ соединен с выходом счетчика, выходы триггера подключены ко вторым входам элементов И, выход второго элемента И подключен к соответствующему входу эле20 мента ИЛИ.

Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР м № 343300, кл. G 11 С 11/00, 1972.

2. Авторское свидетельство СССР № 446052, кл. G 06 F 5/00, 1974 (прототип) .