Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Cow Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 27.12.77 (2! ) 2560564/18-24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 15.05.80. Бюллетень № 1

Дата опубликования описания 25.05.80

Гееударствеииый комитет

СССР. до делам изобретений и открытий

Г. В. Басалаев и А. Б. Кметь (72) Авторы изобретения (7l) Заявитель

Физико-механический институт АН Украинской CCP ( (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и измерительной технике и может быть использовано в быстродействующих преобразователях !напряжение-код и для систем регистрации однократных быстропротекающих процессов в аналоговой форме.

Известно двухтактное запоминающее устройство (ЗУ), содержащее входной усилитель, ключи, запоминающие конденсаторы, выходные усилители и выходные ключи (1).Недостатками известного устройства аналоговой памяти являются большая динамическая погрешность в режиме слежения и .непродолжительное время хранения информации с заданной точностью.

Известно также запоминающее устройство для аналоговых сигналов, содержащее накопительный конденсатор и систему коррекции, выполненную в виде генератора ступенчатого напряжения, подключенного через последовательно соединенные ключи, диод и резистор к обкладке накопительного конденсатора и ко входу компаратора, другой вход которого соединен с выходом генератора ступенчатого сигнала (2) .

К недостаткам этого устройства памяти относятся ограйиченный только положительными значениями входных сигналов динамический диапазон и невысокое быстродействие, обусловленное тем, что накопительный

S конденсатор заряжается через резистор и диод. Кроме того, величина частоты следования ступенчатого напряжения зависит от числа стабилизируемых уровней напряжения, вследствие чего для увеличения числа этих уровней (т. е. повышения точности ЗУ) требуется увеличение времени хранения ЗУ без учета коррекции. В то же время используемая в устройстве система коррекции требует, чтобы изменение напряжения за время хранения происходило только в сторону уменьшения, что достигается введением искусственной утечки, т. е. уменьшением времени хранения ЗУ без учета коррекции. Указанные требования находятся в противоре/ чии, что делает это устройство ненадежным в работе при точностях, необходимых для практики. Правда, при введении искусственной утечки время хранения ЗУ без учета коррекции можно сохранить на требуемом уровне путем увеличения емкости запоми1

734813

3 нающего конденсатора. Однако это сильно умейьшает быстродействие ЗУ.

Цель изобретения — расширение динамического диапазона запоминаемых сигналов и повышение быстродействия устройства.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее основной блок памяти, один из входов которого соединен со входом устройства, другие входы основного блока памяти соединены с первыми выходами блока управления, компаратор, один из входов которого подключен к выходу устройства и выходу основного блока памяти, другой вход компаратора подключен к выходу первого генератора ступенчатого напряжения, вход которого соединен с одним из выходов триггера, генератор импульсов, соединенный со входом триггера, в него введены блок дифференцирования, дополнительный блок памяти, два ключа и второй генератор ступенчатого напряжения, вход которого соединен с другим выходом триггера, выход второго генератора ступенчатого напряжения подсоединен к одним из входов ключей, другие входы которых соединены со вторыми выходами блока управления, входы блока управления соединены с выходами блока дифференцирования, один из входов которого соединен с выходом компаратора, а другой вход блока дифференцирования — с выходом генератора импульсов, один из входов дополнительного блока памяти соединен со входом основного блока памяти, другие входы дополнительного блока памяти соединены с третьими выходами блока управления, выход дополнительного блока памяти соединен с выходом компаратора, выходы ключей подсоединены к третьим входам основного и дополнительного блоков памяти соответственно.

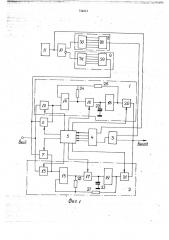

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 — диаграмма напряжений на управляющих входах ключей; на фиг. 3 — диаграмма, поясняющая работу устройства в режиме хранения.

Устройство содержит основной и дополнительный блоки 1 и 2 памяти, компаратор 3, блок 4 дифференцирования, блок 5 управления, ключи 6 и 7, генераторы 8 и 9 ступенчатого напряжения, триггер 10, генератор

11 импульсов.

Основной и дополнительный блоки 1 и

2 памяти выполнены на последовательно соединенных первых ключах 12 и 13, первых усилителях 14 и 15, вторых ключах 16 и

17, вторых усилителях 18 и 19, третьих ключах 20 и 21. Накопительные элементы, например конденсаторы 22 и 23, подключены ко входам вторых усилителей и шине нулевого потенциала. Кроме того, они содержат элементы 24 — 27 обратной связи.

Генераторы ступенчатого напряжения выполнены на цифроаналоговых преобразователях 28 и 29 и счетчиках 30 и 31.

S0

Так, в режиме хранения находится основной блок 1 памяти. Выходное напряжение, т. е. напряжение этого блока 1, сравнивается периодически с напряжением генератора

8 ступенчатого напряжения на компараторе 3. Выходной сигнал компаратора 3, представляющий собой широтный импульс, ширина которого линейно зависит от выходного напряжения устройства, поступает на один из входов блока 4 дифференцирования. На другой его вход подается напряжение прямоугольной формы с выхода генератора 11 импульсов. На выходе блока 4 появляется импульс, фаза которого пропорциональна напряжению хранения. Если выходное напряжение, хранящееся в виде одного из дискретных уровней, отклонится в ту или другую сторону от своего первоначального значения, то из блока 5 управления на управляющие входы ключей 6 и 16 поступят сигналы, переводящие указанные ключи в проводящее состояние. Конденсатор 22 зарядится (или разрядится) до напряжения, определяемого величиной напряжения, поступающего от второго генератора 9 ступенчатого напряВ предложенном устройстве ввод и хранение информации осуществляется по двухтактной схеме, поэтому, когда в основном блоке памяти происходит слежение за входным сигналом (выборка), дополнительный

s блок памяти находится в режиме хранения.

Временное управление работой ключей осуществляется блоком 5 управления (фиг. 2), при этом ключи переходят в состояние «Замкнуто» при подаче на их управляющие входы отрицательного потенциала.

Рабата устройства осуществляется с момента времени t< (фиг. 2). В промежуток времени от ti до tq ключи 12, 16 и 21 замкнуты. Блок 1 памяти, находясь в режиме выборки, следит за входным сигналом, а

ts блок 2 памяти осуществляет хранение ранее записанной информации; т. е. на выходе устройства присутствует сигнал блока 2 памяти. В момент времени t 2, режимы каналов меняются, на выходе устройства появляется сигнал блока 1 памяти, а в блоке 2 памяти

2 осуществляется отслеживание входного сигнала.

В течение времени хранения, которое не ограничивается параметрами схемы, напряжение на конденсаторе 22 может изменять2 ся в сторону уменьшения или увеличения от того значения, которое было в момент переключения из режима ввода в режим хранения. Это происходцт за счет саморазряда конденсатора 22, а также вследствие конечного сопротивления закрытых ключей 16 и зО 17 и входного сопротивления усилителей

18 и 19. Для коррекции указанного изменения предназначена часть. схемы устройства, состоящая из компаратора 3, блока 4 дифференцирования и двух генераторов 8 и 9

3S ступенчатого напряжения.

734813

5 жения. Это напряжение имеет временной и потенциальный сдвиг на половину ступеньки относительно напряжения первого генератора 8 ступенчатого напряжения, что обеспечивается включением триггера 10 и смещением уровня в цифроаналоговом преобразователе 29, поэтому в результате коррекции на выходе устройства устанавливается напряжение, соответствующее середине между двумя дискретными уровнями, между значениями которых находится входной сигнал (см. фиг. 3).

В предложенном устройстве хранимое напряжение может отклоняться в любую сторону от первоначального значения, поскольку коррекция имеет место в обоих случаях. Динамический диапазон предложенного устройства не ограничивается, как в известном, положительными значениями входных сигналов, а определяется только параметрами используемых усилителей и ключей.

Введение в устройство блока дифференцирования позволяет повысить надежность устройства. Это объясняется тем, что влияние дестабилизирующих факторов (изменение напряжения питания, старение, температурные воздействия), имеющих место в блоке дифференцирования, выполненного по схеме обычного дифференциатора на RCцепочке с последующим усилителем, полностью устраняется.

Предложенное устройство превосходит известное по быстродействию, поскольку в нем не затрачивается время на выборку, а в режиме хранения подразрядка накопительного конденсатора осуществляется от усилителя с низким выходным сопротивлением.

Таким образом, по сравнению с известным предложенное устройство имеет широкий динамический диапазон и обеспечивает высокое быстродействие и надежность в работе при длительном хранении информации.

Формула изобретения

Аналоговое запоминающее устройство, содержащее основной блок памяти, один из входов которого соединен со входом устройства, другие входы основного блока памяти соединены с первыми выходами блока управления, компаратор, один из входов которого подключен к выходу устройства и выходу основного блока памяти, другой вход компаратора подключен к выходу первого генератора ступенчатого напряжения, вход которого соединен с одним из выходов триггера, генератор импульсов, соединенный со входом триггера, отличающееся тем, что, с целью расширения динамического диапазона запоминаемых сигналов и повышения быстродействия устройства, в него введены блок дифференцирования, дополнительный блок памяти, два ключа и второй генератор ступенчатого напряжения, вход которого соединен с другим выходом триггера, выход второго генератора ступенчатого напряжения подсоединен к одним из входов ключей, другие входы которых соединены со вторыми выходами блока управления, входы блока управления соединены с выходами блока дифференцирования, один из входов которого соединен с выходом компаратора, а другой вход блока дифференцирования — с выходом генератора импульсов; один из входов дополнительного блока памяти соединен со входом основного блока памяти, другие входы дополнительного блока памяти соединены с третьими выходами блока управления, выход дополнительного блока памяти соединен с выходом компаратора, выходы ключей подсоединены к третьим входам основного и дополнительного блоков памяти соответственно.

3$ Источники информации, принятые во внимание при экспертизе

1. «Автометрия», 1973, № 3, с. 98.

2. Авторское свидетельство СССР № 339961, кл. G 11 С 27/00, 25.06.70 (прототип).

734813

Н7 г.2

Бх.

61 16

Редактор С. Лыжова

Заказ 2234/16

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 ÑÒ. Я

О

Составитель А. Воронин

Техред К. Шуфрич Корректор Т. Скворцова

Тираж 662 Подписное