Цифровой умножитель частоты

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (») 734867

Союз Советски к

Социалистическик

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 10.10.77 (21) 2532834/18-09 с присоединением заявки №вЂ” (51) М. Кл.2

Н 03 В 19/10

Гасударственный комитет

СССР (23) Приоритет— (53) УДК 621.374..4 (088.8) Опубликовано 15.05.80. Бюллетень № 18 .Дата опубликования описания 25.05.80 ао делам нзабретеннй н открмтнй

В.В. Смеляков, В. И. Бармин, H. М. Булгаков, А. С. Багацкий, А. И. Алисейко и 1О. 1. Ольховский (72) Авторы изобретения

Харьковский институт радиоэлектроники,;: .,:,;,,-,::, ., .; „ (71) Заявитель (54) ЦИФРОВОИ УМНОЖИТЕЛЪ ЧАСТОТЫ

Изобретение относится к радиотехнике и может быть использовано в измерительных системах различного назначения.

Известен цифровой умножитель часто„ты, содержащий последовательно соединенные формирователь входного сигнала, блок управления, первый вентиль, первый делитель частоты, элемент И, выход которого является выходом цифрового умножителя частоты, элемент ИЛИ и первую схему переноса; выход которой подключен к другому входу первого делителя частоты, 1о а другой вход — к выходу первого регистра памяти, входом подключенного к другому входу блока управления, а также последо вательно соединенные кварцевый генератор, первый формирователь импульсов, второй вентиль, второй делитель частоты, выход которого подключен ко входу первого регистра памяти, второй регистр памяти, другим входом подключенный к выходу вто/ рого вентиля и к первому входу третьего вентиля, вторая схема переноса, к другому щ входу подключен выход элемента И, сумматор и триггер задержки, выход и другой вход которого подключены соответственно к другому и к третьему входу первого вен2 тиля, при этом выход блока управления подключен к другим входам элемента ИЛИ и второго вентиля, к второму входу третьего вентиля и через третью схему переноса к другому входу сумматора, выходом подсоединенного к другому входу третьей схемы переноса, к третьему входу которой через третий регистр памяти подключен выход третьего вентиля (1) .

Однако в известном цифровом умножителе частоты недостаточно высокая точность умножения из-за неравномерности следования выходных импульсов.

Цель изобретения — повышение точности умножения.

Для этого в цифровой умножитель частоты, содержащий последовательно соединенные формирователь входного сигнала, блок управления, первый вентиль, первый делитель частоты, элемент И, выход которого является выходом цифрового умножителя частоты, элемент ИЛИ и первую схему переноса, выход которой подключен к другому входу первого, делителя частоты, а другой вход —. к выходу первого регистра памяти, входом подключенного к другому входу блока управления, а также последо734867

3 вательно соединенные кварцевый генератор, первый формирователь импульсов, второй вентиль, второй делитель частоты, выход которого подключен ко входу первого регистра памяти, второй регистр памяти, другим входом подключенный к выходу второго вентиля и к первому входу третьего вентиля, вторая схема переноса, к другому входу которой подключен выход элемента И, сумматор и триггер задержки, выход и другой

"вход которого подключены соответственно к другому и к третьему входу первого вентиля, при этом выход блока управления подключен к другим входам элемента ИЛИ и второго вентиля, к второму входу третьего вентиля и через третью схему переноса — к другому входу сумматора, выходом подсоединенного к другому входу третьей схемы переноса, к третьему входу которой через третий регистр памяти подключен выход третьего вентиля, между выходом кварцевого генератора и другим входом триггера задержки- включены последовательно соединенные управляемый фазовращатель и второй формирователь импульсов, а выходы второй и третьей схем переноса подключены к соответствующим входам цифрового устройства деления, выход которого подсоединен к другому входу управляемого фазовращателя (1).

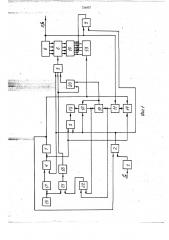

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 — эпюры напряжений в соответствующих точках схемы.

Цифровой умножитель частоты содержит формирователь 1 входного сигнала, блок 2 управления, первый, второй и третий вентили 3, 4, 5, первый и второй делители 6, 7 частоты элемент И 8, элемент ИЛИ 9, первую, вторую и третью схемы 10, 11, 12 переноса, первый, второй и третий регистры 13, 14, 15 памяти, кварцевый генератор 16, первый и второй формирователи 17, 18 импульсов, сумматор 19, триггер 20 задержки, управляемый фазовращатель 21 и цифровое устройство 22 деления.

Цифровой умножитель частоты работает следующим образом.

В исходном состоянии триггеры всех регистров 13, 14, 15 памяти, делители 6, 7 частоты, а также триггер 20 задержки находятся в нулевом состоянии. Все вентили 3, 4, 5 закрыты. Коэффициент деления делителя 7 частоты устанавливается равным К. Нажимает кнопку «Пуск», находящуюся в блоке

2 управления. При этом подготавливается формирователь 1 входного сигнала. При переходе умножаемого сигнала, имеющего частоту (х, через нулевое значение, блок уйравления 2 вырабатывает сигнал %х(1)(фиг. 26), что приводит к открытию вентилей 4 и 5.

Импульсы с частотой fo начинают поступать в делитель 7 частоты, регистры 14 и 15 памяти (фиг. 2в) . При поступлении первого выходного импульса с делителя 7 частоты

4 (см. фиг. 2е) на вход блока 2 управления, последний вырабатывает сигнал Чк (фиг. 26) по которому вентиль 5 закрывается. Таким образом в регистре 15 памяти зафиксировано число К. Следующим. импульсом Че блока управления 2 (фиг. 26) содержимое регистра 15 памяти переносится в сумматор

19 и регистр 22 памяти цифрового устройства деления.3а время первого периода Тп

1 импульсы с частотой fp поступают непрерывно как в делитель 7 частоты так и в регистр 14 памяти, но с каждым выходным импульсом делителя 7 частоты показания регистра 14 памяти сбрасываются в нуль. В итоге к концу первого периода в нем будет зафиксировано число Лп (фиг. 2д), накопленное за промежуток времени от момента последнего выходного импульса делителя 7 частоты до конца первого периода Тщ . То же самое число Ъп будет зафиксировано и в делителе 7 частоты. В регистр 13 памяти поступают выходные импульсы делителя 7 ъо частоты (фиг. 2е) и к концу периода Тх в нем будет зафкисировано число

2$

3$

43

se

По окончании периода Т х блок 2 управления вырабатывает сигнал Vpx (фиг. 26), который закрывает вентиль 4, открывает вентиль 3 и переносит показания регистра

13 в делитель 6. С этого момента начинается процесс деления импульсов, поступающих на вход делителя 6 частоты, на (q) (умножение частоты fx на К). Первый выходной импульс элемента И 8 (фиг. 2з) переносит показания регистра 13 памяти в делитель 6 частоты и показания регистра 14 памяти в сумматор 19 и сумматор 22 цифрового устройства деления. В сумматоре 19 производится операция (К в Ьп), причем если эта величина больше нуля, то на его выходе импульса не будет. Одновременно в цифровом устройстве деления 22 будет осуществлено деление Ьп на К. Код отношения " поступает на управляемый фазовращатель 21, что приводит к изменению фазы синусоиды на его выходе на величину 360 Q. После преобразования в формирователе 18 импульсов импульсы на его выходе, поступающие через вентиль 3 на вход делителя 6 частоты, будут смещены на величину Т ф (фиг. 2а и 2ж). Второй выходной импульс умножителя производит операцию ввода (ц) в делитель 6 частоты и

Ьп, в сумматор 19 и в сумматор 22 цифрового устройства деления, после чего в сумматоре 19 записывается число (К вЂ” 2Ьп), а в цифровом устройстве деления 22 осуществляетсй операция деления 2Ьп на К. Если число (К вЂ” 2Ьп) больше нуля, — на выходе сумматора 19 импульса не будет, а управляемый фазовращатель 21 сместит фазу синусоидального сигнала, пдступающего на его вход с кварцевого генератора

16 на величину 360 ",И, следовательно, 734867 5 импульсы, поступающие на вход делителя частоты 6, будут задержаны на Т o @ (фиг. 2а и фиг. 2ж).

По мере увеличения числа выходных импульсов умножителя может оказаться, что при некотором числе i (например i =3) величина (К вЂ” i Ьп) станет меньше нуля, что приведет к появлению импульса на выходе сумматора 19, который перенесет из регистра 15 памяти число К в сумматор 19 и, следовательно, в нем записывается положительное число (2К вЂ” i4n), а также в сумматоре цифрового устройства деления 22 произведена операция ian — К. На управляеhfbIH фазовращатель 21 подается код числа — "4 Я=, что приводит к задержке импульсов, поступающих на делитель,6 частоты через вентиль 3 на величину Т вЂ”" — „":- . Одновременно выходной импульс сумматора 19 через триггер 20 задержки закрывает вентиль 3.

По этой причине очередной импульс с выхода формирователя импульсов 18 (обозначен пунктиром на фиг 2ж) через вентиль 3 не пройдет, а осуществляет переброс в исходное состояние триггера задержки 20, который в свою очередь вновь открывает вентиль 3.

Коррекция последующих импульсов происходит аналогично. Наличие в цифровом умножителе частоты введенных элементов позволяет получить равномерную последовательность импульсов на выходе умножителя (повысить точность умножения), что дает возможность применения умножителя в составе прецизионной измерительной аппаратуры.

Формула изобретения

Цифровой умножитель частоты, содержащий последовательно соединенные формирователь входного сигнала, блок управления, первый .вентиль, первый делитель ь частоты, элемент И, выход которого является выходом цифрового умножителя частоты, элемент ИЛИ и первую схему гереноса, выход которой подключен к другому входу первого делителя частоты, а другой вход— к выходу первого регистра памяти, входом подключенного к другому входу блока управления, а также последовательно соединенные кварцевый генератор, первый формирователь импульсов, второй вентиль, второй делитель частоты, выход которого подключен ко входу первого регистра памяти, второй регистр памяти, другим входом подключенный к выходу второго вентиля и к первому входу третьего вентиля, вторая схема переноса, к другому входу которой подключен выход элемента И, сумматор и триггер задержки, выход и другой вход которого подключены соответственно к другому и к третьему входу первого вентиля, при этом выход блока управления подключен к другим входам элемента ИЛИ и второго вентиля, к Второму входу 1третьего вентиля и через третью схему переноса — к другому входу сумматора, выходом подсоединенного к другому входу третьей схемы переноса, к третьему входу которой через третий регистр памяти подключен выход третьего веч 2$ тиля, отличающийся тем, что, с целью повышения точности умножения, между выходом кварцевого генератора и другим входом триггера задержки включены последовательно соединенные управляемый фазовращатель и второй формирователь импульсов, а выходы второй и третьей схем переноса подключены к соответствующим входам цифрового устройства деления, выход которого подсоединен к другому входу управляемого ф зовращателя.

ЗХ Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке № 2336740/18-09. кл. Н 03 В 19/! О, 23.03.76 (прототип) .