Реверсивный распределитель

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТВЛЬСТВУ

Союз Советских

Социалистических

Реслублнк р»734880 ьфц11т р: .„ц, (5Ф2М. Кл. (61) Дополнительное к авт. свид-ву— (22) Заявлено 189474 (21) 2017410/18-21 с присоединением заявки ¹(23) Приоритет—

Опубликовано 150580 Бюллетень № 18

Дата опубликования описания 20. 05. SO

Н 03 К 23/08

Государственный комитет

СССР по делам изооретеиий и открытий (53) УДН 621 ° 374, .325.4(088.8) (72) Автор изобретения

E. И. Колков

Ленинградский институт авиационного приборостроения (71) Заявитель (54) PEBEPCHBHblA ЫСПРКдЕЛИтЕЛЬ

Изобретение относится к области Известен, также реверсивный распре- . импульсной техники и может быть ис- делитель, содержащий однотипные ячей; пользовано в устройствах формирования ки на запираемых тиристорах с нагрузи временного разделения электрических ками в цепи анода, цепи запирания коимпульсов, например в телемеханике, 5 торых состоят из последовательно сопри построении систем управления вен единенных зарядного резистора и комтильными преобразователями. мутирующего конденсатора, к общей точИзвестен реверсивный распредели- ке которых через разделительный диод тель, содержащий однотипные ячейки подключен управляющий электрод ва- . на тиристорах, цепи запирания кото- 10 пираемого тиристора, который соединен рых состоят из ключевых элементов через резистор с минусовой шиной исна транзисторах, включенных в катод- точника питания, а также с обкладками ную цепь каждого из тиристоров, При- двух разделительных конденсаторов, чем накопительный конденсатор каждой другие обкладки кбторых через диоды из ячеек подключен через последова- 15 подключены к шинам прямого и ревертельно включенные диод и дополнитель- сивного управления, а через резистоный управляемый ключ к управляющему .ры — к анодам запираежих тиристоров электроду каждого из тиристоров (1). предыдущей и последующей ячеек t21 °

B таком устройстве коммутирующие 20 цепи построены по принципу междуфаз- Это устройство является наиболее ной коммутации с накопительными кон- близким по технической сущности к денсаторами, что приводит к появлению данному изобретению. Однако оно имена нагрузках коммутационных помех вну- ет низкую коммутационную помехозащитреннего происхождения, что, в свою 25 щенность, зависящую от величины наочередь, ухудшает работоспособность грузки, которая, в свою очередь, мовсего устройства. Устранение этого не- жет изменяться в широких пределах. достатка за счет введения дополнитель- Значительная функциональная сложность ных переключаемых элементов значитель- такого устройства делает его ненадежно усложняет устройство в целом. 30 ным в эксплуатации.

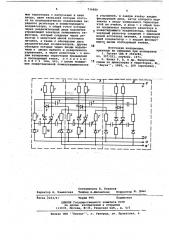

734880, На чертеже представлена схема .предлагаемого устройства. 15

Реверсивный распределитель содержит однотипные ячейки на запираемых тиристорах 1 с нагрузками 2 в цепи анода, резисторы 3 и 3, причем аноды тиристоров 1 предыдущей и после- 20, дующей ячеек через соответствующие резисторы 3 и 3 соединены с обклад ками двух разделительных кснденсаторов 4 и 4, которые, в свою очередь,. соответственно соединены с диодами 25

5 и 5, цепи запирания каждой ячейки состоят иэ последовательно соединенных зарядного резистора 6 и коммутирующего конденсатора 7, к общей точке которых через разделительный диод 8 подключен управляющий электрод запираемого тиристора 1, фикси"рующий диод 9 в каждой ячейке, катод которого подключен к аноду запираемого тиристора 1 этой же ячейки, а анод — к общей точке соединения зарядного резистора б и коммутирующего конденсатора 7, резистор 10, плюсовую шину 11 и минусовую шину .12 источника питания, причем через ре-зистор 10 управляющий электрод запи- 40 раембго тиристора 1 соединен с минусовой шиной 12, а зарядный резистор

6 соединен с плюсовой шиной 11.

Шйны 13 и 13 прямого и реверсив ного. управления соединены через диоды 5 и 5 с обкладками разделитель ных конденсаторов 4 и 4 . . Коммутирующий конденсатор 7 соеди нен с анодом фиксирующего диода 9 последующей ячейки.

Устройство работает следующим об разом.

При подаче напряжения питания включенным окажется тйристор 1 ячейкй, снабженной цепью установки йсходного состояния, например первой, С этого момента начинается. заряд кондейсатора 7 через зарядный резистор

6 второй ячейки, фиксирующий диод 9 и открытый тиристор 1. В последующих тактах работы уот- ф{) ройства по аналогичной цепи заряжаются все коммутирующие конденсаторы

7 всех ячеек.

Все разделительные конденсаторы

4, кроме разделительного кондеисатоФормула изобретения

Реверсивный распределитель, содерф5 жащий однОтипные ячейки на запираеЦель изобретения — повышение комму тационной помехоэащищенности и упрощение устройства.

Поставленная цель достигается тем, чтб в каждую ячейку введен фиксирующий диод, катод которого подключен к аноду запираемого тиристора ,этой же ячейки, а анод к общей точке соединения зарядного резистора и комМутирующего конденсатора, причем зарядный резистор соединен с плюсовой шиной источника питания, а коммутирующий конденсатор — с анодом фиксирующего диора последующей ячейки. ра 4 второй ячейки, заряжаются до напряжения источника питания через резисторы 2, 3 и 10.

Прн подаче тактовых. импульсов положительной полярности при условии, что амплитуда последних не превышает величины питающего напряжения, через ,диод 3 и разряженный разделительный конденсатор 4 обеспечивается открывание тиристора 1 второй ячейки. С этого момента начинается формирование фронта импульса напряжения на нагрузке 2 второй ячейки. Одновременно происходит разряд конденсатора 7 первой ячейки через фиксирующий диод

9 второй ячейки, открытый тиристор 1, резистор 10 и разделительный диод 8 первой ячейки. Ток разряда вызывает падение напряжения на резисторе 10 первой ячейки в. запирающем для управляющего перехода тиристора 1 направлении, что приводит к запиранию тиристора 1 первой ячейки.

В это время происходит формирование среза импульса напряжения на нагрузке 2 первой ячейки и начинается переэаряд конденсатора 7 первой ячейки через резистор б, фиксирующий диод 9 и открытый тиристор 1 второй ячейки.

Одновременно происходит заряд коммутирующего конденсатора 7 второй ячейки через зарядный резистор 6 третьей ячейки, фиксирующий диод 9 и открытый тиристор 1 второй ячейки.

Разделительный конденсатор 4 второй ячейки заряжается через резистор

2 первой ячейки и резисторы 3, 10 второй ячейки, а разделительный конденсатор 4 третьей ячейки разряжается через тиристор 1 второй ячейки и резисторы 3, 10 третьей ячейки.

С приходом очередного импульса на входную шину все процессы в схеме пов-, торяются.

При подаче тактовых импульсов на входную шину обратного сЧета все процессы в схеме аналогичны описанным и характеризуются смещением логической единицы справа налево.

Элементы, обеспечивающие реверсивный режим работы распределителя, обозначены значком штрих .

Сравнительный анализ данного распределителя с известньач показал, что в нем частотные свойства тиристоров могут быть реализованы наиболее полно. При этом значительно снижается уровень коммутационных помех в нагрузке, что, в свою очередь, повьыает достоверность работы всего устройства, а также упрощается устройство в целом.

734880!

fl

33

Составитель В. Казаков

Редактор Н. Каменская Техред A.Щепанская Коррек р М. Поко

Заказ 2103/57 Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r, Ужгород. уп Проектная, 4 мых тиристорах с нагрузками в цепи анода, цепи запивания которйх состоят иэ последовательно соединенных за рядного резистора и коммутирующего конденсатора, к общей точке которых через разделительный диод подключен управляющий электрод запираемого ти» ристора, который соединен через резистор с минусовой шиной источника питания, а также с обкладками двух разделительных конденсаторов, другие обкладки которых через "диоды подклю- чены к шинам прямого и реверсивного управления, а через резисторы — к анодам запираемых тиристоров предыдущей и последующей ячеек, о т л и ч а юшийся тем, что, с целью повышения коммутационной помехозащищенности и упрощения, в каждую ячейку введен

Фиксирующий диод, катод которого подключен к аноду запираемого тиристора

Ьтой же ячейки, а анод — к общей точке соединения зарядного резистора и коммутирующего конденаатора, причем зарядный резистор соединен с плюсовой шиной истьчнйка питания, а коммутиру« ющий конденсатор — с анрдом Фиксирующего диода последующей ячейки.

Источники инФормации, принятые Йо внймание прй экспертизе

1. Патент СШй В,3564282; кл. 307/221, опублик. 1971.

2. Вилик P. В. и др. Импульсные схемы на динисторах и тиристорах, М., Наука,- 1968, с. 209 (прототип).