Процессор для цифровой обработки сейсмической информации

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Саюэ Советскик

Сощиелистическик

Республик

<1?36ОЗЗ (61) Дополнительное к авт. свид-ву— (22) Заявлено 01.09.77 (21) 2519714)18-25 с присоединением заявки №вЂ” (23) Приоритет— (51) М, Кл

G 01 N 1)28

G 06 F 15/34

Государственный комитет (53) УДК 550.83 (088.8) Опубликовано 25.05.80. Бюллетень № 19

Дата опубликования описания 28.05.80 аа делам изоБретений и открытий (72) Авторы изобретения

Ю. В. Денисенко, В. М. Кашин и Э. Н. Верем(1з„ (71) Заявитель (54) ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ

СЕЙСМИЧЕСКОЙ ИНФОРМАЦИИ

Устройство касается вычислительной техники и предназначено для использования при обработке сейсмической информации.

Известны специализированные процессоры, предназначенные для обработки геофизической информации, содержащие устройство управления и арифметическое устройство (1).

Наиболее близким по технической сущности к предложенному является процессор для цифровой обработки геофизической информации, который содержит устройство управления, оперативное запоминающее устройство, арифметическое устройство, включающее устройство умножения, суммирующее устройство, блок местного управления арифметического устройства, регистры для временного хранения исходных, промежуточных и выходных данных (2).

Во всех специализированных процессорах основные части арифметического устройства, например, сумматоры, устройства умножения, регистры имеют разрядность, равную одинарной точности обрабатываемой информации, поэтому при выполнении геофизических процедур, требующих двойной точности входных данных, микрооперацин

2 суммирования и умножения производятся поэтапно. Например, в процессоре (2) умножения исходных данных двойной точности на данные одинарной точности выполняются в три этапа. Сначала умножается

5 младшая часть множ«мого на множитель, за тем старшая часть множ11мого на множ«тель после чего на тре;ь и эта«е провод11тcя «одсуммирование к результату в".. р : > эт;: I;: старшей части результата 110рвого эт«; I

Одной из основных операций, выполняс:. !i

1о указанными процессорами, является быстрое преобразование Фурье (БПФ) . Это «и ративный процесс, выполняемый над масс«ваh1 ми чисел величиной N = 2, где число «тсративных циклов равно m. В пределах одной (i + 1)-й итерации над всем массивом для каждой пары точек выполняются два однотипных действия.

AI,+<() = Ас(ф + AI (k) W

Aj.+I (k) = Ac(8) — AI,(k) W, где

i = 1,2,3,,m.

736033

Количество таких действий при прохождении одного массива равно — .

Структура процессора (2) позволяет заключительную фазу решения выражения (1) — сложение и вычитание комплексных чисел — проводить последовательно за четыре цикла алгебраического сложения:

I-и цикл (AI, (т) ) цействит. + (А,(1к) ф) лействит.

2- Й цикл — (А(, (Ф) ) мним. + (А (к) vs) действит.

3-и цикл — (А (Х) ) действит. (А! (й) Уе),действит.

4-й цикл — (А),(т)) мним. — (A<(k)9 ) мним.

Недостатком известных процессоров является большое число этапов при выполнении геофизических процедур, требующих двойной точности входных данных, а также болыцое число циклов сложения при выполнении операции БПФ при вычислении уравнения i1), что значительно увеличивает время обработки геофизической информации.

Цель изобретения — повышение быстродействия процессора.

Для этого в процессоре для цифровой обработки сейсмической информации в арифметическое устройство дополнительно введены сумматор одинарной длины, две схемы

ИЛИ, четыре схемы И и коммутационные схемы. Сумматор одинарной длины по одному из входов через коммутационные схемы соединен с выходом устройства умножения, на котором формируется младшая часть произведения, и по обоим входам с регистрами слагаемых, а выход переноса кз старшего разряда через первую схему ИЛИ и первую схему И соединен с входом переноса в младший разряд сумматора, на котором формируется старшая часть произведения в устройстве умножения.

Выход переноса знакового разряда сумматора, на котором формируется старшая часть произведения в устройстве умножения, соединен с входом переноса в младший разряд этого же сумматора через вторую схему

И и первую схему ИЛИ и с входом в младший разряд дополнительно введенного сумматора через вторую схему ИЛИ и третью схему И, а выход переноса знакового разряда через четвертую схему И и вторую схему

ИЛИ соединен с входом в младший разряд сумматора.

В результате такой организации появляется возможность сокращения числа этапов умножения чисел двойной длины за счет совмещения второго и третьего этапа, т. е. произвести умножение с одновременным подсуммированием. Число циклов сложения при выполнении операции БПФ в заключительной фазе решения уравнения (1) сокращается за счет наличия двух сумматоров, позволяющих совместить во времени первый и второй, третий и четвертый циклы.

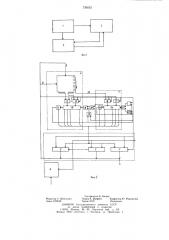

На фиг. 1 изображена структурная схема специализированного процессора; на фиг. 2 — — структурная схема арифметического устройства.

Специализированный процессор содержит оперативное запоминающее устройство

1, у тройство управления 2 и арифметическое устройство 3. Арифметическое устройство содержит блок 4 местного управления, регистры 5 для временного хранения исходных, промежуточных и выходных данных, устроиство 6 умножения и устройство 7 сложения. Устройство умножения имеет вход 8 множи. ля, вход 9 множимого, сумматор 10, на котором формируется старшая часть произведения, дополнительно введенные знаковый разряд 11 этого сумматора и коммутационные схемы 12 и 13 по каждому входу сумматора. Устройство сложения состоит из сумматора 14, знакового разряда 15 этого сумматора, коммутационных схем 16 и 17 по каждому входу сумматора. Вход переноса в младший разряд сумматора )О через схемы ИЛИ 18 и схему И 9 связан с выходом переноса знакового разряда 11 сумматора 10 и через схему ИЛИ 18 и схему И

20 с выходом переноса из старшего разряда сумматора 14. Вход переноса в младший разряд сумматора 14 связан через схему ИЛИ

21 и схему И 22 с выходом переноса знакового разряда 15 сумматора 14. Между выходом устройства умножения, с которого снимается младшая часть произведения, через коммутационную схему 16 установлена связь

23 с входом младшегоразря,д а сумма — îðà 14.

Арифметическое устройство работает в режимах умножения чнсел одинарной д.1нны, умножения чисел двойной длины на число одинарной длины и в режиме суммирования чисел одинарной длины. Каждому режиму соответствует определенная коммутация вычислительной стру ктуры арифметического устройства. В случае умножения чисел одипарной длины по первому управляющему сигналу из блока местного управления сумматор 10 через коммутационные схемы 12 и

13 объединяется с остальной частью устройства умножения в единую множительную структуру, выходы множительного устройства, на которых формируется младшая часть результата умножения, через коммутационную схему 16 соединяется с сумматором 14, выход переноса старшего разряда сумматора 14 через схему И 20 и схему

ИЛИ 18 соединяется с входом переноса в младший разряд сумматора 10. открываются входы 9 и 8 устройства умножения. множимое и множитель поступают в устройство умножения. После поступления сомиожителей на входах устройства умно;гения формуется результат, причем распространение результата идет от младших разрядов к старшим, сначала формируется первый разряд результата умножения, потом второй и т. д. Младшая часть результата умножения благодаря связи 23 проходит через сумматор 14 и появляется иа его входах. Сумматор 10 участвует в формировании старшей части результата умножения. Через время, 736033

Формула изобретекия

55 определяемое задержкой на элементах устройства умножения, результат умножения по другому управляющему сигналу снимается с выходов сумматоров 10 и 14 и = ànîñèòся в регистры арифметического устройства.

Умножение чисел двойной длины на числа одинарной длины происходит в два этапа. Первый этап ничем не отличается от вышеупомянутого умножения чисел одинарной длины, за исключением того, что по первому управляющему сигналу на вход 9 устройства умножения подается младшая часть множимого.

Результат первого этапа по второму управляющему сигналу заносится с выходов сумматоров 10 и 14 в регистры арифметического устройства для временного хранения.

Для выполнения второго этапа умножения по первому управляющему сигналу из блока местного управления производится такая же коммутация, как и при умножении чисел одинарной точНости, за исключением того, что на вход устройства умножения 9 подается старшая часть множимого, дополнительно на второй вход сумматора 14 через коммутационную схему 17 подается содержимое регистра, где хранится старшая часть результата этапа умножения. Таким образом на втором этапе умножения числа двойной точности на одинарную производится умножение с одновременным подсуммированием старшей части первого этапа умножения.

Через время, определяемое задержкой на элементах устройства умножения, на выходах сумматоров 10 и 14 формируется результат второго этапа умноженйя, который в дальнейшем передается в регистры арифметического устройства. Передача младшей части результата умножения через сумматор

14 не увеличивает общее время умножения, так как определяется временем последовательного появления результата умножения на выходе устройства умножения от младших разрядов к старшим. По времени цикл умножения с подсуммированием от цикла умножения чисел одинарной длины не увеличивается, так как в устройстве умножения скорость формирования результата умножения последовательно от младшего разряда к старшему больше, чем скорость распространения переноса в сумматоре 14.

При суммировании чисел одинарной длины, по приходу управляющего сигнала из блока местного управления, в арифметическом устройстве выход .переноса знакового разряда ll сумматора 10 объединяется с входом переноса в младший разряд сумматора 10 через схему И 19 и ИЛИ 18, перенос из знакового разряда сумматора 10 через схему И 19 и ИЛИ 18, перенос из знакового разряда 15 сумматора 14 — с входом переноса в младший разряд сумматора 14. Через коммутационные схемы 12, 13, 16, 17

45 вход; сумм:-оров соединяются с выходами ре петров слагаемых. На выходах сумматоров 10 и 14 формируются суммы. которые затем передаются в регистры арифметического устройства. В режиме работы суммирования чисел одинарной длины за один цикл суммирования производится суммирование двух пар слагаемых.

Таким образом, предложенное устройство позволяет сократить числа этапов умножения чисел двойной длины за счет совмещения второго и третьего этапа. т. е. произвести умножение с одновременным подсуммированием. Такое решение значительно повышает быстродействие процессора при об работке сейсмической информации.

Процессор для цифровой обработки сейсмической информации, содержащее устройство управления, оперативное запоминающее устройство, арифметическое устройство, состоящее из устройства умножения, суммирующего устройства и блока местного управления, регистров для временного хранения входных, промежуточных и выходных данных, отличающийся тем, что, с целью пош.i шения быстродействия, в арифметическое устройство дополнительно введены сумматор одинарной длины, две схемы ИЛИ, четыре схемы И и коммутационные схемы, причем сумматор одинарной длины по одному пз входов через коммутационные схемы соединен с выходом устройства умножения, на котором формируется младшая часть произведения, и по обоим входам с регистрами слагаемых, а выход переноса из c1аршего разряда через первую схему ИЛИ и первую схему И соединен с входом переноса в младший разряд сумматора, на котором формируется старшая часть произведения в устройстве умножения. при этом выход переноса знакового разряда сумматора, на котором формируется старшая часть произведения в устройстве умножения. соединен с входом переноса в младший разряд этого же сумматора через вторую схему И и первую схему ИЛИ и с входом в младший разряд дополнительно введенного сумматора через вторую схему ИЛИ и третью схему И, а выход переноса знакового разряда через четвертую схему И и вторую схему ИЛИ соединен с входом в млалп ий разряд сумматора.

Источники информации, принятые во внимание при экспертизе

1. Процессор МК-1А, Технические условия Яд 3.031.602ТУ, СКБ сейсмической техники, 1976.

2. Процессор ATP фирмы «Raytheon», входящий в комплекс YS-1703-IV фирмы

Jeospace; перевод, трест «Краснодарнефтегеофизика», 1972 (прототип).

736033

Составитель В. Зверев

Редактор A. Шгиелькни Техред К. Шуфрич Корректор Ю. Макаренко

Заказ 2422/38 Тираж 1019 Подлисное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская иаб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4