Устройство для сравнения десятичных чисел

Иллюстрации

Показать всеРеферат

ОПИСА

ИЗОБРЕТЕНИЯ

Союз Советскнк

Социалистических

Республик

36093

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 3),08.77 (21) 2519038/18-24 с присоединением заявки ¹ (23) Приоритет

* Опубликовано 250580. Бюллетень ¹ 14

Дата опубликования описания 2505,80 (51)М. Кл.2

G 06 F 7/04

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. 325.. 5 (088. 8) (72) Авторы изобретения

К.A. Попов, В.Г. Рубанов, И. T. Скибенко и Н. A. Горяйнов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств вычислительной техники и систем автоматического управления и контроля.

Известно устройство для сравнения десятичных чисел, содержащее счетчики, элементы И, ЙЛИ, HE и обеспечивающее последовательное поразрядное сравнение чисел между собой (1).

Недостаток этого устройства— его малое быстродействие.

Наиболее близким техническим реше- 5 нием к предлагаемому является устройство для сравнения десятичных чисел, содержащее два регистра, входами связанные с выходом элемента И, а выходами — со входами элементов памяти соответствующего числа и Входа20 ми соответствующих элементов памяти сравниваемого с ним числа, блок управления тзпросом, входами соединенный с выходами элементов памяти, 25 другие выходы которых через блок формирования результата сравнения связаны с блоком индикации, выходами со входами опроса элементов памяти, и узел контроля, вход которого подключен ко входу элемента И, выход— к другому входу блока управления опросом и ко входу элемента И (2) .

Недостатком этого устройства я вляет ся его сложность.

Пель изобретения — упрощение устройства.

Поставленная цель достигается тем, что в устройстве для сравнения десятичных чисел, содержащем два и-разрядных двоично-десятичных регистра, узел контроля, 2п элементов памяти, схему сравнения, элемент И и узел индикации, причем информационные входы устройства соединены со входами двоично-десятичных регистров, вход тактовых сигналов соединен с перврм входом элемента И, выход которого подключен к управляющим входам двоично-десятичных регистров и к информационному входу узла контроля, выход которого соединен со вторым входом элемента И и со входом управления схемы сравнения, выходы которой подключены ко входам узла инди каци и, выход переполнения каждой i-ой декады, где i = 1 2,...,п первого двоична-десятичного регистра сое73б 093 (динен с информационным входом i-го элеменE3 памяти и с управляющим Elxoдом (n+i) -го элемента памяти, выход переполнения каждой i-ой декады второго двоично-десятичного регистра подключен к информационному входу . (n+i) -ro. элемента памяти и к управляющему входу i-ro элемента памяти„ выходы элементов памяти соединены со входами схемы сравнения.

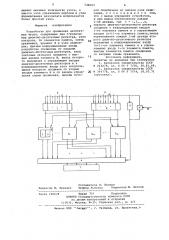

На чертеже приведена блок-схема устройства.

Устройство содержит двоично-десятичные рeãèñòðû 1, 2, элементы 3,, му 4 сравнения, узел 5 контроля,элемент И б, узел 7 индикации, информационные входы 8, 9, вход 10 тактовых си гн ало в.

Устрой ст во работает следующим образом.

При сравнении между со бой чисел

А и В они записываются в двоично-десятичные регистры 1 и

2 в исходном состоянии по информационным входам 8 и 9. При этом в узле 5 контроля записано число 0, каждый элемент 3 памяти находит ся в нулевом со стоянии. Через элемент И б на вход каждого десятичного разряда двоично-десятичных регистров 1, 2 и на вход узла 5 контроля одновременно подает ся по следовательность тактовых сигналов по входу 10 тактовых сигналов. Каждая декада двоично-десятичных регистров

1 и 2 и узел 5 контроля заполняется до переполнения. При этом декада с любым большим по абсолютной величине десятичным разрядом одного числа переполняется раньше декады того же порядка, но с меньшим по абсолютной величине десятичным разрядом другого числа. Иапример, если в i-ых декадах двоична-де сятичных реги стров 1 ч 2 записаны соответственно разряд а; числа А и разряд в; числа В, где а; и в — любые сравниваемые между собой десятичные разряды одинакового порядка чисел A и В, то в случае, если )ц>ф Ь;, раньше переполняется i-ая декада двоичнодесятичного регистра 1 с записанным в нее десятичным разрядом а;, так как для ее переполнения на ее вход нужно подать меньшее количество заполняющих импульсов, чем для переполнения i-ой декады двоично-десятичного регистра 2 и десятичным разрядом в; . Следовательно, импульс переполнения на выходе декады с любым большим пс абсолютной величине десятичным разрядом одного из сравниваемых чисел появляется раньше, чем импульс переполнения на выходе декады того же порядка, но сменьшим,по абсолютной величине десятичным раз— рядом другого и сравниваемых чисел. а1" в а - в ° а-в . а>- в»

l 2 2 I где а„, в — старшие де сятичные разряды сравниваемых чи сел; а;, в; — i--ые десятичные разря— ды сравниваемых чисел; а,, в — младшие десятичные раз. ряды сравни ваемых чисел.

Схема 4 сравнения двоичных чисел сравнивает между собой двоичные раз40 ряды одинакового порядка и по коман— де с узла 5 контроля выдает на узел

7 индикации одну из команд Больше, Меньше, Равно и команду Конец сравнения .

45 Так как в двоично-десятичной декаде узла 5 контроля в исходном состоянии записано число 0, то эта декада определяет максимальное время заполнения двоично-десятичных регистров 1 и 2 до переполнения. Поэтому, если на выходе узла 5 контроля появляется импульс переполнения„идущий на схему 4 сравнения двоичных чисел и на вход элемента

И б, то все де кады двоично-де сятичных регистров 1 и 2 заполняются до переполнения, Импульс переполнения с узла 5 контроля запрещает прохождение через элемент И б заполняющих импульсов и выдает разрешение на индикацию результата сравнения.

Время сравнения определяется частотой поступления заполняющих импульсов и не зависит от разрядности сравниваемых чисел. Устройство со5

Импульс переполнения с выходом

1-ой декады двоично-десятичного регистра 1 с любым большим по абсолютной величине десятичным разрядом одного числа поступает на информацион— ный вход соответствующего i.-го элемента памяти и установит его в единичное состояние.

Этот же импульс переполн ения по ступает н а вход упр авлен и я (п+1) -го элемента памяти и запрещает прохождение импульса переполнения с двоично-десятичного регистра 2.

В случае равенства сравниваемых десятичных разрядов обе двоичнодесятичные декады переполняются одновременно и импульсы переполнения проходят на соот вет ст вующие элементы памяти, Таким образом, по окончании сравнения десятичных разрядов одинакового порядка числа А и В в регистрах

1 и 2 в элементах памяти записываются результаты сравнения в декадах, Исходя .из приведенных выше рассуждений, в случае сравнения чисел

A и В при параллельном заполнении двоично-десятичных регистров 1 и 2 одновременно поразрядно сравни вают ся между собой

73609 3

Формула и зобретения

Составитель B. Белкин

Техред М.Петко Корректор М. нигула

Редактор М. Ликович

Тираж 751 Подпи сное

ЦИИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, F-35, Раушская наб., д. 4/5

Заказ 2266/6

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 держит меньшее количество узлов, а вместо узла управления опросом и узла формирования результата используется более простой узел.

Устройство для сравнения десятичных чисел, содержащее два и-разрядных двоично-десятичных регистра, узел контроля,. 2п элементов памяти, схему сравнения, элемент И и узел индикации, причем информационные входы устройства соединены со входами двоично- десятичных реги стров, вход тактовых сигналов соединен с первым входом элемента И, выход которого подключен к управляющим входам двоично-десятичных регистров и к информационному входу узла контроля, выход которого соединен со вторым входом элемента И и со входом управления схемы сравнения, выходы которой подключены ко входам узла индикации, о т л и ч а ю щ е е с я тем, что с целью упрощения устройства, в нем выход переполнения Каждой

i-ой декады, где i = 1,2,...n первого двоично-десятичного регистра соединен с информационным входом

i-ro элемента памяти и с управляющим входом (n+i) -го элемента памяти, выход переполнения каждой i-ой декады второго двоично-десятичного регистра подключен к информационному входу (n+i) -го элемента памяти и к управ-. ляющему входу i-го элемента памяти, выходы элементов памяти соединены со входами схемы сравнения.

1S Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 263278, кл. G 06 F 7/00, 20.01.69, 2. Авторское свидетельство СССР

Щ Р 394778, кл. G 06 F 7/04 18, 10. 71 (прототип) .