Устройство для контроля последовательности импульсов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕННАЯ

К АВТОРСКОМУ СВИДЕТЕПЬСТВУ ь

l ( (51)М. Кл. (б1) Дополнительное к авт. свид-ву (22) Заявлено120777 (21) 2509774/18-24 с присоединением заявки №

G 06 F -11/00.Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Ьпубликовано2505,80, Б оллетень ¹19

Дата опубликования описания 250580 (53) УДКб 81. 14 (088.8) Г.Е. Бутакова, B.Ô. Волков, A. В. Покровский и А. К. Темник (72) Авторы изобретения

Научно-исследовательский институт электронной интроскопии (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕДОВАТЕЛЬНОСТИ

ИИПУЛЬСОВ

Изобретение относится к области кодирования импульсных последовательностей, а именно к обнаружению нарушений в закономерностях импульсных последовательностей (например, нарушения случайности в флуктуациях амплитуд), и может быть использовано для обнаружения сигнала на фоне случайных помех при анализе последовательности независимых импульсов oïðåделенного объема, Известно устройство обработки информации, в котором в памяти, вы-. полненной на ферритовых сердечниках, хранятся две анализируемые последовательности общим объемом 2N, распо- ложенные с помощью аналого-цифрового преобразователя и схемы сравнения . с соответствующим управлением выводом из памяти и перезаписью в таком порядке, что адреса их по одной координате соответствуют рангу каждого входного импульса в общей последовательности, а ацрес по другой координате соот вет ст вует номеру поступления данного импульса. При считывании из памяти вычисляется разность этих координат, возводится в квадрат, суммируется и сравнивается с порогом для выноса решения о случайности флуктуаций амплитуды (сигнала нет, у = О) или неслучайностг (y=l ) (1)

Недостатком устройства является то, что после аналого-цифрового преобразования, определ ния рангов путем перебора всех элементов в двойной выборке (2N элементов) и сравнения с новым элементом снижается быстродействие устройства, затрудняя использование обнаружителя в реальном масштабе времени, (ель изобретения — повышение быстродей ст ви я за счет со кращени я времени на определение разности между номером импульса в последовательности и его рангом.

Поставленная цель достигается тем, что в устройство для контроля последовательности импульсов, содержащее блок запоминания, блок управления „блок вычитания, квадратор, накопитель, решающий блок и цифроаналоговый преобразователь, причем вход устройства соединен с первыми входами блока запоминания и блока управления, синхрониэирующий вход которого соединен с соответствующим

736 102 входом блэка запоминания, выход квадратора соединен через накопитель с информационным входом решающего блока, управляющий вход которого и управляющие входы накопителя и блока вычитания соединены с соответствующими выходами блока управления, введены амплитудный дискриминатор и счетчик, причем выход блока запоминания соединен с информационными входами амплитудного дискриминатора и счетчика, управляющие входы которых соединены с соответствующими выходами блока управления, а выходы — соответственно с первым и вторым входами блока вычитания, выход которого через цифроаналоговый преобразователь соединен со входом квадратора, и тем, что блок запоминания содержит видикон, соединенный с блоками развертки и гашения, гене-. ратором стирания, блоком смещения начала строки и коммутатором, информационные вход и выход которого являются входом и выходом блока запоминания, управляющие входы блока смещения начала строки, блока разверт ки, блока гашения, блока стирания

:и коммутатора соединены с синхронизирующим входом блока запоминания.

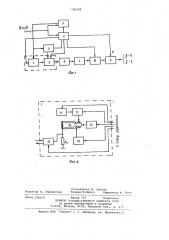

На фиг, 1 предст авлен а блок-схема устройства; на фиг. 2 — блок-схема блока запоминания.

Устрайст во для контроля последовательности импулъсов содержит блок запоминания и блок 2 управления, синхронизирующий вход которого соединен с соответствующим входом блока 1 запоминания, амплитудный дискриминатор 3 и счетчик 4, информационные входы которых соединены с блоком 1 запоминания, управляющие входы — с блоком 2 управления, а выходы — с первым и вторым входами блока 5 вычитания, выход которого подключен через последовательно соединенные цифроаналоговый преобразователь 6, квадратор 7 и накопитель

8, к информационному входу решающего блока 9. При этом вход устройства соединен с первыми входами блока 1 запоминания и блока 2 управления, а управляющие входы блока 5 вычитания, накопителя 8 и решающего блока

9 соединены с соответ ствующими выходами блока управлени я 2.

Кроме того, блок 1 запоминания (фиг. 2) устройства имеет видикон 10, соединенный с блоками развертки 12 и гашения 13, генератором 14 стирания и коммутатором 15, и блок 11 смещения начале строки, который соединен с блоком 12 развертки. Управляющие входы блоков развертки 12, гашения

13, генератора 14 стирания и блока

11 смещения начала строки соединены с синхронизирующим входом блока

1 запоминания, вход и выход которогс

1 стиранием участка с устаревшей информацией и записью на его место новой. При этом начало считывания для обработки перемещается на один участок. Таким образом, в конце каждого цикла считывания один участок мише—

20 ни стирается и развертка записи начинаетсяя с этого участ ка. После з апи си нового си гн ала, по команде из блока 2 управления, коммутатор

15 переключает видикон 10 на считы 5 ванне с участка следующего за вновь записанным. Определение рангов проис— ходит автоматически с помощью амплитудного дискриминатора 3 с дешифратором положения — двоичный код на выходе, имеющеro N каналов, который выдает после поступления каждого импульса двоичный код. Двоичный код далее поступает в блок 5 вычитания (блок реверсивного счета) . Ширина общего окна канала амплитудного дискриминатора 3 выбирает ся равной корню квадратному из дисперсии исследу— емого входного сигнала, и в процессе обработки не н астраи вает ся . Настройка ширины общего окна производится

4() только при переходе к исследованию процессов с другими статическими характери сти ками. Уровен ь пора га нижнегоа окна амплитудного дискримина тора 3 задается из блока 2 управления

65 являются информационным входом и выходом коммутатора 15 .

Устройство работает следующим образом.

Амплитуда входного импульсного сигнала з аписы вает ся B соот вет ст вующей точке мишени види кон а 10 в виде потенциала. Строка мишени условно разбита на участки, B которых располагают ся соот вет ст вующие входным импульсам заряды. Число их зависит от объема выбор ки (т . е . от вероят HocT ных характеристик) . Память на видиконе работает в динамическом режиме со и является плавающим . Входной процесс в блоке 2 управления интегрируется с постоянной времени, большей длительности одной выборки, и это значение поступает на питание делителей опорного напряжения амплитудного дискриминатора 3. Источни к эталон ного напряжения находит ся в блоке 2 управления. Сравнение эталонных з начений с текущими о суще ст ьляет ся на входе амплитудного дискриминатора 3. Если входной сигнал выше некоторого порога, то он фиксируется соот вет отвующим каналом амплитудного дискриминатора и на его выходе появляется сигнал,. пространственное положение (номер канала) которого сост вет ст вует е го ран—

„гу и кодируется на выходе амплитудного дискриминатора 3 дешнфратором в двоичном коде. Разность м =жду рангом и номером прихода ана 1н..нруемого

736102 импульса на выходе блока 5 вычитания преобразуется в блоке 6 в аналоговую величину (напряжение), которая возводитсяя в квадрат в блоке 7 и накапливается в течение строки считывания в блоке 8. Подачей сигнала из блока

2 управления 2 в накопитель 8 происходит выдача результата на решающее устройство 9, которое выдает результат у =1, если сумма больше порога

К, и у =О, если сумма меньше порога

К. Затем происходит сброс накопителя

8 в нуль. Одновременно с этим генератор 14 стирания и блок 13 гашения стирают первый из исследуемой выборки элемент. Блок 11 смещения начала строки с помощью блока 12 раз- 15 верт ки уст анавли вает начало строки записи в положение стертого элемента.

После записи по команде из блока 2 управления 2 коммутатор 15 переключает види кон 10 на считывание с участ- () ка сЛедующего за вновь записанным, процесс считывания повторяется в описанном порядке.

Определение рангов элементов выборки происходит за одно считывание элемента, беэ перебора всех элементов.

Анализ в устройстве производится непрерывно после прихода каждого импульса на его вход. Продолжительность обработки информации в выборке определяют частоту следования входных импульсов. Организация динамического режима запоминающего устройства и сокращение времени на вычисление статистики устройства с дешифратором положения — двоичный код на выходе и счетчика позволяет обеспечить большее быстродей ст вие „чем устройство с определением рангов путем последовательного перебора всех элементов двух выборок. 40

Кроме того, в устройстве величина порога зависит только от двух параметров: d — заданной вероятности ложных тревог и N. В случае расширения диапазона использования устройства при различных и N в блоке управления можно предусмотреть клавишную матрицу, столбцы которой соответствуют значениям о, строки-N. При нажатии любой клавиши меняется порог К.

Формула изобретения

1. Устройство для контроля последовательности импульсов, содержащее блок запоминания, блок управления, блок вычитания, квадратор„ накопитель, решающий блок и цифроаналоговый преобразователь, причем вход устройства соединен с первыми входами блока запоминания и блока управления, синхрониэирующий вход которого соединен с соответствующим входом блока запоминания, выход квадратора соединен через накопитель с информационным входом решающего блока, управляющий вход которого и управляющие входы накопителя и блока вычитанияя соединены с соот вет ст вующими выходами блока управления, о т л ич ающе е с я тем,что, сцелью повышения быстродействия, в него введены амплитудный дискриминатор и счетчик, причем выход блока запоминания соединен с информационными входами амплитудного дискриминатора и счетчика, у травляющие входы которых соединены с соответствующими выходами блока управления, а выходы— соответ ственно с первым и вторым входами блока вычитания выход которого через цифроаналоговый преобразователь соединен со входом квадратора.

2. Устройство по п.1, о т л ич ающе е с я тем, что блок запоминания coäåðæèò видикон, соедиI ненный с блоками развертки и гашения, генератором стирания, блоком смещения начала строки и коммутаторам, информационные вход и выход которого являются входом и выходом блока запоминания, управляющие входы блока смещения начала строки, блока раз верт ки, блока гашения, блока стирания и коммутатора соединены с синхронизирующим входом блока запоминания.

Источники информации, принятые во внимание при экспертизе

1. Неразрушающие методы и средства контроля и их применение в промышленности .. Минск, 1973, с. 362 (прототип) .

736102

=О

Редактор В. Зарванская

Заказ 2266/6

«З

Ъ< о

С С:1

Составитель И. Хазова

Техред 14,Петко Корректор М. Пожо

Тираж 751 Подпи сное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, F-35, Раушская наб., д. 4/5

Филиал ППП Патен, г. Ужгород, ул. Проектная 4