Устройство для регистрации стационарных и нестационарных участков случайного процесса

Иллюстрации

Показать всеРеферат

Союз Соеетскик

Социапистическик

Республик

ОП ИСАН.ИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и; 736117

Ф ф (6I ) Дополнительпое к авт. свид-ву — . (22)Заявлено 16.05.77 (21) 2485766/18-24 (51)M. Кл.

G 06 Р Х5/Э6 с присоединением заявки J%—

Государственный комитет (23) Приоритет— до делам изобретений и открытий

Опубликовано 25.05.80.Бюллетень № 18 (53) УД f(681.325 (088.8) Дата опубликования описания 28.05.80 (72) Автор изобретения

В. Н. Терентьев (7I) Заявитель (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ

CTAIINOHAPHbIX H HECTALIHOHAPHbIX

УЧАСТКОВ СЛУЧАЙНОГО ПРОКЕССА

Изобретение относится к вычислитель ной технике и предназначено для определения стационарных и нестационарных участков информации из общего информационного потока случайного процесса.

Известно устройство для определения характеристик случайного процесса, содержащее блок управления, логический блок, блок задания начальных значений, блок формирования, блок запоминания (11

Недостатки устройства - сложная структурная схема и низкое быстродействие и невозможность осуществлении контроля информации.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее блок памяти, первый выход которого соединен со входом блока сравнения, второй выход блока па» мяти подключен ко вхоцу блока контроля, первый и второй дифференцирующие блоки, пороговый блок, формирователь прямоугольного сигнала, регистрирующий блок t2).

Недостаток устройства — низкая точность определения стационарных и нестационарных участков случайных процессов.

Цель изобретения повышение точ ности определения стационарных и песта» ционарных участков случайных процессов.

Кель достигается тем,. что в устрой ство дополнительно введены первый и вто рой интеграторы, блок умножения, второй пороговый блок,, первый и второй пере- ключатели, первый и второй элементы И, причем третий выход воспроизводящего блока подключен к информационному входу первого переключателя, управляющий вход которого соединен с первым выходом формирователя прямоугольного сиг» нала, выход которого подключен к управляющему входу второго переключателя, выходы первого и второго переклю-чателей соединены соответствующими входами регистрирующего блока, информа дионный вход второго переключателя под736117

3 ! ключен к выходу первого элемента И, первый и второй входы которого соедииены соответственно с выходами блока сравнения и блока контроля, первый вы ход блока памяти подключен ко входам

5 первого интегратора и блока умножения, выход первого интегратора через последовательно соединенные первый дифференцирующий блок и первый пороговый блок подключен к первому входу второго эле- j(j мента И, второй вход которого через последовательно соединенные второй интегратор, второй дифференцирующий блок и второй пороговый элемент подключен к выходу. блока умножения, выход второго 15 элемента И соединен со входом формирователя прямоугольного импульса.

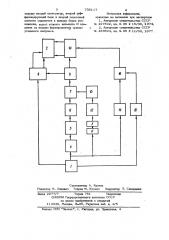

На чертеже представлено описываемое устройство.

Оно содержит блок 1 памяти, регистри- 2о рующий блок 2, интеграторы 3, 4, дифференцирующий блок 5, пороговый блок 6,, элемент И 7, формирователь 8 прямоугольного, импульса, перекоючатели 9, 1 О, блок 1 1 умножения, дифференцирующий 25 блок 12, пороговый блок 13, блок 14 сравнения, блок 15 контроля, элемент

И 16.

Устройство работает следующим образом.

Сигнал из блока 1 памяти одновременно поступает на входы интегратора 4, блока 1 1 умножения, блока 1 4 сравнения и блока 15 контроля. С выхода интеграто35 ра 4 текущее среднее значение поступает на дифференцирующий блок 5, с выхода которого сигнал, в случае изменения среднего значения случайного процесса, ереэ пороговый блок 6 подается на один из о входов элемента И 7.

С выхода интегратора 3 текущее значение автокорреляционной функции поступает на дифференцирующий блок 12, 45 с выхода которого сигнал, в случае изменения автокорреляционной функции, через пороговый блок 1 3 подается на другой вход элемента И 7.

С выхода элемента И 7 сигнал по

50 ступает на формирователь 8 прямоугольного импульса,- один из выходов которого соединен с одним из входов переключателя 9, а другой - с одним иэ входов переключателя 1 О. Параллельно с опре55 делением признака нестационарности осуществляется определение содержательности информапии блоком 12 и определение достоверности информации блоком 13»

При наличии содержательной и достоверной информации с выходов блоков 14 и 15 сигналы поступают на входы элемента И 16, с выхода которого сигнал поступает на другой вход переключателя

10.

Комбинация сигналов на выходах переключателей 9 и 10 задает режим регистрации для блока 2. Таким образом, осуществляется регистрация стационарHbIK и нестационарных участков случайного процесса.

Предлагаемое устройство благодаря наличию новых элементов и связей между ними позволяет осуществлять-регистрацию стационарных и нестационарных участков случайного процесса.

Формула и э о б р е т е н и я

Устройство для определения стационарных и нестационарных участков слу-. чайного процесса, содержащее блок памяти, первый выход которого соединен со входом блока сравнения, второй выход блока памяти подключен ко входу блока контроля, первый и второй дифференцирующие блоки, пороговый блок, формирователь прямоугольного сигнала, регистрирующий блок, о т л и ч а ющ е е с я тем, что с целью повьпцения точности, в устройство дополнительно введены первый и второй интеграторы, блок умножения, второй пороговый блок, первый и второй переключатели, первый и второй элементы И, причем третий выход блока памяти подключен K информационному входу первого переключателя, управляющий вход которого соединен с первым выходом формирователя прямоугольного сигнала, выход которого подключен к управляющему входу второго переключателя, выходы первого и второго переключателей соединены с соответствующими входами регистрирующего блока, информационный вход второго переключателя подключен к выходу первого элемента И, первый и второй входы которого соединены соответственно с выходами блока сравнения и блока контроля, первый выход блока памяти подключен ко входу первого интегратора и блокка умножения, выход первого интегратора через последовательно соединенные первый дифференцирующий блок и первый пороговый блок подключен к первому выходу второго элемента И, второй вход которого через последовательно соеди736ii7

5 ненные второй интегратор, второй дифференцирующий блок и второй .пороговый элемент подключен к выходу блока умножения, выход второго элемента И соединен со входом формирователя прямоугольного импульса.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 497592, кл. G 06 Р 15/36, 1974.

2. Авторское свидетельство СССР

% 453694, кл. Ь 06 F 11/00, 1977, Составитель А. Колчин

Редактор М. Ликович Техред М. Кузьма Корректор Т. Скворцова .

Заказ 2277/7 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб. д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4