Логарифмический аналого-цифровой преобразоватль

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (1»736132

ИЗОБРЕТЕН ИЯ

Союз Советскик

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6() Дополнительное к авт. свил-ву (22)Заявлено 16.01.78 (2() 2570780/18-24 (5 I ) M. Кл, С, 06 3/00

i присоединением заявки Р(Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 25.05.80. Бюлоетеиь р(о 19

Дата опубликования описания 28.05.80 (53) УДК 681..335.813 (088.8) (72) Авторы изобретения

А. И. Фесенко, Г. В. Крндратьев и В. С. Борисюк (7() Заявитель (54) ЛОГАРИФМИЧЕСКИЙ АНАЛОГО-ЦИФРОВОЙ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к вычислительной технике и может быть использовано для построения логарифмируюших и множительно-делительных устройств.

Известен логарифмический аналого-цифровой преобразователь, содержаший счет5 чик, источник опорных напряжений, выходы которого соединены с одними входами ключей, к другим входам которых подключен выход блока управления, выходы од(о ной пары ключей подключены к первому входу интегратора, выход которого соединен со входом элемента сравненья (. 1).

Недостаток такого преобразователя— низкая точность воспроизведения лога рифмической зависимости.

Наиболее близким техническим решением к изобретению является логарифмический аналого-цифровой преобразователь, 20 содержал.ий счетчики, элемент сравнения, первый вход которого соединен со входом преобразователя, генераторы опорного напряжения, выход первого из которых соединен с первыми входами первого и второго ключей, а выход второго — с первыми входами третьего и четвертого ключей (21 .

Недостаток этого преобразователясравнительно малая точность и относительно невысокое быстродействие, обусловленные наличием на выходе дополнительного интегратора начального напряжения перед началом цикла работы и записьто. в счетчик ложной единицы в момент начала ра-. бот ы.

Цель изобретения — повышение точности работы преобразователя и его быстро» действия.

Поставленная цель достигается тем, что устройство содержит элементы И, элементы ИЛИ, блоки запаздывания, триггеры, регигтр и блок преобразования код-аналог", входы которого соединены с выходами первого счетчика и входами первого элемента И, выход блока преобразования код-аналог соединен со втос третьими входами второго и третьего ключей и с третьим входом второго счетчика, выходы первого и третьего ключей соединены со входами второго элемента 20

ИЛИ, выход которого подключен к третьему входу второго счетчика, выходы второго и <четвертого ключей соединены со входами третьего элемента ИЛИ, выход которого подключен к четвертому входу первого счетчика, второй вход первого элемента ИЛИ подключен к выходу второго элемента И и третьему входу третьего счетчика, выход которого соединен со входом регистра, выход первого элемента ИЛИ соединен с первым входо<< второго триггера, второй вход которого соединен с выходом первого элемента

И, выходы второго счетчика соединены

ro входами второго элемента И.

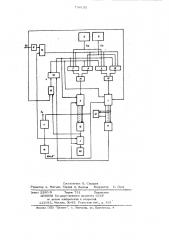

На чертеже приведена блок-схема устройства.

Логарифмический аналого-цифровой преобразователь содержит счетчики 1, 2 и 3; элемент 4 сравнения, первый вход которого соединен со входом преобразователя, генераторы 5 и 6, опорного напряжения, выходы которых соединены со входами соответствующих ключей 7, 45

8, 9 и 10. Кроме того, он содержит элементы И 11 и 12, элементы ИЛИ 13, 14 и 15„блоки 16 и 17 запаздывания, триггеры 18 и 19, регистр 20 и блок

21 преобразования код-аналог". Вкод

50 запуска преобразователя обозначен цифрой .22.

Г1реобразователь работает следующим образом.

На вход 22 запуска преобразователя

«о<-.тупиет импульс, который устанавлива- .т в счетчике 1 (реверсивный счетчик) код « о заранее заданного числа и, одновременно, через элемент ИЛИ 15

3 736 рым входом элементи сравнения, выход которого через первый блок запаздывания соединен с первыми входами первого, второго и третьего счетчиков, второй вход третьего счетчика соединен с выходом элемента сравнения и первым входом первого триггера, второй вход которого через второй блок запаздывания соединен со вторым входом первогс счет. чика и первым входом первого элемента

ИЛИ, выход первого триггера подключен ко вторым входам ключей, третьи входы первого и четвертого ключей подключены к прямому выходу второго триггера и второму входу второго счетчика, а ин- 15 версный выход второго триггера соединен

132 4 переключает триггер 18 в единичное состояние или подтверждает это состояние. При этом на вход режим работы. счетчика 1 с инверсного выхода триггера

18 поступает логический нуль, а на вход режим работы счетчика 2-логическая единица .. Состоянию логический нуль на входах счетчиков 1 и 2 соответствует режим вычитан ия, а со стоян ию "ед ин ица"— режим суммирования импульсов. После прохождения импульса запуска через элемент

17запаздывания триггер 19 переключается в единичное состояние и открывает ключи 7 и 10. Ключи 8 и 9 при этом закрыты логическим нулем с инверсного выхода триггера 18. На выходах элементов ИЛИ 13 и 14 начинают формироваться потоки импульсов от генераторов 6 и 5 с частотами f о1 и f о, которые поступают на основные входы счетчиков 1 и 2. Счетчик 1 работает в режиме вычитания, а счетчик 2 — в режиме суммирования. В счетчик 1 записывается число «, = N - f t, где t — время, а в счетчик 2 — число N — 1о„° t

В момен т времени t 1 происходит обнуление счетчика 1, а на выходе элемента И 11 формируется импульс, который переключает триггер 18, закрывающий своими выходами ключи 7 и 10, открывающий ключи 8 и 9 и переводящий счетчик 1 в режим суммирования, а счетчик 2 — в режим вычитания. В. счетчике

2 при этом записывается число N = 1о t<, В следующий. момент времени на вход счетчика 1 поступают импульсы с частотой fо через ключ 9 и элемент ИЛИ

13, а на вход счетчика 2 — импульсы с частотой Й< через ключ.8 и элемент

ИЛИ 14. Числа, записываемые в счетчике 1 и 2, равны

<" < ог. г ох < о< - °

После обнуления счетчика 2 е момент времени 1 в счетчике 1 записывается число Q < — f o î с учетом о<

0<

В суммирующем счетчике 3 записывается "единица с выхода элемента. И 12 и одновременно через элемент ИЛИ 15

736132 сано число

Равенство напряжений на входах элемента 4 сравнения с выхода блока 21 и вкодного Uz определяет соотношения 25

N к =е. „„—,, где о

Ux

К = 40(y где х и Бо- 30 о

Или

I I соответственно преобразуемое напряжение и напряжение, принимаемое часто .за единицу.

Предложенное устройство позволяет 35 повышать точность преобразования и быстродействие по сравнению с известным устройством, исключив полностью временную и температурную нестабильности,, запись ложной "единицы в счетчик,.а также ошибки регистрации нулевых значений интегратора за счет применения элементов дискретной вычислительной техники и начале работы преобразователя по логарифмированию входного сигнала не- 45 посредственно в момент запуска. . Формула изобр етен ия

Логарифмический аналого-цифровой преобразователь, содержащий счетчики, элемент сравнения, первый вход которого

50 соединен со входом преобразователя, и генераторы опорного напряжения, выход первого из которых соединен с первыми осуществляется переключение триггера

18. Далее описанный цикл работы преобразователя повторяется до тех пор, пока сигнал с выхода блока 21 преобразования код-аналог" не станет равным Ug на входе элемента 4 сравнения. В этом случае на выходе элемента 4 сравнения формируется импульс, который осушествляет перенос числа из счетчика 3 в регистр 20, переключение триггера 19 t0 в нулевое состояние и через элемент запаздывания 16 устанавливает счетчики 1, 2 и 3 в нулевые состояния (подтверждая эти состояния и исключая накопление ошибки от случайных помех в l5 процессе работы). При числе К, записанном в счетчике 3, в счетчике 1 запивходами первого и второго ключей, а выход второго — с первыми входами третьего и четвертого ключей, о т л и— чаюшийся тем,чтo,сцелью повышения точности и быстродействия, он содержит элементы И, элементы ИЛИ, блоки запаздывания, триггеры, регистр и блок преобразования код-аналог", входы которого соединены с выходами первого счетчика и входами первого элемента И, выход блока преобразования "код-аналог, соединен со вторым входом элемента сравнения, выход которого через первый блок запаздывания соединен с первыми входами первого, второго и третьего счетчиков, второй вход третьего счетчика соединен с выходом элемента сравнения и первым входом первого триггера, второй вход которого через второй блок за-, паздывания соединен со .вторым входом первого счетчика и первым входом первого элемента ИЛИ, выход первого триггера подключен ко вторым входам ключей, гретьи входы первого и четвертого ключей подключены к прямому выходу второго триггера и второму входу второго счетчика, а инверсный выход второго триггера соединен с третьими входами второго и третьего ключей и с третьим входом второго счетчика, выходы первого и третьего ключей соединены со входами второго элемента ИЛИ, выход которого подключен к третьему входу второго счетчика, выходы второго и четвертого ключей соединены со входамн третьего элемента

ИЛИ, выход которого подключен к четвертому входу первого счетчика, второй вХод первого элемента .ИЛИ подключен к выходу второго элемента И и третьему входу третьего счетчика, выход которого соединен со входом регистра, выход первого элемента ИЛИ соединен с .первым входом второго триггера, второй вход которого соединен с выходом первого элемента И, выходы второго счетчика соединены со входами второго элемента M.

Источники информации, принятые во внимание при эксперти. о

1. Авторское свйдетельство СССР

hfo 424171, кл. (» 06 Q 7/24, 1974.

2. Авторское свидетельство СССР

% 547785, кл. С 06 G 7/24, 1977

{ прототип) .

73(>132

Составитель О. Сахаров

Редактор А. Мотыль Техред Q. Дегеза Корректор Е:. Папп

Заказ 2280/9 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскаи наб., д. 4/5 филиал ППП Патент", r, Ужгород, ул, Проектная, 4