Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскнк

Соцналнстнческнк

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ, iii736173

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.11.77 (21) 2540288/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

G 11 С 27/00

Гооуднрстеенный комитет

Опубликовано 25.05.80. Бюллетень № 19

Дата опубликования описания 28.05.80 (53) УДК 681.327..66 (088.8) ао делам изобретений и открытий (72) Авторы изобретения

С. П. Семенищев и С. П. Зимин (71) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСТВО

+ 3к + 13@( квк

Изобретение относится к вычислительной и измерительной технике и может быть использовано в устройствах запоминания и последующего преобразования уровня напряжения.

Известно аналоговое запоминающее устройство, содержащее усилитель. накопительный конденсатор (1). В таких устройствах точность запоминания ограничена дрейфом нуля и нелинейностью характеристик уси-, лителя. Кроме того, из-за конечного значения входного сопротивления усилителя время хранения запоминаемого напряжения невелико.

Наиболее близким к изобретению по технической сущности является аналоговое запоминающее устройство, содержащее накопительный конденсатор, усилитель тока с коэффициентом усиления по напряжению, равным 1, источник тока и регулировочные резисторы (2). В этом устройстве источник тока и резисторы позволяют получить компенсирующий ток любой величины.

В общем случае ток разряда конденсатора состоит из двух составляющих где Jp — ток разряда конденсатора;

UK — заряд конденсатора;

R — собственное сопротивление утечки конденсатора;

Кок в входное сопротивление усилителя;

U — входное напряжение усилителя.

Используя конденсаторы с полистирольным диэлектриком, токами утечки можно пре10 небречь. Вторая составляющая ф - при разных U < будет изменяться, поэтому полная компенсация по предложенной схеме осуществима только при одном значении

Это значит, что достаточно высокая точ15 ность работы и время хранения запоминания будут лишь на ограниченном участке диапазона.

Целью изобретения является повышение точности и увеличение времени хранения на гв широком диапазоне.

Достигается это тем, что в аналоговое запоминающее устройство, содержащее накопительный элемент например, конденсатор, одна обкладка которого соединена с шиной

7361 73 нулевого потенциала, другая обкладка конденсатора подключена к неинвертирующему входу дифференциального усилителя, ключ, например транзистор, выход дифференциального усилителя соединен с базой транзистора, эмиттер транзистора соединен с отрицательной шиной питания, первый резистор, один вывод которого подключен к положительной шине питания, второй резистор., один вывод которого подключен к другой обкладке конденсатора, введены два элемента стабилизации, например стабилитроны, третий и четвертый резисторы, один вывод третьего резистора соединен с первым входом питания дифференциального усилителя, с коллектором транзистора и анодом первого стабилитрона, катод которого соединен с выходом устройства, с инвертирующим входом дифференциального усилителя и с анодом второго стабилитрона, катод второго стабилитрона подключен к другому выводу первого резистора, к одному из выводов четвертого резистора и второму входу питания дифференциального усилителя, другой вывод второго резистора подключен к другим выводам третьего и четвертого резистора.

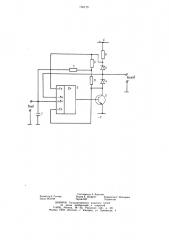

На чертеже изображена электрическая схема предложенного устройства.

Устройство содержит накопительный элемент, например конденсатор 1, дифференциальный усилитель 2, ключ, например транзистор 3, элементы стабилизации, например стабилитроны 4 и 5, элемент нагрузки, например первый резистор 6, компенсирующий элемент, например второй резистор 7, делитель напряжения, выполненный на третьем и четвертом резисторах 8 и 9. Вход устройства подключен к неинвертирующему входу усилителя 2 и обкладке конденсатора 1.

Выход усилителя 2 соединен с базой транзистора 3, в нагрузочной цепи которого последовательно соеди нены стабилитроны 4 и 5 и резистор 6. Вход делителя напряжения шунтирует стабилитроны 4 и 5, а выход через резистор 7 образует цепь компенсации разряда конденсатора 1. Шины питания дифференциального усилителя 2 подключены к входу делителя. Инвертирующий вход дифференциального усилителя 2 подключен к точке соединения стабилитронов 4 и 5 и является выходом устройства.

Устройство работает следующим образом.

При заряде конденсатора 1 до напряжения 11вх на выходе усилителя 2 появляется напряжение, управляющее транзистором 3, который открывается или закрывается в зависимости от полярности входного напряжения до тех пор, пока не сравняются потенциалы входов дифференциального усилителя 2, при этом U будет равно Бвх.

Напряжение питания дифференциального усилителя 2 снимается со стабилитронов

4 и 5 и стабилизировано относительно уровня запоминаемого напряжения, следовательно, и входное напряжение усилителя 2 и входной ток постоянны на всем диапазоне работы. Этот ток компенсируется током компенсации, подбираемым с помощью делителя напряжения, в качестве которого может быть использован потенциометр.

Предлагаемое устройство проще известных и обладает высокими точностными характеристиками и большим временем хранения.

$ о

Формула изобретения

Аналоговое запоминающее устройство, содержащее накопительный элемент, например, конденсатор, одна обкладка которого соединена с шиной нулевого потенциала, другая обкладка конденсатора подключена к нгинвертирующему входу дифференциального усилителя, ключ, например транзистор, выход дифференциального усилителя соединен с базой транзистора, эмиттер транзистора соединен с отрицательной шинои питания, элемент нагрузки, например первый резистор, один вывод которого подключен к положительной шине питания, компенсирующий элемент, выполненный на втором резисторе, один вывод которого подключен к другой обкладке конденсатора, отличаюи ееся тем, что, с целью повышения точности и увеличения времени хранения устройства, в него введены два элемента стабилизации, например стабилитроны, делитель напряжения, выполненный на третьем и четвертом резисторах,:один вывод третьего резистора соединен с первым входом питания дифференциального усилителя, с коллектоИсточники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 504248, кл. G 11 С 27/00, 12.09.74.

2. Авторское свидетельство СССР № 453740, кл. G 11 С 27/00, 06.12.72 (прототип) . ром транзистора и анодом первого стабилитрона, катод которого соединен с выходом устgg,ройства, с инвертирующим входом дифференциального усилителя и с анодом второго стабилитрона, катод второго стабилитрона подключен к другому выводу первого резистора, к одному из выводов четвертого резистора и второму входу питания дифференциального усилителя, другой вывод второго резистора подключен к другим выводам третьего и четвертого резисторов.

736173

/xod

Составитель А. Воронин

Редактор Е. Гончар Техред К. Шуфрич Корректор Г. Назарова

Заказ 2433/40 Тираж 662 Подписное

ЦНИИ ПИ Государственного комитета СССР по делам изобретений и открытий

l 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <Патент> г. Ужгород, ул. Проектная, 4