Устройство для сохранения информации в памяти при отключении питания

Иллюстрации

Показать всеРеферат

Союз Советских

Соцмалистическик республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

,736178 (6! } Дополнительное к dBT. свил-ву (51}M, Кл.

6 11 С 29/00 (22)Заявлено 24.11.77 (21) 2546729/18-24 с присоединением заявки,%

Государственный комитет (23 } П риори гет ао делатв изобретений н открытий

Опубликовано 25,05.80. Бюллетень И 19

Дата опубликования описания 28.05.80 (53} У1 K

681. 127 (088.8) (72} Авторы изобретения

В. Е. Ганшин, Л. А. Колосков, В. М. Константиновский, Ю. Л. Усов и Б. М. Ямпольский (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СОХРАНЕНИЯ ИНФОРМАПИИ В ПАМЯТИ

ПРИ ОТКЛЮЧЕНИИ ПИТАНИЯ

Изобретение относится к области запоминающих устройств.

Известны устройства для сохранения информации в памяти при отключении питания.

Одно из известных устройств содержит кас5 кад сброса, пороговые каскады и позволяет обеспечить сохранение информации при отключении питания в запоминающем устройстве 11).

Однако в запоминающем устройстве может происходить частичное разрушение инфор1О мации непосредственно в момент отключения питания в случае прихода в этот момент импульса обращения.

Из известных устройств наиболее близким техническим решением к изобретению является

15 устройство для сохранения информации в памяти при отключении питания, содержащее источники питания, входы которых соединены с выходом первого ключа, вход которого соединен со входом устройства, фильтр, вход которого подключен к выходу первого источника питания — ко входам источников опорного напряжения, второй ключ, вход которого соединен с выходом второго источника питания, а вы2 ход — с одним из выходов устройства, блоки сравнения, одни входы которых подключены к выходам источников опорного н1пряжения, другие входы соответственно -- к выходам источников питания и входу устройства,а выходы блоков сравнения соединены со входами элемента ИЛИ, временной селектор, вход которого подключен к выходу элемента ИЛИ, один выход через элемент задержки — к управляющему входу первого ключа, другой выход — к первому входу генератора одино щых импульсов, второй вход которого соединен с выходом источника тактовы импульсов, и управляющиешины (2) .

Недостатком этого устройства является возможность частичного стирания информации в момент отключения питания. Это объясняется тем, что отклонение питания адресных и разрядных цепей должно происходи1ь и происходит быстрее, чем откли>чение целей питания логических элементов, и если это время соизмеримо с времененисм цикла обрэтцения при перезаписи, то перезапись может прои водиться при уменьшенном (на фронте о1к:Iloчсния) 736178

35 значении питания адресных и разрядных цепей, что снижает надежность устройства, Целью изобретения является повышение надежности устройства.

Это достигается тем, что устройство содержит элементы И, элемент ИЛИ вЂ” HE, элемент

И вЂ” НЕ, триггер и счетчик, выход которого соединен с управляющим входом второгс ключа; один из входов — с выходом источника тактовых импульсов, другой вход — с первым 10 входом элемента И вЂ” HE и выходом триггера, вход которого подключен к в входу генератора одиночных импульсов, одни входы элементэв И соединены с управляющими шинамидругие — c выходом элемента И вЂ” HE, а выходы — с други- 15 ми выходами устройства и входами элемента

ИЛИ вЂ” НЕ, выход которого подключен ко второму входу элемента И вЂ” НЕ.

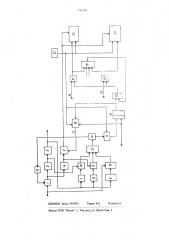

На чертеже представлена схема предложенного устройства. 20

Устройство содержит первый ключ 1, второй ключ 2, источники питания, например первый выпрямитель 3 и второй выпрямитель 4, фильтр 5, элемент задержки 6, первый источник опорного напряжения 7, второй источник опорного напряжения 8, третий источник опорного напряжения 9, первый 10, второй 11 и третий 12 блоки сравнения, элемент ИЛИ 13, временной селектор 14, генератор одиночных импульсов 15, счетчик 16, имеющий выход 17, эо элемент ИЛИ вЂ” НЕ 18, триггер 19, элемент И вЂ” НЕ

20„элементы И 21 и источник тактовых импульсов 22.

К выходам устройства подключены блоки памяти 23. Выход 17 счетчика 16 соединен с управляющим входом второго ключа 2, один из входов — с выходом источника тактовых импульсов 22; другой вход — с первым входом элемента И вЂ” НЕ 20 и выходом триггера

19, вход которого подключен к выходу генератора одиночных импульсов 15. Одни входы элементов И соединены с управляющими шинами 24, на которые подается импульс обращения, другие входы — с выходом элемента

И вЂ” НЕ 20, а выходы — с выхода пт устройnsa и входами элемента ИЛИ вЂ” НЕ 18, выход которого подключен ко второму входу элемента И вЂ” НЕ 20.

Устройство работает следующим образом.

Напряжение сети, поступающее на вхсд устройства с первого ключа 1, подается на вы. прямитель 3 и 4. С выхода фильтра 5 выпрямленное напряжение подается на исто шики опорного напряжения 7 — 9. На блоки сравнения

10 и 11 подаются напряжения с выходов выпрямителей 3 и 4, а также с выходов источников опорных напряжений 7 и 8.

На блок сравнения 12 подаются напряжение сети и напряжение с выхода источника onopvoro напряжения 9. На элементах ИЛИ 13 собираются сигналы с выходов блоков 10 — 12, Тактовые импульсы с источника тактовых импульсов -22 поступают на блоки памяти 23, «а счетчик 16 и на генератор одиночных импульсов 15. Импульсы обращения> синхронные с тактовой частотой, через элементы И 21 поступают на блоки памяти 23. Кроме того, импульсы обращения собираются на элементе

ИЛИ вЂ” HE 18 и поступают на элемент И вЂ” HE 20.

При отключении питания во временном селекторе 14 вырабатывается сигнал, возбуждающий генератор одиночных импульсов 15.

Импульс с генератора одиночных импульсов

15 в свою очередь воздействует на вход триггера 19„в результате триггер 19 из ".нулевого" состояния переходит в "единичное".

Если отключение питания происходит в момент времени, соответствующий наличию импульса обращения на входе одного из элементов И 21, то на выходе элемента И вЂ” HE

20 не вырабатывается запрещающий потенциал, что позволяет импульсу обращения закончиться и произвести запуск одного из блоков памяти 23.

По окончании импульса обращения в рассматриваемом случае запрещающий потенциал появляется на выходе элемента И вЂ” НЕ

20.

Чтобы отключение питания адресных и разрядных цепей блоков 23 не произошло раньше окончания внутреннего цикла работы блока памяти, предусмотрена задержка отключения питания. Для этой цели применен счетчик

16. Разрешением на начало работы счетчика

16 является потенциал с выхода триггера 19.

При переполнении счетчика 16 на его выходе появляется импульс, запирающий ключ 2, в результате чего шины литания адресных и разрядных цепей блоков 23 отключаются.

Кроме того, сигнал с выхода временного селектора 14 поступает через элемент задержки

6 на ключ 1 и отключает выпрямители 3 и

4 от сети, что приводит к отключению цепей питания логических элементов (на чертеже не показаны).

Тем самым обеспечивается номинальное значение напряжения питания адресных и разрядных цепей при перезаписи последнего числа в момент отключения первичной сети или источника питания логических элементов, что, в итоге, приводит к повышению функциональной надежности устройства.

Применение описанного устройства, например в комплексе для отладки программ, позволяет значительно сократить непроизводительные

736178 затрпы времени на восстановление информации путем повторного ввода программ после каждого сбоя по цепям питания.

Формула изобретения

Устройство для сохранения информации в памяти при отключении питания, содержащее источник питания, входы которых соедине- <и ны с выходом первого ключа, вход которого соединен со входом устройства, фильтр, вход которого подключен к выходу первого источника питания, а выход — ко входам источников опорного напряжения, второй ключ, вход TopoIo соединен с выходом второго источника питания, а выход — с одним из выходов устройства, блоки сравнения, одни входы которых подключены к выходам источников опорного напряжения, другие входы со- >О ответственно — к выходам источников питания и входу устройства, а выходы блоков сравнения соединены со входами элемента ИЛИ, временной селектор, вход которого подключен к выходу элемента ИЛИ, один выход через элемент задержки к управляющему входу первого ключа, другой выход — к ерному входу генератора одиночных импульсов, Второн вход которого соединен с выходом источника TBKToBblx импульсов, и управляющие шины, о т л и ч а ю щ е е с.я тем, что, с целью повышения надежности устройства, оно содерх ит элементы И, элемент ИЛИ—

HF., элемент И вЂ” НЕ. триггер и счетчик, выход которого соединен с управляющим входом второго ключа, один из входов — с выходом источника тактовых импульсов, другой вход — с первым входом элемента И вЂ” НЕ и выходом триггера, вход которого подключен к выходу генератора одиночных импульсов, одни входы элементов И соединены с управляющими шинами, другие — с выходом элемента И вЂ” НЕ, а выходы — с другими выходами устройства и входами элемента ИЛИ вЂ” НЕ, выход которого подключен ко второму входу элемента И вЂ” НЕ.

Источники информации, принятые во внимание при экспертизе

1. Патент США N 3624б17, кл. 340 — 17"5, 1971.

2. Авторское свидетельство СССР И 331424, М. кл. 6 11 С 27/00, 1970 (прототип).