Устройство для синхронизации однотактных дискретных устройств

Иллюстрации

Показать всеРеферат

Q л и с- : сан

И ЗОБ РЕТЕ Н

Союз Советских

Социалистических

Реслублик

К АВТОРСКОМУ СВИДЕТЕЛЬС (6I ) Донолннтельное к авт. свнд-ву = (22) Заявлено 01.06,76 (21) 236 5894/

}М. Кл.

Н 03 К 5/13 с присоединением заявки И

Государственный комнтет (23) Приоритет йо делам нэооретеннй н открытий

Опубликовано 25.0,60, Бюллетен

) УДК 621 .3 1 7.799 (oee.a) Дата опубликования описания (72) Авторы изобретения

К). В. Пресняков и П. С, Супьменев (7!) Заявитель (54) УСТРОЙСТВО jlJIH СИНХРОНИЗАЦИИ ОДНОТАКТНЫХ

ДИСК РЕТНЫХ УСТ PGACTP

Изобретение относится к импульсной технике и может быть испопьэовано в синхронных устройствах обработки дискретной информапии.

Известные устройства дпя синхронизации однотактных дискретных устройств имеют существенные недостатки, закпю чающиеся в необходимости выпопнения опредепенных соотношений между вепичинами задержек сигналов синхронизации и

IO задержек переключения элементов памяти и комбинационных логических схем $1).

Так как задержки эпементов, на которых реапизуются устройства обработки дискретной информации, контропируются

1S только сверху, то-есть гарантируется непревышение задержками некоторых максимапьных значений, то дпя обеспечения устойчивого обмена информацией между элементами памяти необходимо введение контроля временных параметров элементов по минимуму, что приводит к уменьшению процента выхода годных элементов и к увеличению их стоимости.

Наиболее бпизким к изобретению по технической сущности явпяется устройство, преобразования входного сигнала дпя синхронизация однотактных дискретных устройств, содержащее последовательно соединентые усилители мощности схемы размножения тактовых импульсов и разбитые на группы эпементы памяти (2> . Обеспечение устойчивого функционирования однотактных устройств осуществляется за счет того, что выход первого усилителя мощности схемы размножения тактовых импульсов подключается к синхрониэирующим входам поспедней группы эпементов памяти, выход второго усилителя мощHccTH — K синхроттиэирующим BxogQM предпоследней группы эпементов памяти и т.д., а выход поспеднего усилитепя мощности — к синхронттэирующим входам первой группы элементов памяти.

Недостатком известного устройства является невозможность осуществления связей между поспедутощими и предыдущими группами эпементов памяти, так как при этом не обсспечивается условие передачи информации без искажений. Кро. ме того, при последовательном соединении усилителей мощности увеличивается задержка сигналов синхронизации, что приводит к снижению быстродействия устрой ства обработки дискрстной информации.

Цель изобретения — повышение надежттости работы дискретных устройств и увеличение их быстродействия.

Это достигает за счет того, что в устройство для синхронизации однотакл ных дискретных устройств, содержащее

15 разбитые на группы элементы памяти, между группами элементов памяти введены инверторы и дополнительные одноступенчатые элементы памяти, входы которых соединены с выходами элементов

20 памяти предыдуших групп„а выходы— со входами элементов памяти последующих групп, причем сцнхронизируюшие входы дополнительных одноступенчатых эле ментов памяти подключены через инвер25 торы к шинам тактовых частот тех групп элементов памяти, на входах которых они установлены.

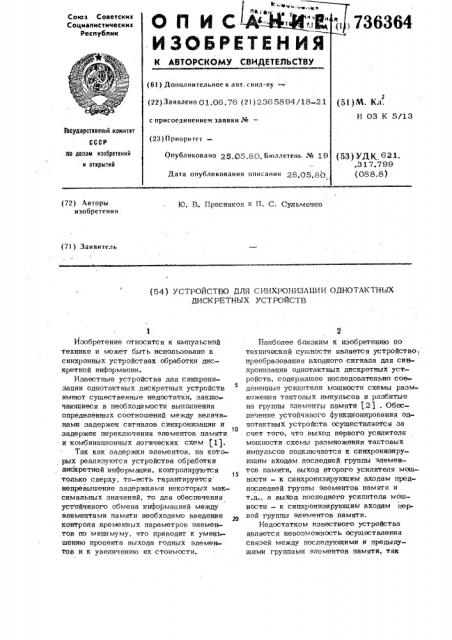

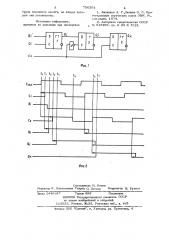

На фиг. 1 дана схема предлагаемого < устройства; на фиг. 2 — графически представлена временная диаграмма, поясня>ошая работу устройства.

Оно содержит передающий элемент 1.

35 памяти, принадлежащий t. -ой труппе элементов памяти, принимающий элемент памяти 2, принадлежащий 5 -ой группе элементов памяти, дополнительный эле-, мент памяти 3 и инвертор 4.

4О

Из-за разли тных задержек импульсов исходной тактовой частоты Гиск схемой размножения тактовые импульсы С; и С к могут иметь несовпадение во вре45 менп фронтов импульсов, вследствие чего при непосредственном соединении элеме|ттов памяти может произойти ложный перенос информации с элемента 1 памяти на элемент 2 памяти. При вк почении между элемента Вт памяти 1- -ой и К -ой групп дополнительного элемента памяти, запись информации в который производится уровнем напряжения противоположным уровню, осуществляющему запись информации в элементы памяти К-ой группы, 55 информация, появившаяся;на выходе элемента 1 памяти с -ой группы в момент времени t>, не может записаться в дополнительный элемент памяти, так как ! в это время па его синхронизирующем входе цаходится потенциал, запрещающий запись, 1(ри появлении положительного фронта импульса тактовой частоты С к в момент времени t 5 начинается запись информации в дополнительный элемент памяти и одновременная блокировка -,ÿïècè информации в элементы памяти К -ой группы. "àèèñü информации в элементы памяти К -ойгруппы начнется в мбментвремени t5, а изменение информации на выходах элементов памяти К -ой группы— в момент времени t <, то-есть инфор-. мация на выходах элементов памяти

-ой группы появится по отношению к информации на выходах элементов памяти ь -ой группы с задер>ккой, равной периоду синхронизируюшей частоты, что соответствует правильной передаче информации без искажений.

Гледовательно, включение дополнительных элементов памяти между группами элементов памяти, синхронизируемых от различных усилителей мощности, позволяет обеспечить устойчивое функционирование однотактных устройств обработки дискретной информации, то-есть повысить надежность работы дискретных устройств прп любом порядке подключения усилителей мощности к синхронизируюшим входам элементов памяти, и получить максимально возможное быстродействие этих устройств за счет уменьшения задер>кки, вносимой схемой размножения тактовых импульсов. формула изобретения

Устройство для сицхронизации однотактных дискретных устройств, содержащее разбитые на группы элементы памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности функционирования и повышения быстродействия, между группами элементов памяти введены инверторы и дополнительные одноступенчатые элементы памяти, входы которых соединены с выходами элементы памяти предыдущих групп, а выходысо входами элементов памяти последующих групп, причем синхронизирующие входы дополнительных одноступенчатых элементов памяти подключены через инверторы к шинам тактовых частот тех групп алементов памяти, на входах которых они установлены. с

<о4 4 4

Gucx

Сх

Составитель И. Ильин

Редактор К. Катаманина Техред O. де, еза Корректор B. Бутяга

Заказ 2446/47 Тираж 995 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Источники информации, принятые во внимание при експертизе

7ММ4 6

1. Филипков А. Г.,Белкин О. С. Про ктирование логических узлов ЭВМ. М., (ов.радио, 1974.

2. Авторское. свидетельство СССР

N. 515266, кл. Н 03 К 5/13.