Устройство для интегрирования в системе остаточных классов

Иллюстрации

Показать всеРеферат

„„737961

О П Е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

РеспубликК АВТОРСКОМУ СВИ ЕТИЛЬСТВУ (61) Дополнительное к авт. саид-ву — (22) Звявлено 010378 (21) 2583517/18-24 (51)М. Кл.2 с присоединеиЫем заявки ¹ 2584 294/18-24

G 06 G 7/18

Государственный комитет. СССР по дедам изобретений и открытий (23) Приоритет

Опубликовано 300580.Бюллетень ¹ 20

{53) УДК б 81 . 3 35 (088.8) Дата опубликования описания 300580 (72) Авторы изобретения

М,В.Синьков и В.Н.Груц

Институт электродинамики AH Украинской ССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ

В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ

Изобретение относится к аналоговой .вычислительной Технике и может быть .использовано для. интегрирования пеРеменных, представленных по любому, заранее выбранному, модулю сисъ темы остаточных классов (СОК).

Известно устройство для интегрирования решаемых переменных при .представлении их в СОК, состоящее

:из интегрирующего усилителя, схем сравнения, транзисторного ключа, триггера и счетчиков опорного и ком» пенсационного напряжения (1J

В этом устройстве уменьшена погрешность, связанная с задержкой, вносимой разрядом конденсатора обратной связи, ®цнако погрешность, связаннаи с задержкой на включение цепи разряда- конденсатора обратной связи, не уменьшена..Кроме того, это устрой- ство громоздко и не позволяет работать с входными сигналами обоих знаков. . Известно также устройство для ,интегрирования в СОК, состоящее иэ интегрирующего усилителя, тринистора и источйика опорного напряжения (23.

В этом устройстве не приняты специальные меры для исключения задержки на включение цепи разряда конденсатора обратной связи. Устройство также не позволяет работать с входными сигналами обоих знаков.

Наиболее;близким по технической сущности является устройство для интегрирования в системе остаточных. классов, содержащее интегрирующий усилитель, выход которого через последовательно соединенные токоограничивающий резистор и электронный ключ соединен с суммирующим входом -интегрирующего усилтттеля, и схемй cðàâнения, первые входы которых подключены к выходу интегрирующего усилителя, а вторые входы схем сравнения соединены соответственно с разноименными полюсами источников напряжения 13)..

Это устройство позволяет работать с входными сигналами обоих знаков.

Однако ойо обладает низкой точ,ностью из-за большой задержки на

-включение цепи разряда конденсатора обратной связи. В эту задержку вхо.дят время срабатывания одной из

737961 ;exeM сравнений и время включения эЛеКтромагнитного реле. Кроме того, данное устройство обладает низкой надежностью из-за присутствия электромеханических контактов.

Цель изобретения — повышение точности интегрирования.

Поставленная цель достигается тем, что в устройство введены диф- . ференциатор. и элемент ИЛИ, входы которого подключены к выходам схем сравнения, выход элемента ИЛИ под- ключен к управляющему входу электронного ключа, а дифференциатор включен между выходом интегрирующе"го усилителя и другими полюсами источников напряжения.

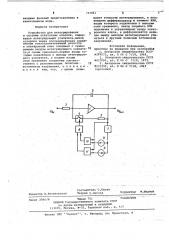

Йа чертеже представлена функциональная схема устройства для инте- . грирования B системе остаточных классов.

Устройство для интегрирования в СОК содержит интегрирующий усилитель 1 с конденсатором 2 в цепи обратной связи и резистором 3 на входе, электронный ключ 4, токоограни- 75 чивающий резистор 5, элемент 6 ИЛИ, дифференциатор 7, источники 8 и 9 напряжения, задающие выбранный модуль СОК, схемы 10 и 11 сравненйя.

Вход дифференциатора 7 соединен с выходом интегрирующего усилителя

1, а Выход - с разноименными полю- сами обоих источников 8 и 9 напряжения, вторые полюса которых соеди- нены с входами схем 10 и 11 сравнения, выходы схем 10 и ll сравнения подключены ко входам элемента 6 ИЛИ, соединенного своим выходом с управляющим входом электронного ключа 4, нормально разомкнутые контакты кото-, рого включены последовательно с токо- 40 ограничивающим резистором 5 в обратную связь интегрирующего усилителя 1, Устройство для интегрирования в СОК работает следующим образом.

В начальном положении, когда напряжение на входе Ug равно нулю, напряжения на выходе интегрирующего усилителя 1 и дифференциатора 7 также равны нулю, на выходах схем

10, 11 сравнения и элемента б ИЛИ также информационный. нуль.

Следовательно, электронный ключ 4 разомкнут.

В Этом положении, если необходимо, осуществляется ввод начальных значений на конденсатор 2 (цепи ввода начальных значений, а также цепи пуска и останова условно не показаны).

При подаче входного напряжения

Оь„ вначале интегрирование осуществляется обычным путем. Любая из схем 6О сравнения срабатывает только тогда (выдает на выход информационную . единицу), когда напряжения на ее входах сравняются и по знаку и по амппитуде.

Схема 10 сравнения определяет момент сравнения положительных напряжений, т.е., когда

dU вь

Ьь1к Р! 1 Д

m ) р1; выбранный модуль СОК; масштаб по р1; коэффициент передачи дифференциатора. где Upi =. р1

mð К

Схема 11 сравнения срабатывает при сравнении отрицательных напряжений.

Величины т Uр; задаются при помощи источников 8 и 9 напряжений.

Задержка на включение цепи разряда конденсатора обратной связи равна сумме времени срабатывания одной из схем 10 или 11 сравнения, времени передачи информации через элемент

6 ИЛИ и времени срабатывания элект- ронного ключа 4. Эту задержку можно считать величиной постоянной и рав-. ной t . Если коэффициент передачи цифференциатора 7 к равен времени

Задержки t>,то момент начала срабатывания любой из схем 10 или 11 сравнения автоматически упреждается точно на величину задержки tg (при условии, что входное напряжение U „представлено в квантованном виде) .

Если квант входного напряжения равен (— U>), тогда напряжение U> 1„ до момента срабатывания любой их схем 10 или 11 сравнения определяется по формуле

U = -K K Uj, . (4)

При сравнении формул (3) и (4), видно, что, если К„= t®, абсолютные значениял0 и Ug совпадают. Это оз- . начает, что в схеме автоматически происходит вычитание величины ь U нз Бр), обеспечивающее требуемый момент упреждения по времени на величину

Применение предлагаемого устройства позволяет повысить точность интегрйрования эа счет исключения задержки на включение цепи разряда конденсатора обратной связи для (2) где к — коэффициент передачи интегри- . рующего усилителя 1 .. При такой форме напряжения U рачало срабатывания любой из схем 10 или 11 сравнения упреждается точно на величину времени задержки t если амплитуда напряжения Б„„в момент начала срабатывания меньше напряжения

U; на величину. U = К U t (3)

С другой стороны, при подаче напряжени я (3 ) на вход ди фференци атора

7 напряжение на его.выходе равно

Ю 3796.1

Формула изобретения

Составитель С.Белан

Техред О.Легеза корректор и Шарохин

Редактор Л. Веселовская

Подписное

Тираж 751

ljHHHHH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д . /

4/5

Заказ 2566 /8

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 входных функций представленных в квантованном виде. устройство для интегрирования в системе остаточных классов, содержащее интегрирующий усилитель, выход которого через последовательно соединенные токоограничивающий резистор и электронный ключ соединен с суммирующим входом интегрирующего усилите- 10 ля,и схемы сравнения, первые входы которых подключены к выходу интегрирующего усилителя, а вторые входы схем сравнения соединены соответственно с разноименными полюсамиисточников напряжении, о т л и ч а ю— щ е е с я тем, что, с целью повышения точности интегрирования, в авво введены: дифференциатор и элемент ИШ, входы которого подключены Ы выходам схем сравнения, выход элемента ИЛИ ,! подключен к управляющему входу электронного ключа, а дифференциатор включен между выходом интегрирующего усилителя и другимй полюсами источникоЬ напряжения.

Ист очи и ки информации принятые во внимание при экспертйзф

1. Авторскбе свидетельство СССР

9249072 кл. G 06 G 7/18, 1968.

2. Авторское свидетельстно СССР

9437090, кл.. G 06 G 7/18, 1972.

3. Авторское свидетельство СССР.

М233299, кл. 6 06 6 7/18,-. 196.7 (прототип) .