Ячейка памяти для регистра

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свид-ву— пп 73799 «1

Союз Советских

Социалистических

Республик (51)М. Кл.2 (22) Заявлено 11,0178 (21) 2570190/18

G 11 С 19/00 с присоединением заявки ¹

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет—

Опубликовано 30,0580 Бюллетень № 20

Дата опубликования описания 300580 (53) УДК 681.327. .66 (088.8) (72) Авторы изобретения

Д.H. Дудин и В.И. Калинин (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ ДЛЯ РЕГИСТРА

Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах, Известен счетный триггер, содержащий прямой и инверсный однофазные тактируемые D-триггеры с перекрестным переключением их выходов ко входам, объединенные тактовые входы которых образуют счетный вход триггера (1).

Наиболее близким к предлагаемому по технической сущности является регистровое запоминающее устройство с последовательной записью, содержащее в качестве ячеек памяти регистры, соединенные через вентили записи, сигнальные триггеры по числу. регистров, линии задержки и вентили задержки (2) .

Каждое из рассматриваемых устройств можно использовать только для одной цели: либо только для счета, либо только для записн и хранения информации.

Недостатком известных устройств является низкая помехоустойчивость и силу выбранных схем построения, Цель изобретения — повышение помехоустойчивости ячейки памяти для регистра.

Поставленная цель достигается тем, что в ячейку памяти для регистра, содержащую основной D-триггер и элемент

И-НЕ, шину разрешения счета, шину записи, тактовые шины и шины установки 1 и 0, вв едены дополнительный D-триггер и элемент И-ИЛИ-НЕ; выход которого соединен с D-входом основного D-триггера, выход основно1О го D-триггера подсоединен к D-входу дополнительного D-триггера, выходы которого соединены с выходами разряда регистра и с первыми входами элемен там И-ИЛИ-НЕ соотв етственно, S-вход

t5 основного D-триггера и R-вход допол— нительного D-триггера подключены к

" шине установки 0, а S-вход дополнительного и R-вход основного

Р-триггеров соединены c шиной уста20 новки 1, С-входы основного и дополнительного D-триггеров соединены соответственно с тактовыми шинами, второй вход элемента И-ИЛИ-НЕ подключен к выходу элемента И-НЕ, один из

25 входов которого соединен с импульсным входом разряда регистра и третьим входом элемента И-ИЛИ-НЕ, другой вход элемента И-НЕ соединен с шиной разрешенйя счета и четвертым входбм элеЗО мента И-ИЛИ-НЕ, пятый вход которого

737991 подключен к шине записи, а шестой вход — к потенциальному входу разря да регистра.

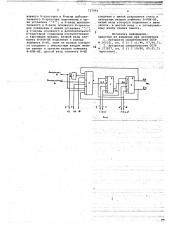

На фиг. 1 изображена функциональная схема ячейки памяти для регистра, а на фиг, 2 — временные диаграммы режимов работы.

Ячейка памяти для регистра содержит элемент 1 И-НЕ, элемент

2 И-ИЛИ-HE основной 3 и дополнительный 4 D-триггеры, шину 5 разрешения сМета, шину б записи, тактовые шины

7, 8 и шины 9,10 установки 1 и О™

Ячейка памяти для регистра работает с двумя синхронизирующими импульсными последовательностями С и Т (фиг. 2) . Такие последовательности применяют для синхронизации, например, в ЭВМ. В таких системах обработ(0 ка информации происходит по стробимпульсу, а выдача информации по так- 20 ту. Следовательно, все сигналы, приходящие на входы ячейки памяти синхронизированы (кратны) с Фактом.

Ячейка памяти в счетном режиме работает следующим образом. 25

С приходом первого импульса, счетной последовательности (время t на фиг. 2) и потенциала разрешения счета РС4 на входах элемента 2 И-ИЛИ-HE появляются три единицы. Следователь- 30 но, на выходе элемента 2 появляется

О, ТРИггер Подготовлен к перебросу и с приходом строб-импульса (время на фиг. 2) изменяет свое состояние (опрокидывается), подготовив к перебросу триггер 4, который опрокидывается с приходом тактового импульса

I (время Ф на фиг. 2), после чего элемент 2 еще не готов к работе. Логическая единица на соответствующие входы приходит с выхода триггера 4,,с выхода элемента 1 И-НЕ (на входе его логический 0 импульсной последовательности С„„ но время большее 1 ) и инверсия РР. Таким образом, на входе D-триггера 3 состояние не 4 йзйеняется до тех пор, пока не приходит второй счетный импульс С „(время t ) . С приходом этого импульса

" "снимается единица с соответствующего входа 2 элемента 2 И-ИЛИ-НЕ, а на вы- щ ходе этого элемента появляется.единица и подготавливает триггер 3 к пе.Ребросу. С приходом строб-импульса (время 4) триггер 3 перебрасывается и подготавливает к перебросу триггер

4, который, в свою очередь, перебрасывается с приходом очередного такта (время tq). Дальше цикл повторяется, I начиная со времени 5.

В режиме записи информации ячейки памяти работает следующим образом. 60

С йриходом импульса записи входной логической 1 (время t1), ко =" торую"нужно записать, готов к работе элемент И на соответствующих входах элемента И-ИЛИ-НЕ 2. Следовательно, 6$ на выходе элемента 2 (на входе

D-триггера 3) появляется логический 0, который подготавливает, а строб-импульс С (время tz) перебрасывает триггер 3 с логического 0 на логическую 1 . Триггер 3 изменяет свое состояние и подготавливает, 1 а такт Т„(время t. ) перебрасывает триггер 4, Таким образом, на его выходе Q записывается логическая 1 .

Это состояние может длиться сколь угодно долго.

Рассмотрим нозврат ячейки памяти в исходное состояние (время t ) или перезапись входной информации (логический 0 ) по. сигналу PP. Сигнал PP приходит во время (или в другое время), изменяя выходное состояние элемента 2 с логического 0 на логическую 1, что, н свою очередь, по строб-импульсу С„ вызывает переброс триггера 3 (время tq) и переброс по такту Tq триггера 4 (время tq), что равнозначно переходу разряда регистра и исходное состояние.

В ячейке памяти есть еще дне шины: шина установки 1 и шина установки 0, причем вход Установки 0 триггера 3 (вход R) соединен со входом Установка 1 триггера 4 (нход S), а вход Установка 1 триггера 3 (вход S) соединен со входом Установка 0 триггера 4 (нход R) . Такое соедине- . ние позволяет упростить схему ячейки памяти, так как иначе необходим еще один дополнительный иннертор между выходом триггера 3 и входом триггера 4. Исходное состояние триггера н этом случае обратное состоянию триггера 4. Кроме того, дополнительные входы Установка 0 и Установка 1 позволяют задавать различные начальные услония счета.

Предложенную ячейку памяти можно применять без изменения схемы для построения любых схем вычислительной техники, содержащих память.

Формула изобретения

Ячейка памяти для регистра, содержащая основной D-триггер и элемент

И-НЕ, шину разрешения счета, шину записи, тактовые шины и шины установки 1 и 0, о т л и ч а ю щ а я с я тем, что с целью повышения помехоустойчивости ячейки памяти для регистра, в нее введены дополнительный D-триггер и элемент И-ИЛИ-НЕ, выход которого соединен с D-входом основного D-триггера, выход основного D-триггера соединен с D-нходом дополнительного D триггера, выходы которого соединены с выходами ячейки памяти и с первыми входами элемента

И-ИЛИ-НЕ соответственно, S-вход ос1

737991

Йнлцлесии й

Оолим и иапо

Т Мкю,g

C йю!

РП ФЯ Ю

Фив 1 новного D-триггера и R-вход дойолнительного.D-триггера подключены к шине установки 0, а S-вход дополнительного и R-вход основного D-триггеров соединены с шиной установки 1, а С-входы основного и дополнительного

D-триггеров соединены соответственно .с тактовыми шинами, второй вход элемента И-ИЛИ-HE подключен к выходу элемента И-НЕ, один из входов которо го соединен с импульсным входом ячейки памяти и третьим входом элемента

И-ИЛИ-НЕ, другой вход элемента И-НЕ соединен с шиной разрешения счета и четвертым входом элемента И-ИЛИ-НЕ, пятый вход которого подключен к шине записи, а шестой вход — к потенциальному входу ячейки памяти.

5 °

Источники йнформации, принятые во внимание при экспертизе

1. Авторское свйдетедьствО СССР

9 362351, кл. G 11 С 11/40, 07.04.71.

2. Авторское свйдетельство СССР

М 377877, кл. G 11 С 19/00, 05.01.71 (прототип) .

° 737991

Заказ 2 571/9

Тираж бб2 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 а

Составитель А. Воронин

Редактор Л..Веселовская Техред A.степанская Корректор B. Синицкая