Устройство для управления тиристорным преобразователем

Иллюстрации

Показать всеРеферат

,ЭЗВО95

Союз Советскна

Соцналнстнческнк

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к авт. свил-ву— (22) Заявлено 09.06.77 (2I ) 2493882/24-07 с присоединением заявки,% (23) Приоритет

Опубликовано 30.05.80. Бюллетень М 20

Дата опубликования описания 30.05,80 (51) М. Кл.

Н 02 P 13/16

Государственный комитет (53) УДK 621. ,316.7 27 (088. 8) по делам изобретений и открытий

А. В. Черкашин, А. И. Тарасенко и Ф. И. Пискун (72) Авторы изобретения (7I) Заявитель

Украинский заочный политехнический институт (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТИРИСТОРНЫМ

- HPÅ0ÁРАЗОВАТЕЛ ЕМ

Устройство относится к области алектротехники и может быть использовано при построении систем управления тиристорными преобразователями.

Известны устройства для управления

5 тиристорными преобразователями содержащие двухтактный ключевой каскад, работающий в автоколебательном режиме, трансформатор, токоограничиваюшие резисторы в цепях баз транзисторов двух1О тактного ключевого каскада, дополнительный транзистор, резистор, ограничивающий ток коллектора дополнительного транзистора, резистор смешения дополHHTBB b HOW TpGHBHCTOp 8 К не достаткам 1 5 устройства относится низкий коэффициент полезного действия, за счет наличия бросков тока при переключении транзисторов .двухтактного ключевого каскада, а также из-за потерь в дополнительном транзисторе.

Известно также устройство для унравлееии тарилтлрами (2j,аолериатее е своем составе двухтактный ключевой каоf

2 кад, работающий в автоколебательном режиме, выходной трансформатор, являющийся нагрузкой двухтактного ключевого каскада, управляющий транзистор, амиттер которого соединен с источником смещения, резистор, ограничивающий ток управляющего транзистора, диоды, соединяющие базы транзисторов двухтактного ключевого каскада с коллектором управляющего транзистора через базовые обмотки выходного трансформатора, и ограничивающие резисторы, включенные в базовые пепи транзисторов двухтактного ключевого каскада.

К недостаткам устройства относится низкий КПД тяжелый режим работы управляющего транзистора, сложная схема иэ-эа наличия источника смешения.

Наиболее близким по технической сущности к изобретению является устройство для управления тиристарным преобразователем $3), содержащее задающий генератор, распределитель импульсов по каналам, выходной двухтактный ключевой

3 73 каскад, дополнительный транзистор, подключенный через резистор параллельно

- йереходу коллектор-эмиттер одного из транзисторов двухтактного ключевого кас када и отпираемого в паузах между управляюшими импульсами, Я -цепочку, осуществляющую включение определенного транзистора двухтактного ключевого кас-. када при поступлении управляющего импульса, ограничиваюшие резисторы, включенные в базовые цепи транзисторов ttayxтактного ключевого каскада, Извертное устройство имеет тот недостаток, что наличие дополнительного транзистора, подключенного параллельно переходу коллектор -эмиттер одного из транзисторов двухтактного ключевого каскада к отпираемого в паузах между управляюшими импульсами, значительно снижает помехоустойчивость всего устройства, Белью изобретения является повышение помехоустойчивости устройств для управления тиристорными преобразователями.

Поставленная цель достигается тем, что устройство для управления тиристорным преобразователем, содержащее задаюший генератор, распределитель импульсов по каналам и выходной двухтактный каскад на ключах переднего и заднего фронта имйульсов управления в каждом канале дополнительно снабжено в кажт дом канале модуляторами управляющих импульсов ключей переднего к заднего фрбнта выходного каскада, узлом очеред» ности работы модуляторов, выполненным на инверторе,RS -триггере ячейки запрета и логической схеме ИЛИ, и узлом состояния ключей выходного каскада, выполненным на ЙЗ -триггере ячейки памятк, логической схеме И и одновибраторе, причем выход задающего генератора подключей к одному иэ входов обо- их модуляторов каждого канала,к другом у входу одного иэкоторых неПОсредственно, а второго через узел очере дности подключен выход данного канала распр еделителя импульЖв, -при этом выходы модуляторов подключены к управляющим входам ключей выходного каскада и входам A S òðèòrepa ячейки памяти, выход которого подФйбчен к одному из входов схемы И, к другом входу которой подключен выход входного инвертора узла очередности, а выход схемы И через одновибратор включен на один из входов выходной схемы

ИЛИ узла очередности, к другому входу

=-"М ф = :а.-:,ж ., .:8095 4 которой подключен выход -триггера ячейки запрета, на входы которого подключен выход инвертора и модулятора ключа переднего фронта.

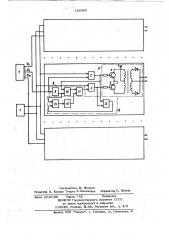

На чертеже представлена принципиаль5 ная схема устройства, Устройство содержит задаюший генератор 1, выходы которого подключены к одному из входов модуляторов 2 и 3 управляюших импульсов ключей переднего

4 и заднего 5 фронта выходного двухтактного каскада 6, Выход данного канала распределителя 7 управляющих импульсов по каналам подключен на вто15 рой вход модулятора 2 ключа переднего фронта 4 и ко входу узла очередности .

8 работы модуляторов, выход которого подключен на второй вход модулятора 3 ключа заднего фронта 5. Узел очередщ ности 8 состоит из входного инвертора 9 выход которого подключен к одному из входов Pg -триггера ячейки запрета 10. на второй вход которого подается сигнал с выхода модулятора 2. ВыходЖ-триг25 гера ячейки запрета 10 подключен к одному из входов выходной логической схемы ИЛИ 11, к другому входу которой подключен выход узла состояния 12 ключей выходного двухтактного каскада 6, ЗО состояшего кэйл -триггера ячейки памяти

13, на входы которого подаются сигналы с модуляторов 2 и 3, логической схемы И 14, один из входов KQTopoA связан с выходом RS -триггера ячейки па35 мяти 13, а другой — с выходом инвертора 9 узла очередности 8, и выходного одновибратора 15, включенного на выход схемы И 14.

Устройство работает следуюшим об40 разом.

Как толко на -ом выходе распределителя управляюших импульсов 7 появится управляющий импульс, он поступит на один из входов модулятора управ;

45 ляюших импульсов 2 ключа переднего фронта 4 и откроет его. Одновременно с запрешаюшего входами -триггера ячейки запрета 10 узла очередности 8 снимается запрешаюший единичный сигнал.

Первый заполняющий импульс, который появится на выходе модулятора ynpaamnoших импульсов 2 иключит транзисторный ключ 4 переднего фронта двухтактного ключевого каскада 6 и поступит на разре55 шаюший вход А -триггера ячейки запрета 10, пер@вбдя его в единичное состояние. Едивичный сигнал с выхода ячейки

10, пройдя через схему ИЛИ 11, отроет

738095

Источники информайни, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 440759, кл. Н 02 Р 13/16, 1974.

2. Авторское свидетельство СССР

K 474083, кл. Н 02 М 1/08, 1975.

3. Авторское свидетельство СССР

¹ 464949, кл. Н 02 P 13/16, 1975. модулятор управляющих импульсов 3 ключа заднего фронта 5 для прохождения заполняющих импульсов. Таким образом, оба модулятора управляющих импульсов оказываются открытыми и обеспечивают нормальную работу двухтактного ключевого каскада

6, причем первым всегда включается транзистор переднего фронта импульса управления.

После окончание управляющего импуль-, са оба модулятора закрываются, а на вход схемы И 14 с выхода инвертора 9 подается единичный сигнал. Если последним открывался транзисторый ключ 5 йвухтактного ключевого каскада 6, т.е, 1S последний заполняющий импульс прошел через модулятор управляющих импульсов, 3, то в этом случае Р -триггер ячейки памяти 13 узла состояния .12 ключей выходного двухтактного каскада 6 примет нулевое состояние и одновибратор 15 не получит разрешения на запуск, Если же последним открывался, транзистор 4 двухтактного ключевого каскада

6, то RG -триггер ячейки памяти 13 примет единичное состояние.

В этом случае на входе одновибратора 15 появится сигнал запуска, и на выходе сформируется импульс, длительность которого не больше длительности 30 .заполняющего импульса, но достаточная для надежного открывания транзистора 5 йвухтактного ключевого каскада 6, Этот импульс, пройдя через схему

ИЛИ 11, откроет мбдулятор 3 управляю- 35 щих импульсов ключа зайнего фронта 5 и пропустит на его выход заполняющий импульс, Транзистор 5 двухтактного ключевого каскада 6 откроется и переведет трансформатор выходного каскада 6 в 46 исходное состояние. Одновременно — триггер ячейки памяти 13 выдаст на своем выходе нулевой сигнал и закроет схему И 14 запуска одновибратора 15.

По окончании импульса на выходе одно45 вибратора 15 модулятор управляющих импульсов 3 ключа заднего фронта 5 закроется, и схема примет исходное состояние.

Таким образом, при поступлении управляющего импульса в каждом канале первым включается .транзистор 4 йвухтактного ключевого каскада 6, а при окончании управляющего импульса iroc-. ледним открывается транзистор 5. Поэ55 тому состояние выходного трансформатора двухтактного каскада 6 перед поступлением очередного управляющего импульса является определенным, и первый заполняющий импульс, поступающий на управляющий переход тиристора будет иметь такую же амплитуду и длительность, как и все последующие, что обеспечит четкое включение силового тиристора тнристофного преобразователя и высокую помехоустойчивость системы управле ния. формула изобретения

Устройство для управления тнристорным преобразователем, сбдержащее задающий генератор, распределитель импульсов, по каналам и выходной двухтактный каскад на ключах переднего и заднего фронта импульсов управления в каждом кана- ле,отличающе еся тем, что, с целью повышения помехоустойчивости, оно снабжено в каждом канале модуляторами управляющих импульсов ключей переднего и заднего фронта выходного каскада, узлом очередности работы модуляторов, выполненным íà инвертореКЭтриггере ячейки запрета и логической схеме ИЛИ, и узлом состояния ключей выходного каскада, выполненным BBRS триггере ячейки памяти, логической схеме И и одновибраторе, причем выход задающегб генератора подключен к одному йз входов обоих модуляторов каждого канала, к другому входу одного иэ которых непосредственно, а второго через узел очередности подключен выход данного канала распределителя импульсов, при этом выходы модуляторов подключены к управляющим входам ключей выходного каскада и входами -триггера ячейки памяти, вь ход которого подключен к одному из вхо; дов схемы И, к другому входу которой подключен выход входного инвертора узла очередности, а выход схемы И через одновябратор включен на один из входов выходной схемы ИЛИ узла очередности, r. другому входу которой подключен выход

RS -триггера ячейки запрета, на входы которого подключен выход инвертора и модулятора ключа переднего фронта.

738095

Составитель В, Жмуров

Редактор Н, Коляда Техред А Шеланская Корректор С, Шомак

Заказ 2826/35 Тираж 783 Подписное

lIHHHflM Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4