Цифровой импульсный фазовый дискриминатор

Иллюстрации

Показать всеРеферат

Й С

Ссноз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 10 0 4 73 (2 1) 19 1 3 б 22/ 18-2 1 (51)М. Кл.

Н 03 К Ь/18 с присоединением заявки М (23) Приоритет

Государственный комитет

СССР йо делам изобретений н открытий

Опубликовано 30.05.80, Бюллетень Мо 20 (53) УДК 621. 314. 3 (088 ° 8) Дата опубликования описания 30,05,80 (72) Авторы изобретения

О.С.Голод, И.-Б,И.Кампо, Ш.И,Исаев и Г,Г.Олехнович (71) Заявитель

Севеоо-Западный заочный политехнический институт (54) ЦИФРОВОЙ ИМПУЛЬСНЫЙ ФАЗОВЫЙ ДИСКРИМИНАТОР

Изобретение относится к импульс- группе, соединен с Вторыми выходами ной технике. триггеров (2) .

Известен цифровой импульсно-фазо- ....Данный дискриминатор не обеспечивый дискриминатор, содержащий два вает необходимого фазового диапазона. канала, каждый из которых содержит Целью изобретения является расщисчетчик импульсов, триггер, трехвхо- рение фазового диапазона дискримина-довый логический элемент И, блок ин- ции. дикации и логическую схему (1), Это достигается тем, что в фазовый такой дискриминатор имеет малый 1О дискриминатор, содержащий триггерный диапазон. фазовый дискриминатор, состоящий из

Наиболее близким по технической триггеров, объединенных в две группы, сущности к предлагаемому является первые выходы которых подключены к цифровой импульсно-фазовый дискри- входам цифро-аналогового преобразова.МННаТор, содержащий триггерный фазо- теля,логические элементы И,ббъединенвый дискриминатор, состоящий из ные в четыре блока по числу триггеров триггеров, объединенных в две группы, в триггерном фазовом дискриминаторе первые выходы которых подключены к каждая, причем выходы логических элевходам цифро-аналогового преобразова- ментов И подключены к входам соответтеля, логические элементы И, объеди- ствующих триггеров, первые входы всех ненные в четыре блока по числу триг- логических элементов И, кроме одного геров В триггерном фазовом дискон- .в каждсм блоке, первых двух блоков минаторе каждая, причем выходы логи- соединены c первыми выходами триггеческих элементов И подключены к вхо- ров, первые входы логических элемендам соответствующих триггеров riep- тов И третьей и четвертой групп, кро25 вые входы всех логических элементов ме первого в каждой группе, соединены

И, кроме одного в каждом блоке, пер- с-вторйми выходами триггеров, введевых двух блоков соединен с первыми ны логический элемент антисовпадения, .выходами триггеров, первые входы ло- два логических элемента ИЛИ и два гических элементов И третьей и чет- ----логических элемента HE„ причем входы вертой групп, кроме первого в каждой Зо логического элемейта антисовпадения --738135 соединены с входными шинами, один вь ход логического элемента антисовпаде. -ния соединен с вторыми входами логических элементов И первого и четвертого блоков,а второй выход логического элемента антисовпадения соединен с вторыми входами логических элементов

И .Второго и третьего блоков, входы каждого из логических элементов ИЛИ соединены с вторыми выходами триггеров соответствующей группы, а выходы каждого логического элемента

ИЛИ через логический элемент НЕ подключены перекрестно к первым входам первых логических элементов И третьего и четвертого блокон.

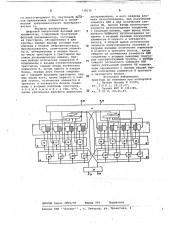

На чертеже приведена структурная электрическая схема предлагаемого фазового дискриминатора.

ЦиФровой импульсный фазовый дискриминатор содержит фа3оный триггерный дискриминатор из двух групп 1,2, cocToRlljHx соответственно из триггеров 3-10, цифроаналоговый преобразователь 11, блоки 12-15 логических элементов И 16-31, логический элемент антисонпадения 32, логические элементы ИЛИ 33, 34, логические элементы НЕ 35, 36, Входной сигнал подан на входные шины 37, 38. Выходной сигнал снимается с выходов 39, 40.

Дискриминатор работает следующим образом.

При нулевом положении всех триггеров 3-10 в группах 1, 2 триггерного фазового дискриминатора потенциалы на выходе цифроаналогового преобразователя 11 также равны нулю и ток в нагрузке дискриминатора отсутствует; таким образом, исходная точка выходной характеристики устройства проходит через начало координат. Поступающие на входы логического элемента антисовпадения 32 импульсы подвергаются фазоной селекции, в результате которой совпадающие по фазе импульсы не проходят на вторые входы блоков 12-15 логических элементов И и состояние схемы .не изменяется.

Запись информации в группы 1, 2, триггеров триггерного фазового дискриминатора осуществляется импульсами с блоков 14, 15 элементов И последовательно, начиная с первого триггера в каждой группе (1 или 2), которому соответствует первый логический элемент И блоков 14, 15, первым входом соединенный с выходом со ответствующего логического элемента НЕ 35, 36 ° После записи логической 1 в любую из групп 1, 2 триггеров запись в другую группу триггеров блокируется сигналом логического 0 с выходов логических элементов HE группы 1 или 2, в которую осуществлена запись, логической 1

Запись 1 в другую группу тригге os становится возможной лишь после воэнращения всех триггерон группы в нулевое положение, что осущестнляется импульсами с блоков 12, 13 логических элементов И.

Таким образом, работа триггер)ов групп 1, 2 происходит последовательно н соответствии со знаком фазового рассогласования. Также последовательно происходит запись 1 и внутри групп 1, 2 триггеров.

Последовательная установка триггеров групп 1, 2 в положение логической 1 приводит к линейному изменению тока в нагрузке (не показана) цифроаналогового преобразователя 11 до тех пор, пока все триг1з геры соответствующей группы не окажутся н положении 1 . Дальнейшее поступление импульсов на тот же вход устройства изменить состояния схемы не может,и выходная характеристика

33 дискриминатора с этого момента имеет нид типа ограничение . Так как периоду следования импульсов соотнетстнует 2 .радиан, то линейный фазовый диапазон дискриминации предлагаемого р5 дискриминатора составляет +2%и радиан (п — число импульсов заполнения групп триггеров фазового дискриминатора), При поочередном поступлении импульсов на входные шины триггеры групп 1, 2 будут поочередно, начиная с первых, работать н режиме установка 1 — устанонка 0 .

При этом через нагрузку цифроаналогогоного преобразователя 11 будут протекать импульсы тока, ширина которых пропорциональна фазовому рассогласованию, а с учетом постоянства нх амплитуды среднее значение процесса также будет пропорционально фазоному

40 рассогласонанию. Если разность фаз между импульсами на входах дискриминатора становится больше 2 )t радиан, т.е. периода следования, то соответствующий триггер группы 1 или 2 (в зависимости от знака фазового рассогласования) остается в положении логической 1, а последующий начинает работать, выделяя фазоное рассогласование за вычетом 2 л радиан.

Предыдущий триггер при этом является по существу элементом памяти, к содержимому которого добавляется среднее значение широтно-модулированного импульса последующего триггера. Таким образом, к концу линейного участка

55 -характеристики элемейтарного триггер .но-фазового дискриминатора, представляющего собой триггер группы 1 или 2, примыкает начальный участок характеристики последующего элементарного

g) триггерного фазового дискриминатора и т.д.

В целом устройство работоспособно в широком диапазоне частот. Разрешающая способность его определяется у чувствительностью логического элемен.

/38135

ЦНИИПИ Эаказ 2829/37 Тираж 995 Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 та антнсовпадения 32, крутизной фрон,тов применяемых элементов и линейностью цифроаналогового преобразователя 11.

Формула изобретения

Цифровой импульсный фазовый дискриминатор, содержащий триггерный фазовый дискриминатор, состоящий из триггеров, объединенных в две группы; первые выходы которых подключены к входам цифроаналогового ) д преобразователя, логические элементы И, объединенные в четыре блока по числу триггеров в триггерном фазовом дискриминаторе каждая, причем выходы логических элементов. И подключены к входам соответствующих триггеров, первые входы логических элементов И, кроме одного в каждом . блоке, первых двух блоков соединенМ с первыми выходами триггеров, первые входы всех, кроме первого в каждой группе, логических элементов И третьего и четвертого блоков соединены с вторыми выходами триггеров, отличающийс ятем,что,с целью увеличения фазового диапазона дискриминации, в него введены элемент антисовпадения, два логических элемента ИЛИ и два логнческих элемена НЕ, причем входы логического элемента антисовпадения соединены с входными иннами, один выход логи ческого эйемейта -антйсовпадения соединен с вторыми входами логических элементов И первого и четвертогО блоков, а второй выход логического элемента антисовпадения соединен с вторыми входами логических элементов

И второго и третьего блоков,, входы каждого из логических элементов ИЛИ соединены с вторыми выходами триггеров соответствующей группы, а выходы каждого логического элемента ИЛИ через логический элемент НЕ подключены перекрестно K первым йходам пер" вых логических элементов И третьего и четвертого блоков.

Источники информации, принятые во внимание при экспертизе 1. Патент Японии Р 33309, кл. 110 Н 2, 28.12 ° 67.

2. Патент ФРГ Р 1301365, кл. Н 03 К, 08.05.67,