Устройство преобразования дискретных сигналов

Иллюстрации

Показать всеРеферат

«i> f38146

Союз Советскня

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕДЬСТВУ, --.

3 Г - Б

j ?PJ S.! "« ),",(;, ","; «.y » (51)М, Кл.

Н Оз К 13/Ог (61) Дополнительное к авт. свид-ву (22) Заявлено 250577 (21) 2488786/18-21 с присоединением заявки ¹ (23) Приоритет

Государственный комитет

СССР по делам изобретений н открытий

Опубликовано 3005.80 Бюллетень № 20 (53)УДК 681 325 (088. 8) Дата опубликования описания 30.05,80 (72) Авторы изобретения

P.Т Сафаров н В Б Краскнн (71) Заявитель (54) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ

Изобретение относится к телеметрии св язи.

Известно устройство преобразования дискретных сигналов, позволяющее каждую выборку представить в виде $ и-значного двоичного сигнала, содержащее коммутатор каналов, преобразователь аналог — цифра, накопитель, преобразователь кода и передатчик (1).

Недостатком этого устройства является то, что ри передаче цифровых сигналов простым двоичным кодом при равномерном законе распределения значений выборок исходных сообщений на каждую выборку s среднем -"- еди- 15 ничных посылок.

Известно устройство преобразования дискретных сигналов, содержащее преобразователь аналог-цифра, соединенный через анализатор качества 2О посылок с триггером, синхронизатором, выходы которого соединены с синхронными входами преобразователя аналог-код, триггера и синхронизатора (2) ° 25

Недостатком устройств а является необходимость применения на приемной стороне преобразователя сигналов и сложной схема символьной синхронизации . ЗО

Цель изобретения — обеспечение

:энергетического выигрыша и уменьше ния до нуля систематической ошибки квантования. указанная цель достигается тем, что в устройство преобразования дискретных сигналов, содержащее преоб разователь аналог-цифра, синхрониэа» тор, преобразователь кодойого сиг» нала, передатчик,к первому выходу преобразователя аналог-цифра подключены запараллеленные первые, а к второму выходу — эапараллеленные вторые входы элементов И от первого до (и - 2)-го, к-й выход преобразователя аналог-цифра подключен на эапарал,леленные к-е входы элементов И ог (к — 1)-го до (и - 2)-го, где к

=3, 4,..., n — 1; и-й выход преобразователя аналог-цифра подключен на запараллельные первые входы элемента ИЛИ и дополнительного элемента И, Выход ка)кдого элемента И присоединен к"первому входу соответствующего логического устройства, у каждого иэ которых, кроме первого, первый вход предыдущего устройства соединен с вторым входом последующего устрбйст ва, а второй вход первого логического устройства связан с первым вы 738146 ходом преобразователя аналог-цифра.

Третьи эапараллеленные входы всех,. логических устройств подключены к выход(у дополнительного элемента И, а четвертый вход каждого логического устройства связан соответственно с (r + 1)-м входом элемента И, где

r=l, 2,..., n - 2. Выходы всех логических устройств, а также выход элемента ИЛИ соединены с входами преобразователя кодового сигнала.

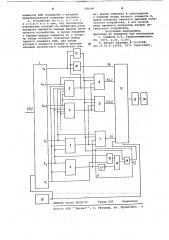

Логическое устройство состоит из инвертора, вход которого является первым входом логического устройства, а выход соединен с первым входом элемента И, к второму входу которого подключен выход первого элемента ИЛИ, два входа которого являются вторым и третьим входами логического устройства. Выход элемента И присоединен к первому входу второго элемента И, выход которого является выходом логического устройства, а его второй вход является четвертым входом логического устройства, Структурная электрическая схема устройства приведена на чертеже.

Устройстso содержит преобразователь 1 аналог-цифра, элементы и

2, 3, 4, 5 {их число равно n — 2), логические устройства 6, 7, 8, 9 (их число равно n — 2), элемент ИЛИ

10, дополнительный элемент И 11, преобразователь 12 кодового сигнала, модулятор 13, передатчик 14 и синхронизатор 15. Логическое устройство состоит иэ первого элемента ИЛИ 16, инвертора 17 элемента И 18 и второго элемента ИЛИ 19.

Устройство работает следующим образом.

Если посылка младшего разряда

x =О, то на выходе элемента И 2 будет

О, на выходе инвертора 17 1 ; если посылка х --õ, т.е. если х =О, то х =Оу если х = 1, то х =1 °

КОогда посылка х, =1, To npH х =О. на выходе элемента И 2 будет 0, на выходе инвертора 17 1, на выходе элемента 16 также 1, на выходе элемента 18 — 1 и х, =1.

Если х =1, то при х =1 на выходе инвертора 17 будет О, на выходе элемента 18 тоже 0 и х =О, а сигнал х будет зависеть от хЗ, Если

I 2

Ф х -0 то х =l если х =1, то х =О.

Р 3 3 и т.д.

Элементы 10 и 11 предназначены для того, чтобы при входном сигнале, состоящем из одних единиц (х4=1, х =1, х„ =1, х, =1) выходной сигнал также состоял йз единичных сигналов,.

I 1 i т Еер Чтобы ха=li х 3=1 ° ° ° ° i xi=1»

Действительно, если х =х = ° ° =. хл- =1 то сигнал на выходе элемента И 5 будет равен 1. Тогда при х =1 сигнал на выходе элемента И 11 будет равен

1 и он пройдет через элемент ИЛИ 19 всех логических устройств., а сигнал х„=l пройдет на вход преобразователя 12 через элемент ИЛИ 10.

Прн равномерном законе распределения значений выборок, передаваемых и-значными двоичными сигналами, т.е. когда с одинаковой вероятностью встречаются любые из 2 и-значных сигналов от 0000...00 до 111...11, относительное уменьшение количества единичных посылок (в импульсном канале это будут импульсы) и-2

2(-2)-

1 =.1 и-1 и 2 и. 2.

Одновременно с этим систематическая ошибка квантования становится равной нулю.

Кроме того, отбрасывание последней нулевой посылки (х„ = О) всегда позволяет либо увеличить скорость передачи информации, либо увеличить средний интервал между импульсами.

Формула изобретения

1. устройство преобразования дискретных сигналов, содержащее преобразователь аналог-цйфра, вход которого соединен с выходом синхронизатора и с синхронным входом преобразователя кодового сигнала, выход которого через модулятор соединен с входом передатчика, о т л и ч а ю щ е е с я тем, что,:с целью обеспечения энергетического выигрыша и уменьшения до нуля систематической ошибки квантования, к первому выходу преобразователя аналог-цифра подключены запараллеленные первые,а к второму выходу— запараллеленные вторые входы элементов И от первого до (n-2)-ro,ê-й выход преобразочателя ачалог-цифра подключен назапараллеленчые к-е входы элементов И от (к -1)-ro до (n — 2)- . го, где к=3, 4,..., n — 1; и-й выход преобразователя аналог-цифра подключен на запараллеленные первые входы элемента ИЛИ и дополнительного элемента И; выход каждого элемента И при соединен к первому входу соответствующего логического устройства, у каждого из которых, кроме первого, первых вход предыдущего устройства соединен с вторым входом последующего устройства, а второй вход первого логического устройства связан с первым выходом преобразогателя аналог-цифра; третьи запараллеленные входы всех логических устройств подключены к выходу дополнительного элемента И, а четвертый вход каждого логического устройства связан соответственно с (z + 1)-м входом элементов И, где

r=l 2,..., n - 2; выходы всех логических устройств, а также выход

738146 филиал ППП Патент, г. Ужгород, ул. Проектйая, 4 элемента ИЛИ соединены с входами преобразователя кодового сигнала, 2, Устройство по п,1, о т л и ч а ю ш е е с я тем, что логическое устройство состоит нз инвертора,вход которого является первым входом логического устройства, а выход соединен с первым входом элемента И, к второму входу которого подключен выход первого элемента ИЛИ, два входа которого являются вторым и третьим входами логического устройства схеьы; выход элемента И присоединен к первому входу второго элемента И, выход которого является выходом логического устройства, а его второй вход является четвертым входом логического устройства, Источники информации, принятые во внимание при экспертизЬ

1. Сафаров P,Т., Радиотелеметрия.

МО, 1973, ч.II с.201, 2. Патент Франции Р 2234708, ;кл. Н 03 К 13/02, 1975 (прототип).