Логическое устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИ.Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДИ ЕЛЬСТВУ (и 7381 71

Союз Советских

Социалистических

Республик (6! ) Дополнительное к авт. саид-ву— (22)Заявлено30.12.77 (2!) 2563618/18-21 (51)M. Кл, Н 03 К 19/08 с присоединением заявки РЙ—

Гасударственный кемнтет

СССР (26) Приоритет

Опубликовано 30.05.80.Бюллетень J% 20 (53) Д1(62). .3 74 {088.8 )

Дата опубликования описания 30.05.80 ао делам нэабретемкй н втхритнй

А. 3, Иванников, А. Д. Кравпов и В. Б, Летннков (?2) Авторы изобретения (71) Заявитель (54) ЛОГИЧЕСКОЕ УСТРОЙСТВО

Л!

Изобретение относится к автоматике телемеханике и вычислительной технике и может быть использовано в узлах стыковки логических и управляющих токовых сигналов, в частности как блок схемы управления постоянного репрограм5 мируемого запоминающего устройства с матрицей запоминающих элементов на основе халькогенидных стекол.

Известно логическое устройство (фортО мирователь разрядной записи-усилитель воспроизведения), содержащее входные выходные и управляющие транзисторы, диоды и резисторы $1$

Это логическое устройство имеет весь- ма сложное построение, значительные потребляемую мощность и напряжение питания, снизить которые не представляется возможным.

Наиболее близким к предлагаемому по технической сущности является логическое устройство, содержащее две вхо дные цепи, два выходных двухэмиттерных транзистора, один из эмиттеров которых

2 подключен K базе того же транзистора и через соответствующий резистор - к ши те"нулевого =йж бййГаФа,=а второй"- не- по=редствевно к шиве. нулевого потенпи- ала. Коллекторы выходных транзисторов

"сбединены с соответствующими выходами устройства и через соответствующие резисторы - с шиной питания. ства управляющих транзистора также выполнены двухамиттерными, причем один из эмиттеров каждого иэ этих транзисторов подключен к базе того же транзистора и через собтветствующий резистор к шине нулевого йотенциапа, а второй непосредственно — к шине нулевого потенциала. Коллекторы""уйравляющих трайзисторов объединены и через резистор подключены к шине питания, а также через диод ь rtpsiмом включении - к базе первого выходного транзйстора (2

Недостатки известного устройства заключаются в сложности конструктивного исполнения, в том, что логические сигналы на выходах устройства действуют в з 73&i 7 противофазе, что ограничивает возмож- ности применения его в ПЗУ, а также в значительной площади, занимаемой на кристалле в интегральном исполнении (вследствие включения в устройство многоэмиттерных транзисторов и шести диодов).

Цель изобретения — расширение функциональных возможностей устройства, снижение потребляемой мощности, повышение надежности и улучшение температурного режима.

Поставленная цель достигается тем, что в логическом устройстве, содержащем два входных, два выходных и управляющий транзисторы, диод и резисторы, эмиттеры входных транзисторов подключены к соответствующим входам устройства, базы- через резисторьг к источнику питания, коллектор второго выходного транзистора подключен к соответствующему выходу устройства и через резистор — к источнику питания, а эмиттеры выходных транзисторов — к шине нулевого потенциала, коллектор первого входного транзистора соединен с базой управляющего транзистора, эмиттер которого подсоединен к коллектору первого вь1ходного транзистора, база которого связана с катодом диода, а анод — с коллек- 3О тором второго выходного транзистора, а коллекторы управляющего и первого выходного транзисторов через соответствую1 щие резисторы подключены к первому выходу устройства. 35

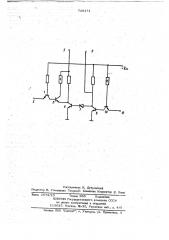

На чертеже схематически представлено логическое устройство.

Эмиттер первого входного транзистора 1 подключен к первому входу 2 устройства. База транзистора 1 через резистор соединена с источником питания

+Е„, . Коллектор транзистора 1 связан с базой управляющего транзистора 3. Коллектор транзистора 3 через резистор 4 подсоединен к первому выходу 5 устрой- ства. Эмиттер транзистора 3 подключен к коллектору первого выходного транзистора 6 и через резистор к первому выходу 5 устройства. Эмиттер транзистора

6 соединен с шиной нулевого потенциала, а база его — с катодом диода 7, анод которого связан с коллектором второго выходного транзистора 8, со вторым выходом 9 устройства и через резистор— с источником питания. Эмиттер транзистора 10 подсоединен ко второму входу устройства 12, Таким образом, устройство содержит два управляющих входа (2- информацион1 ф ных сигналов логического "0" или "1" и 12 — выбора режима), подача сигналов на которые обеспечивает управление состояниями двух выходов (9 — с действующими потенциалами сигналов логического

"О" или "1", 5 — с действующими трехуровневыми токовыми сигналами (отсутствие тока, нормированный ток малой величины, нормированный ток большой величины), Это позволяет выходными потенциальными сигналами логического 0" или "1" с выхода 9 управлять режимом работы блоков схемы управления путем разрешения или запрета работы блоков, а токовые выходные сигналы с выхода 5 использовать для записи информации в ячейки матрицы памяти.

Логическое устройство работает следующим образом.

Пусть ко входу 12 приложен потенциал логической "1" и по эмиттеру транзисторы 10 действует втекающий ток.

От источника питания + через резистор

11, открытый переход база-коллектор тран. зистора 10 в базу транзистора 8 протекает ток, Транзистор 8 открывается и пропускает ток от Г„. На выходе 9 устанавливается потенциал логического "0", который прикладывается также к аноду диода 7. Транзистор 6 заперт из-за отсутствия базового тока, через транзистор

6 и выход 5 ток не протекает, независимо от состояния транзистора 3 и сигнала по входу 2.

При действии по входу 12 сигнала "логического "0" ток от источника питания

- Е„через резистор 11 и переход базаэмиттер транзистора 10 замыкается на источник входного сигнала логического

"0 . Отсутствие базового тока транзистора 8 запирает транзистор, и по выходу

9 устанавливается потенциал логической

"1", который через диод 7 отпирает переход база-эмиттер транзистора 6 . Через открытый транзистор 6 образуется цепь для протекания токового сигнала по Bb ходу 5;: Нормирование величины этого токового сйгнала производится управляющим сигналом по входу 2. Пусть ко входу 2 приложен потенциал логического "0". Ток через переход база-эмиттер транзистора

1 замыкается на источник входного сигнала. Транзистор 3 заперт,,и цепь из резистора 4 и закрытого транзистора 3 не шунтирует резистор в коллекторе транзистора 6. Величина тока, протекающего по пепи выход 5 и открытый транзистор 6, нормируется величиной резисторов в коллекторе транзистора 6.

738171

Запись

Считываниее

"1 "О" . "О" 1" приДО

-"-1" "1 "0" 1 при,7= О

I ф о р м у л а и з о б р е т е н и я ния температурного режима, коллектор первого входного транзистора соединен

Логическое устройство, содержащее с базой управляющего транзистора, амитдва входных, два выходных и управляющий тер которого подсоединен.r,.ê коллектору транзисторы, диод и резисторы, эмиттеры О первого выходйого транзистора, база ко входных транзисторов подключены к соат- торого связана с катодом диода, а анодветствующим входам устройства, базы« с коллектором второго выходного трап= через резисторы к источнику литания, . зистора, а коллекторы управляющего и

1 коллектор второго выходного транзистора первого выходного транзисторов через подключен к соответствующему выходу 4 соответствующие резисторы цодключепы . устройства и через резистор к источии- к первому выходу устройства. ку питания, а эмиттеры выходных трап- -+"-"= - Источники информации, зисторов — к шине нулевого потенциала, принятые во внимание при экспертизе о т л и ч а ю щ е е с я тем, что, с ...;.. 1. "Каталог интегральных микросхем, целью расширения функциональных воз- о ч. 1, изд. ЦБП, 1973-1974, с.,260, . можностей, снижения потребляемой мощ- 2„, ИМС К134РУ6 ЧТУ бКО 347, ности; повышения надежности и улучше- 083 Т49 (прототип).

При действии по входу "2 управляющего потенциала логической "1" протекающий через резистор в цепи. базы транзистора 1 ток от источника +Е„отпирает транзистор 3. 9то приводит к подключению к коллектору транзистора 6 шунтирующей цепи из.резистора .4 и открытого транзистора 3, что обеспечивает протека-ние по цепи выход 5 и открытый транзистор 6 второго нормированного значения тока.

Работа устройства определяется таблицей истинности.

Предлагаемое устройство отличается простотой исполнения всего лишь 5 транзисторов, 1 диод, 5 резисторов.

Оно позволяет расширить функциональные возможности, т.е. обеспечить трехуровневь5е выходные токовые сигналы с нормированными величинами токов по вы, 1

5 "ходу 5 и логические управляющие сигналы по выходу 9, что существенно расши ряет область использования устройства.

Уменьшение числа элементов и возможность снижения напряжения питания

1 до 2,5 В обеспечивает снижение потребляемой устройством мощности. Кроме то го обеспечивается улучшение температурного режима кристалла и повышение надежности устройства за счет уменьшения

15 общего числа элементов,: межсоединенйй и количества контактов.

738171

Составитель Н. Дубровский

Редактор В. Романенко ТехредН. Ковалева Корректор Е. Папп

Заказ 2574/10 Тираж 995 Подписное

IIHHHHH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4