Устройство для измерения вероятностных характеристик процессов восстановления синхронизма по циклам

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ рщ 738183

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВЯДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 19.1277 (21) 2556018/18-09 (51)М. Кл.2

Н 04 В 3/46 с присоединением заявки ¹

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет.

Опубликовано 3005;80. Бюллетень № 20

Дата опубликования описания 3005,80 (53) УДК621. 394. .662.2 (088.8) Г. В.Коновалов, Э.И.Лангуров;

Н. В . Михайлов и Г.С. Рудс кая (72) Авторы изобретения е . 3 (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ BEPORTUOCTRblX XAPARTEPHCTHK

ПРОЦЕССОВ ВОССТАНОВЛЕНИЯ СИНХРОНИЭИА ПО ЦИКЛАМ. Изобретение относится к радиотех- нике и может использоваться в устройст вах, обеспечивающих синхронизм источников и приемников информации в системах передачи дискретных сообщений.и в системах с цифровыми методами модуляции аналоговых сигналов.

Известно устройство для измерения вероятностных характеристик процессов восстановления синхрониэма по циклам, содержащее последовательно соединенные блок формирования управляющей последовательности и формирователь импульсов сбоя, запрещающий вход которого соединен с вы-. ходом счетчиха числа испытаний, а" также формирователь сигналов времени и регистратор (1), Однако известное устройство, имеет недостаточную точность измерений и не позволяет измерение таких важных характеристик устройства цикловой синхронизации, как время обнаружения отсутствия синхронизма и ложных фиксаций состояния синхронизма.

Цель изобретения — повышение точности измерений.

Для этого в устройство для измерения вероятностных характеристик процессов восстановления синхрониэ= ма по циклам, содержащее последовательно соединенные блок формирования управляющей последовательности и формирователь импульсов сбоя, запрещающий вход которого соединен с "выходом счетчика числа испытаний, а также формирователь сигналов времени и регистратор, введены блок обнаружения ложного фазирования,блок определения времени обнаружения отсутствия синхронизма, блок определения вРемени поиска синхронизма, блок установки допустимого времени восстановления синхрониэма, блок сравнения и элемент ИЛИ, при этом выход формирователя импульсов сбоя, являющийся выходом устройства, подключен к входу счетчика числа испы-

2О таний и к объединенным первым вхо дам бло<а сравнения, блока обнаружения ложного фазирования и блока определейня времени,обнаружения отсутствия. синхроннзма, второй вход которого, являющийся входом устройства, аоединен с вторым входом блока обнаружения ложного фаэирования и первым входом блока определения вре.— мени йоиска синхронизма, второй вход

ЗО

738183!

Ф которого Соединен с выходом формиро вателя сигналов времени и с третьим входом блошка определения времени обнаружения отсутствия синхронизма, выход которого подключен к первому входу элемента ИЛИ,. второй -вход которого соединен с выхбдом блока определения времени поиска синхронизма, выход которого, а также выходы бло« ка определения времени обнаружения огсутствйя синхронизма, блока установки допустимого времени восстановления синхронизма и элемента ИЛИ подключены к соответствующим входам блока сравнения, выход которого и вы 1 ния ложного фазирования, блок 5 определения времени ООС, блок б сравнения

Так как известно число испытаний, а ледозатеЖйо, и число выводов устройства цикловой синхронизации, то с помощью блока 4 обнаружения ложного фазирования может быть выявлено число лишних срабатываний индикатора состояния синхронизма, которое отме10 чается регистратором 10.

Среднее время восстановления синхронизма и его составляющие: время обнаружения отсутствия синхронизма ходы блока определения времени обнаружения отсутствия синхронизма, блока определения времени поиска синхронизма, блока обнаружения ложйого фази" рования и элемента ИЛИ подключены к соответствующим .входам регистратора, кроме. того, блок обнаружения ложного фазирования содержит триггер с раздельным запуском, входы которого являются входами блока,и элемент И, первый и второй входы которого соединены.соответственно с выходом и вторым входом триггера, а выход элемента И является выходом блока.

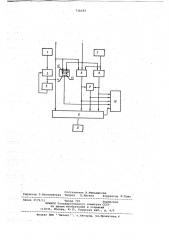

На чертеже приведена структурная электрическая схема предложенного устройства. устройство для измерения вероятностных характеристик процессов восстанбвления синхронизма по циклам содержит блок 1 формирования управ-. ляющей последовательности, формирователь 2 импульсов сбоя, счетчик 3 числа испытаний, блок 4 обнаружения ложного фазирования, блок 5 определения времени обнаружения отсутствия синхронизма (00C), блок б сравнения, формирователь 7 сигналов времени, блок 8 определения времени поиска синхронизма, элемент 9 ИЛИ, регистратор 10, блок ll установки допустй-" " мого времени восстановления синхро.низма, блок 4 обнаружения ложного фазирования .содержит триггер 12 с раздельным запуском н элемент 13 И, Устройство работает следующим образом.

Блоком 1 формирования управляющей последовательности формируется последовательность, период которой заведомо превышает время восстановления потерянного синхронизма по циклизм, подается на вход формирователя 2 импульсов сбоя, обеспечивающего формирование импульсов сбоя, число которых соответствует числу испытаний, определяемому счетчиком 3 числа исйытаний. По заполнении счетчика 3 выдается сигнал, который запрещает дальнейшее фоомирование импульсов

"сбоя, Импульс сбоя поступает на передатчик синхросигнапа"и изменяет,ego взем4нное положение, кроме того, пс дготавливает к работе, блок 4 обнаоуже15

65 и время поиска и фиксации синхронизма — измеряются в нормированных интервалах времени с помощью блока 5 определения времени ООС, блока 8 оп-. ределения времени поиска синхронизма и элемента 9 ИЛИ, Через блок 5 определения времени ООС и блок 8 определения времени поиска синхронизма проходит некоторое количество временных меток, например,испульсов с частотой следования. циклов, формируемых формирователем 7 сигналов времени. Для блока 5 определения времени 0ОС это число определяется отрезком времени с момента изменения фазы синхросигнала до выхода устройства цикловой синхронизации из состояния синхронизма, т.е. до переключения индикатора состояния синхронизма в режим поиска, Блок 8 ойределения времени поиска синхронизма формирует количество импульсов, соответствующее отрезку времени, в течение которого индикатор состояния синхронизма индицирует режим поиска. Результаты, полученные на выходах блока 5 определения времени ООС и блока 8 определения времени поиСка синхро.— низма, суммиоуются с помощью элемента 9 ЙЛИ для получения количества меток," соответствующего общему времени восстановления синхронизма.

С выходов блока 5 определения времени OQC, блока 8 определения времени поиска синхронизма и элемента 9 ИЛИ метки времени, соответствующие процессу восстановления синхронизма, подаются на регистратор 10, а также на блок б сравнения, с помощью котброго осуществляется измерение дифференциальной и интегральной функций распределения общего времени восстановления синхронизма, времени обнаружения отсутствия синхронизма и суммарного времени восстановления синхронизма;

Измерение функции распределения осуществляется следующим образом.

С помощью блока 11 установки допустимого времени восстановления синхронизма устанавливается необходимая цифра, соответствующая аргументу дифференциальной или интеграль ной функции, 73.8183 с

В зависимости от установленного блоком 11 установки допустимого времени восстановления синхронизма дво- . ичного числа нормированных интервалов на выходе блока 6 сравнения появляется определенное количество импульсов, соответствующих восстановлению потерянного.синхронизма за строго определенное, или не превышающее его, число нормированных интервалов времени, подающееся на вход регистратора 10, Полученные таким образом результаты позволяют, получить интегральную и дифференциальную функции рас пределения подаваемого на вход блока б сравнения числа нормированных интервалов времени с выходов блока 5 распределения времени 00С,.блока 8 определейия времени поиска .синхронизма и элЕмента 9 ИЛИ.

С помощью предложенного устройст- . ва можно выявить число ложных фиксаций состояния синхрониэма, измерить средние значения общего времени восстановления синхрониэма, времени обнаружения отсутствия состояния синхронизма, времени поиска и фиксации состояния синхрониэма, а также дифференциальную и интегральную функции распределения укаэанных времен процесса восстановления синхронизма.

6 установки допустимого временй вбсстановления синхронизма, блок бравнения и элемент ИЛИ, при этом выход формирователя импульсов сбоя, являющийся выходом устройства, подключен к входу счетчика числа испытаний и к объединенным первым входам блока сравНений, блока обнаружения ложного фазирования,и блока определения времени обнаружений отсутствия синхронизма, второй вход которого, являющийся входом устройства, соединен с вторым входом блока обнаружения ложного фазирования и первым входом блока определения времени поиска синхрониз ма, второй вход которого соединен

15 с выходом формирователя. сигналов времени и с третьим входом блока QIlределения времени обнаружения отсутствия синхронизма,выход которого подключен к первому входу элемента ИЛИ, 2О второй вход которого соединен с выхо. дом блока определения времени поиска

--синхронизма, .выход которого, а также выходы блока определения времени обнаружения отсутствия синйрбнизма, блока установки допустимого времени восстановления синхронизма и элемента ИЛИ подключены к соответствующим

:-- - Входам блока сравнения, выход которого и выходы блока определения времени обнаруженйя отсутствия синхронизма, блока определения времени .- ..пойска синхронизма,блока обнаружения, Формула изобретения

1. Устройство для измерения вероятностных характеристик процессов восстановления синхронизма по циклам, содержащее последовательно соединенные блок формирования управляющей последовательности и формирователь импульсов сбоя, запрещающий вход которого соединен с выходом счетчика числа испытаний, а также формирователь сигналов времени и регистратор, о т л и ч а ю щ е е с я тем, что, с целью повыаения точности измерений, введены блок обнаружения ложного фазирования, блок определения времени обнаружения отсутствия синхронизма, блок определения времени поиска синхронизма, блок ложного фаэирования и элемента ИЛИ подключены к соответствующим входам .регистратора.

35:"

2. Устройство по п,1, о т л и ч а ю щ е е с я тем, что блок обна- ружении ложного фази1 ования содержит

45 триггер с раздельным запуском, входы которого являются входами блока, и элемент И, первый и второй входй которого соедйнены соответ ственно с выходом и вторым входом триггера, а выход элемента И является выходом блока.

Источники информации, принятые во внимание пои экспертизе

1 . Авторское свидетельство СССР

Р 280526, кл. Н 04 Ь 7/02, 1968 (прототип).

) 738183

Составитель A.Ìåíüøèêoâà

Редактор Л.Веселовская Техред О.Легеза Корректор М.Пожо

Эаказ 2579/11 Тиоаж 729 Подписное

11НИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г.ужгород, ул.Проектная,4