Процессор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТИЛЬСТВУ

Сова Советских

Социалистических

Республик (и1739539 (б1) Дополнительное к авт; свид-ву

1 (22) Заявлеио1ЯИ77 (21) 2462586/18-24 (51)М. Кл.

G 06 F 15/00 с присоединением заявки №Государретвеииый комитет

СССР по делам изобретений и открытий (23) Приоритет—

Опубликовано 0506.80. Бюллетень ¹21 (53) УДК 681.14 (088. 8) Дате опубликования описания 0506.80

{72) Авторы изобретения

В.A. ГУляЕв, В.A. Иванов, A.В; Палагин и П.М. Сиваченко.

Институт электродинамики AH Украинской CCP (71) Заявитель (54) ПРОЦяССОР

Изобретение относится к области. вычислительной техники и может быть использовано в вычислительных системах различного назначенйя.

Известны процессоры (1 J содержащие устройство управления, генератор синхросигналов, операционное устройство со средствами контроля и блок синхронизации. Принцип работы устройства состоит в том, что по сигналу детектора ошибки запускаются средства, обеспечивающие выработКу специальных синхросигналов с периодом повторения, превьыающим перибд повторения рабочих синхросигналов на время переходного про- . цесса.

Недостатком устройства является бо®ьшое время контроля из-sa низких диагностических свойств, обусловленных тем, что устройство управления и операционное устройство работают на одинаковой частоте следования синхросигналов и устройство управления не успевает анализировать результаты преобразований в операционном устройстве.

Наиболее близким по технической сущности к изобретению является процессор (21, содержащий блок микропрограммного управлени я, соединенный двусторонней связью с регистром микрбкоманд, выход которого подклю- . чен ко входу дешифратора микрокоманд, операционный блок, вход и выход которого.подключены соответственно к выходу дешифратора.микрокоманд и адресному входу блока микропрограммного управления, и блок синхронизации, включающий узел формирования основных и рабочих .тактовых импульсов, соединЕнный группой выходов с группой входов узла распределения тактовых импульсов, первая группа выходов которого подключена к группе входов синхронизации блока микропрограммно го управления.

Однако надежность этого устройст ва недостаточна из-за значительного ,времени, необходимого для проведения тактового контроля в случаях по- явления неисправностей как в самом процессоре, так и в вычислительной системе в целом, Целью изобретения является повышение надежности работы.

Поставленная цель достигается тем что в предложенном процессоре

739539 в блок синхронизации введены узел формирования®контрольных тактовых импульсов, триггер управления, две группы элементов И и группа элеменboa ИЛИ; выходы которых соединены с группой входов синхронизации операционного блока. Входы триггера управления соединены с соответствующими- дополнительными выходами дешифрато- . ра микрокоманд. Выходы второй группы выходов узла распределения тактовых импульсов подключены ко входам соответствующих элементов И первой группы, управляющие входы которых соединены с первым выходом триггера управления, а выходы — с первыми входами элементов ИЛИ группы. Вы<оды узла формирования контрольных тактовых импульсов подключены ко входам соответствующих элементов .И второй группы, управляющие входы которых подключены ко второму выходу тригге- 20 ра уйравления, а выходы - ко вторым входам соответствующих элементов

ИЛИ группы.

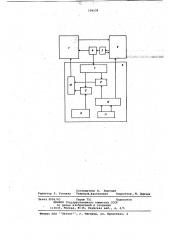

На чертеже дана структурная схема процессора.

Он содержит операционный блок 1, блок 2 микропрограммного управления, регистр 3 микрокоманд, дешифратор 4 микрокоманд, блок 5 синхронизации, включающий узел 6 формирования контрольных тактовых импульсон:, триггер 7 управления, первую 8 и вторую 9 группы элементов И, группу 10 элементов ИЛИ, узел 11 формирования основных и рабочих тактовых импульсов и узел 12 распределения так- N товых импульсов °

Устройство работает следующим образом.

При нормальной работе процессора рабочие тактовые импульсы, вырабатываемые узлом 11, поступают с выходов узла 12 на входы синхронизации блока 2 и блока 1, причем на входы последнего эти тактовые импульсы посту-пают через элементы И первой группы

8, открытые управляющим сигналом с . нулевого выхода триггера 7 который установлен н единичное состояние сигналом с выхода дешифратора 4.

При обнаружении ошибки в работе процессора осуществляется переход О на программу, поиска неисправности.

Одна из микрокоманд этой программы вызывает переключение триггера 7 в единичное состояние, что вызывает снятие разрешающего сигйала с эле- Я

;ментов И группы 8 и подачу его с единичного выхода триггера 7 на управляющие входы элементов И группы 9.

В результате на входы синхронизации блока 1 через группу 9 элементов И начинают:поступать тактовые импульсы, ФОРМиРуемые узлом 6.

Если частота тактовых импульсов, поступающих иэ узла б, ниже частоты тактовых импульсов, генерируемым узлом 12, то в режиме поиска неиспранностей блок 2 может работать с более высокой частотой, чем блок 1. Это обеспечивает возможность анализа результата выполнения микрооперации до начала выполнения другой, и, следовательио, облЕгчает процесс поиска неисправностей и исключает необходимость перезапуска процессора для повторения ситуаций. 1аким образом, предложенный процессор позволяет упростить процедуры поиска неисправностей, сократить мх количество, повысить разрешающую способность диагностирования и снизить за счет этого время контроля. формула изобретения

Процессор, содержащий блок микропрограммного управления, соединенный двусторонней связью с регистром микрокоманд, выход которого подключен ко входу дешифратора микрокоманд, операционный блок, вход и выход которого подключены-соответственно к выходу дешифратора микрокоманд и адресному входу блока микропрограммного управления, и блок синхронизации, включающий узел формирования оснонных и рабочих тактовых импульсов, соединенный группой вы-. ходов с группой входов узла распределения тактоных импульсов, первая группа выходов которого подключена к группе входов синхронизации блока микропрограммного управления, отличающийся тем, что, с целью повышения надежности, в блок синхронизации введены узел формирования контрольных тактовых импульсов, триггер управления, две группы элементов И и группа элементов ИЛИ, выходы которых соединены с группой входов синхронизации операционного блока, а входы триггера управления соединены с соответствующими дополнительными выходами дешифратора микрокьманд, причем выходы иэ второй" группы выходов узла распределения тактовых импульсон подключены ко нходам соответствующих элементов И первой группы, управляющие входы которых соединены с первым выходом триггера управления, а выходы - с первыми нходами элементов .

ИЛИ группы, выходы узла формирования контрольных тактовых импульсов подключены ко входам соответствующих элементов И второй группы, управляющие входы которых подключены Ко второму выходу триггера управления, а выходы - ко вторым входам соответствующих элементов ИЛИ группы.

Источники информации, принятые во внимание при экспертизе

1. Патент CIIlA 9 3868647, Н. кл. 340-172.5, 1970.

2. Процессор ЭВИ ЕС-1020. М., - Статистика, 1975, гл.1,2, рис.1,. (прототи ) .

739539

Составитель В. Вертлиб

Редактор Л. Утехина ТехредЖ.Кастелевич КорректоР ° М. Демчик

Заказ 2926/43 Тираж 751 Подписное

ЦНИИПИ Государственного ксыитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4