Цифровой измеритель временных интервалов

Иллюстрации

Показать всеРеферат

ОПИСдНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (iii739569

Союз Советских

Социалистических

Республик (6I) Дополнительное к авт. свид-ву— (22) Заявлено 19.04.78 (21) 2599101/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл

С 06 J 3/00

G 11 С!1/00

Государственный комитет

СССР

Опубликовано 05.06.80. Бюллетень №21

Дата опубликования описания 15.06.80 (53) УДК 628.327..6 (088.8) по делам изобретений и открытий (72) Авторы изобретения

А. Г. Алексенко, К. А. Гасумян, В. К. Камотесов, Ю. П. Иванов, Г. П, Мозговой и И. И. Шагурин (7I ) Заявитель (54) ЦИФРОВОЙ ИЗМЕРИТЕЛЪ ВРЕМЕННЫХ

ИНТЕРВАЛОВ

Изобретение относится к измерительной и вычислительной технике и может быть использовано в радионавигации, радиолокации и в физических экспериментах, в которых необходимо с высокой точностью измерить временной интервал между сигналами.

Известны цифровые устройства для измерения временных интервалов, работающие по принципу заполнения измеряемого промежутка времени импульсами эталонной частоты, причем для уменьшения ошибки временной интервал заполняется импульсами и-тактного генератора эталонной частоты F>, сдвинутыми относительно друг друга на время 1/nF,, где n — целое положительное число (1) ..

В состав таких измерителей входит и-такт- ный генератор эталонной частоты, триггеры, вентили, счетные ячейки и логические схемы, осуществляющие связь регистрирующего счетчика со счетными ячейками. го . Наиболее близким к изобретению по технической сущности является цифровой измеритель временных интервалов, в котором производят статическую обработку большого числа измерений одного и того же временного интервала (2).

Целью изобретения является повышение точности однократного измерения временного интервала.

Указанная цель достигается тем, что в цифровой измеритель временных интервалов, содержащий многотактный генератор эталонной частоты, первый управляющий триггер, элемент блокировки, элемент И, и счетчик, введены второй управляющий триггер, блоки памяти с тремя группами входов и двумя группами выходов каждый, сумматор, блок управления с тремя группами входов и двумя выходами, причем элемент блокировки соединен соответственно с первым и вторым управляющими триггерами, первой группой входов блока управления, первого и второго блоков памяти и счетчиком, вторые группы входов первого и второго блоков памяти подключены к выходам многотактного генератора эталонной частоты, третья группа входов первого блока памяти соединена с выходом первого управляющего триггера, а третья группа входов второго блока памяти соединена с выходом второго управляющего триггера, первые группы выхо739569

3 дов первого и второго блоков памяти соединены с второй группой входов блока управления, а вторые группы выходов — с входами слагаемых сумматора, одни выходы "которого подключены к соответствующим входам элемента И, один из входов которого подключен к первому входу блока управления, выходы элемента И соединены с выходами устройства, выход переноса сумматора соединен с третьей группой входов блока управления, второй выход которого соединен с входом счетчика.

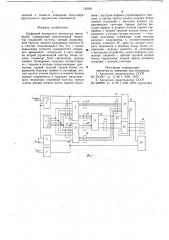

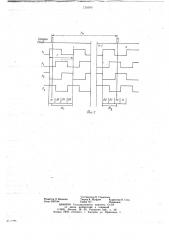

На фиг. 1 представлена схема цифрового измерителя временных интервалов; на фиг. 2 — временные диаграммы, поясняющие работу устройства на примере использования четырехтактного (и = 4) генератора эталонной частоты.

Предлагаемый цифровой измеритель временных интервалов содержит многотактный генератор эталонной частоты 1, управляющие триггеры 2 и 3, входы 4 и 5 которых соединены с выходом элемента блокировки 6

:...:;.=:=-.-;:и входами 7 и 8 блоков памяти 9 и 10.

Входы 11 и 12 этих блоков памяти соединены с выходами многотактного генератора эталонной частоты 1, а входы 13 и 14 соединены с выходами управляющих триггеров

2 и 3 соответственно. Выходы 15 и 16 блоков памяти 9 и 10 соединены с входами 17 блока управления 18, а выходы 19 и 20 соединены с входами сумматора 21, выход переноса 22 которого соединен с входом 23 блока управления 18, а выходы 24 сумматора 21 соединены с входами элемента И 25.

Выходы элемента И 25 соединены с выходами устройства 26. Вход 27 блока управления 18 соединен с выходом элемента блокировки 6 и счетчиком 28. Выход 29 блока управления 18 соединен с элементом И 25, а выход 30 — со счетчиком 28.

Измеритель работает следующим образом.

Перед измерением на вход элемента блокировки 6 подается сигнал «Пуск». Триггеры 2 и 3, блоки памяти 9 и 10, блок управления 18 и счетчик 28 устанавливаются в исходное состояние, при этом блоки памяти 9 и 10 не чувствительны к сигналам генератора 1. При приходе импульса «Старт» сначала измеряемого интервала Т управляющий триггер 2 меняет свое состояние и разрешает работу блока памяти 9, который запоминает количество импульсов тактовых последовательностей Fi, Г5, ..., Р„ генератора 1 от момента прихода «Старт» до ближайшего импульса основной последовательности F (интервал m, на фиг. 2), который делает нечувствительным блок 9 к сигналам генератор» 1. На выходе 19 появляется двоичный код, соответствующий интервалу m . Doc;Icëîâàòcëüíîcòü импульсов FI с выходов 15 поступает через блок

Измеритель может быть реализован в виде монолитной сверхбыстродействующей большой интегральной схемы. При этом существенно снижаются потребляемая мощность, вес и габариты измерителя, значительно повышаются надежность в резуль тате сокрашения числа внешних межсое4 управления 18 на счетчик 28. Приход импульса «Стоп» конца измеряемого интервала Т, приводит к изменению состояния управляющего триггера 3, который разрешает работу блока памяти 10, Блок памяти 10 запоминает количество импульсов последовательностей Fa, Рз, ...; Р„от момента прихода сигнала «Стоп» до ближайшего импульса последовательности F> (Ny, ), который делает нечувствительным блок 10 к сигналам генератора 1. На выходе 20 при этом

4у появляется двоичный код, соответствующий. интервалу от ближайшего импульса последовательности FI, предшествующего сигналу «Стоп», до момента появления сигнала «Стоп» (интервал m z на фиг. 2) . С выхода 16 сигнал Х „поступает на блок управления 18 и запрещает дальнейшее прохождение импульсов последовательности FI на счетчик 28. С выходов 19 и 20 блоков памяти 9 и 10 информация в виде двоичных чисел, соответствующих начальному m и конечному m> интервалам (фиг. 2) поступает на входы сумматора 21. С выходов 24 сумматора 21 информация поступает на элемент И 25. Так как сумма (mI + mq) может быть больше периода Т эталонной частоты FI, то возникает сигнал переноса, который с выхода 22 передается в блок управления 18, а затем с выхода 30 — в счетчик 28. При этом показание счетчика увеличивается на единицу. Блок управления передает в счетчик (N — 1) импульс последовательности F . Сигнал переноса, когда он возникает, поступает в счетчик с задержкой (по отношению к импульсу NI, ), необходимой для полного срабатывания сумматора 21, что устраняет ложные срабатывания счетчика. При этом с выхода 29 блока з5 управления поступает сигнал разрешения на элемент И 25, который пропускает на выходы устройства 26 сигналы N„(s двоичном коде) с выходов 24 сумматора: и f mI + mq, если mI + mq <(Т

Р т=.

Ъп + mq — Т, если m < + mq )T

Таким образом, длительность измеряемого интервала Т„, измеренная по показаниям счетчика NeII выходам устройства 26 равна:

Т вЂ”вЂ” Мс Т+ 1х1 .—,, Предлагаемый цифровой измеритель временных интервалов позволяет в п - раз, где и — число тактов многотактного генератора эталонной частоты, повысить точность измерения длительности временного интервала при его однократном измерении.

При этом логические и запоминающие элементы работают на частоте выше эталонной.

739569

5 динений и точность измерения благодаря идентичности параметров компонентов.

Формула изобретения

Цифровой измеритель временных интервалов, содержащий многотактный генератор эталонной частоты, первый управляющий триггер, элемент блокировки, элемент И и счетчик, отличающийся тем, что, с целью повышения точности однократного измере- 1 ния временного интервала, в него введены второй управляющий триггер, блоки памяти, сумматор, блок управления, причем элемент блокировки соединен соответственно с первым и вторым управляющими триггерами, первой группой входов блока управления, блоками памяти и счетчиком, вторые группы входов первого и второго блоков памяти подключены к выходам многотактного генератора эталонной частоты, третья группа входов первого блока памяти соедиь нена с выходом первого управляющего триггера, а третья группа входов второго блока памяти соединена с выходом второго управляющего триггера, первые группы выходов первого и второго блоков памяти соединены с второй группой входов блока управления, а вторые группы выходов — с входами слагаемых сумматора, одни выходы которого подключены к соответствующим входам элемента И, один из входов которого подключен к первому входу блока управления, выходы элемента И соединены с выходами устройства, выход переноса сумматора соединен с третьей группой входов блока управления, второй выход которого соединен с входом счетчика.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР .

М 391587, кл. G 08 С 9/00, 1970.

2. Авторское свидетельство СССР № 438998, кл. G 06 J 3/00, 1972 (прототип) ««@и@« @-" ..;,,;.« —. « -, ««=,« -. -, .:,- -,,- =« :: ««ад «« ъ д. ==. - " «@м«««««Ф« Ф- - «« «

739569

Составитель В. Гордонова

Редактор Л. Волкова Техред К. Шуфрич Корректор Н. Стец

Заказ 2927/44 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4