Усилитель записи-считывания для запоминающего устройства на дополняющих мдп-транзисторах

Иллюстрации

Показать всеРеферат

ОП ИС

Союз Советски к

Социалистически к

Республик (>739643

ИЗОБРЕТЕН ЙЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (5!)И. Кл. (22) Заявлено 02,11.77 (21) 2539005/18-24 с присоединением заявки ¹

Я 11 С 7/00

Государственный комитет

СССР (23.) П р и о р и тет

Опубликовано 05,06.80. Бюллетень № 21 по делам изобретений н открытий (53) УД 683 .327 ° .67 (088.8) Дата опубликования описания 07.06.80

В. В. Баранов, I0. М. Герасимов, А. Н. Кармазинский и Э. П, Савостьянов (72) Авторы изобретения (71) Заявитель (54) УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ

ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

НА ДОПОЛНЯЮЩИХ МДП-ТРАНЗИСТОРАХ

Изобретение относится к вычислительной технике и может быть использовано при построении микромошных запоминающих устройств на дополняющих МДП-транзисторах.

Известны усилители записи-считывания, построенные на основе ключа или триггера, в которых перед считыванием выходы и входы.закорачиваются,-с помощью специального транзистора flJ и (2) .

Недостатком схемы таких усилителей является сложность управления ее работой и критичность к фазовым соотношениям между управляющими сигналами.

Наиболее близким техническим решением к данному является усилитель записи считывания для запоминающего устройства на дополняющих МДП-транзисторах, содержащий четыре усилительных транзис тора, включенных по триггерной схеме, два2о нагрузочных транзистора, истоки которых подключены к шине питания и к истокам

Двух установочных транзисторов, стоки ко торых соединены с соответствующими стоками усилительных транзисторов и со стоками двух транзисторов сброса, истоки которых подключены к шине нулевого потенциала и к истокам одних усилительных транзисторов, стоки нагрузочных транзисторов соединены с истоками других усилителт ных транзисторов, и две шины управления, соединенные с затворами установочных транзисторов и с затвором дополнительного транзистора (3).

Недостатком известного усилителя записи-считывания является большое число транзисторов в нем, сложность схемы, боль шая плошадь на кристалле и невысокое быстродействие в режиме записи.

Пельто изобретении является увеличение быстродействия и упрощение усилителя.

Поставленная цель достигается тем, что в усилителе записи-считывания первая шина управления подключена к затворам транзисторов сброса, вторая — к затворам нагрузочных транзисторов, а затворь| уста7396 новочных транзисторов соединены соответственно со входом установки и со входом сброса усилителя.

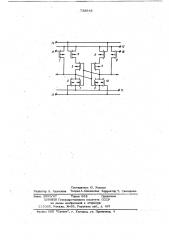

Схема усилителя записи-считывания представлена-на чертеже и содержит усилитель ные транзисторы 1-4, нагрузочные транзисторы 5 и 6, установочные транзисторы

7 и 8, транзисторы 9 и 10 сброса, шины

11 нулевого потенциала, питания 12, пер- вую 13 и вторую 14 управления, а также 10

15 установки и 16 сброса.

" Усилитель записи-считывания работает следующим образом.

В режиме хранения напряжение на шинах 13-16 соответствует уровню логичео- 15 кой единицы, так что транзисторы 9 и 10 открыты, а транзисторы 5-8 закрыты, и на выходах усилителя поддерживается напряжение логического нуля...

В режиме считывании транзисторы 7 20 и 8 остаются закрытыми. Первоначально сигнал логического нуля подается на шину 13,запирая транзисторы 9 и 10. Узло вые емкости на выходах триггера изолированы от источников питания и одна из них начинает заряжаться током считывания от выбранной ячейки памяти, которая через дополнительные транзисторы в памяти подключена к выходам усилителя записи-считывания. После того как напряжение на одном из выходов усилителя превысит некоторую величину (разбаланс усилителя), на.вторую шину 1 4 управления подается сигнал логического нуля и открываются нагрузочные транзисторы 5 и 6. После 35 этогз начинается форсированные заряд емкостей на выходах усилителя через последовательно соединенные транзисторы

3,5 или 4, 6 и регенеративный процесс, обеспечивающий в случае предварительно- 40 го установления на выходах необходимого разбаланса, быстрое переключение триггера в требуемое состояние. После окончания считывания сначала запираются транзисторы 5 и 6, а затем отпираются тран- 4> зисторы 9 и 10, обеспечивая установку усилителя в исходное состояние. -В режиме записи запираются транзисторы 9 и 10 и отпирается один из транзисторов 7 или 8 подачей сигнала логическо- 50 го нуля на один из входов 5 или 16 в зависимости от кода записываемой инфор;.

43 4 мации. Состояние шины 14 в режиме записи безразлично. В случае, если размеры,, транзисторов 7 и 8 имеют достаточную величину, происходит принудительная установка усилителя в требуемое состояние и последующая запись этой информациии в выбранную ячейку памяти.

В ряде случаев, при незначительном разбросе параметров транзисторов и строгом соблюдении фазовых соотношений между управляющими сигналами, допускается объединять шины 13 и 14.

Предлагаемый усилитель записи-считывания имеет на два транзистора меньше и проще, чем известный усилитель.

Формула изобретения

Усилитель записи-считывания для запоминающего устройства на дополняющих

МДП-транзисторах, .содержащий четыре усилительных транзистора, включенных по триггерной схеме, два нагрузочных транзистора, истоки которых подключены к шине питания и к истокам двух установочных транзисторов, стоки которых соединены с соответствующими стоками усилительных транзисторов и со стоками двух транзио— торов сброса, истоки которых подключены к шине нулевого потенциала и к истокам одних усилительных транзисторов, стоки нагрузочных транзисторов соединены с истоками других усилительных транзисторов, и две шины управления, о т л и ч аю шийся тем, что, с целью увеличения быстродействия и упрощения усилителя, первая шина управления подключена к затворам транзисторов сброса, вторая— к затворам нагрузочных транзисторов, а затворы установочных транзисторов соединены соответственно со входом установки и со входом сброса усилителя.

Источники информации, принятые во внимание при экспертизе

1. Патент Франции Хо 2317497, кл. 4 11 С 11/40, 1974.

2. "1ЕЕЕ 3. о1 So5ol ММе С1гспАь"„

SC -5, 1976, Мь й

3. "Электроника, 1975,.М 15, пер. с англ „с. 47-53 (прототип).

739643 т2

Составитель Ю. Ушаков

Редактор А. Ахмедова ТехреаА.Шепанская Корректор Т. Скворцова

Заказ 2950/47 Тираж 662 Подписное

БНИИПИ Гсосударственнога комитета СССР по делам изобретений и открйтий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4