Запоминающее устройство

Иллюстрации

Показать всеРеферат

4vy з, . с(1,;;я

О П И С Д Н М -1

Союз Советскик

Социалистических

Республик 1, 739646

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ф (б1) Доиолнительиое к авт. свил-ву— (22)3e eаеио 03.11.77 (21) 2540004/18-24

2 (51) М. Кл. с присоединением заявки №

G 11 С 11/00

Гесулзрстюавмв квинтет (23) Приоритет ессеи ае Аештт изэаретевий и етирыпе

Опубликовано 05 06 80, Бюллетень № 21

Дата опубликования описания 07.06.80 (53) УЛК 628 327 °.6(088,8) (72) Автор изобретения

И М Соколов (7l ) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

1

Изобретение относится к вычислительной технике и может быть использовано, в частности в микропрограммных устройствах управления.

Известны запоминающие устройства, содержащие группу многовходных схем

ИЛИ, кольцевые пересчетные схемы, накопитель, линию задержки, схемы И $1$.

Из известных запоминающих устройств наиболее близким к изобретению по технической сущности и по структурной схеме

10 является устройство $2) .

Бель изобретения — повышение надежности запоминающего устройства.

Бель достигается тем, что в запомиl5 нающее устройство, содержащее накопитель, первая группа выходов которого подключьнак ттервым входам блоков элементов И, вторая группа выходов - к соответствующим входам дешифратора, выходы которого подключены ко входам блоков элемента И, à входы накопителя подключены к выходам формирователя адреса, введены коммутаторы адреса и ошибки, одни входы

2 коМмутатора адреса подключены ко входам устройства, другие - к выходам коммутатора ошибки, управляющий вход коммутатора адреса и третьи входы блоков элементов И подключены к третьей группе входов накопителя, выходы коммутатора адреса подключены ко BxoQBM формирователя, а информационные и управляющие входы коммутатора ошибки подключены соответственно к первой группе выходов накопителя и выходам дешифратора.

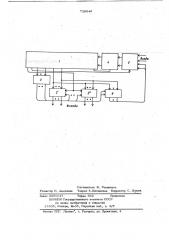

Схема устройства представлена на чертеже.

Предлагаемое запоминающее устройство содержит накопитель 1, первые выходы которого соедиьни ы с соответствующими входами групп схем И 2" — 2, вторые

0 выходы накопителя 1 соединены через дешифратор 3 с управляющими входами соответствующих блоков элементов И 2 - 2 и

1 а выходы накопителя 1 подключены через формирователь 4 адреса и коммутатор 5 ко входам устройства. Другие входы коммутатора 5 адреса подключены к выходам

3 7396 коммутатора 6 ошибки, связанного с первыми выходами накопителя 1 и с выходами дешифратора 3. Выходы третьей группы выходов накопителя 1 связаны с цепя ми управления коммутатора 5 адреса и элементов И 2 - 2

Yl

Предлагаемое запоминающее устройс1 во работает следующим образом.

В исходном положении на выходах .третьей группы выходов накопителя 1 долж- о ны формироваться единицы, которые o6ec» печив т подключение выходов устройства через соответствующие блоки элементов

И 2 - 2 к первой группе выходов накопителя 1 и входов устройства ко входам формирователя 4 адреса через коммутатор

5 адреса. При этом в накопителе 1 в соответствии с адресом, поступающим на его вход, формируются сигналы управления и код коммутации. Сигналы управления по- 20 ступают с первых выходов накопителя 1 параллельно на входы всех блоков элементов И 2 - 2 . Код коммутации поступ пает со вторых выходов накопителя 1 на входы дешифратора 3, обеспечивающего поМ ключение только одной (в соответствии с кодом коммутации) групп схем И 2 - 2

Ф

Выходное слово запоминающего устройства определяется суммой разрядов всех блоков элементов И 2 — 2 30

При наличии дефекта в запоминающих элементах каждого выбираемо-о слова из накопителя 1 в третьей зоне его должны быть записаны нули, обеспечиваюшие отключение всех блоков элементов И 2" — 2 З5

4и подключение входов формирователя 4 адреса через коммутатор 5 к выходам коммутатора 6 ошибки. При этом во второй зоне накопителя 1 должен быть записан код коммутации коммутатора 6 ошибки, обеспечивающего оподапочение входов его к группе исправных запоминающих ячеек первой группы выходов накопителя 1, в которой записан код адреса переадресации.

По этому коду адреса переадресации из накопителя 1 выбирается слово с заданными сигналами управления, кодом коммутации и с единицами, записанными в третью зону накопителя 1, которые обеспечивают подключение выходов устройства через

1 соответствующие блоки элементов И 246 4

2 к первой группе.выходов накопителя 1 и входов устройства ко входам формирс вателя 4 адреса через коммутатор 5 адреса.

В, предлагаемое запоминающее устройство дополнительно введены коммутаторы адреса и ошибки, а также ряд новых свя зей, что позволяет обходить неисправные ячейки памяти как в процессе эксплуатации, так и при изготовлении накопителя.

Эти нововведения позволяют также сократить количество брака, что особенно важно при изготовлении накопителя в интегральном исполнении и позволяет повысить надежность запоминающего устройства в работе.

Формула изобретения

Запоминающее устройство, содержащее накопитель, первая группа выходов которого подключена к первым входам блоков элементов И, вторая группа выходов — к ,соответствующим входам дешифратора, выходы которого подключены ко вторым входам блоков элементов И, а входы иаков пителя подключены к выходам формирователя адреса, о т л и ч а ю ш е е с я

1 тем, что, с целью повышения надежности устройства, оно содержит коммутаторы адреса и ошибки, одни входы коммутатора адреса подключены ко входам устройства, другие - к выходам коммутатора ошибки, управляюший вход коммутатора адреса и третьи входы блоков элементов И подключены к третьей группе входов накопителя, выходы коммутатора адреса подключены ко входам формирователя адреса, а информаIlHoBHbTe и управляющие axollbr коммутатора ошибки подключены соответственно к первой группе выходов накопителя к выходам дешифратора.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР № 337823р кл. & 1 1 С 1 1/00у

17.08. 70

2. Авторское свидетельство СССР № 490179, клюю-11 С 11/00, .21.12.73 (прототип).

739646

Составитель Ю. Розенталь

Редактор Н. Ахмедова Техред А.Кепанская Корректор С. 1UîM

Заказ 2950/47 Тираж 662 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

13035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП .Латент", r. Ужгород, ул. Проектная, 4