Программируемая логическая матрица

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Социалистичесиик .рес убл »739651 (63) Дополнительное к авт. свил-ву (22) Заявлено 04. 10.76 (21) 2409175/18-24 (5 I ) M. Кл.

g 11 С 15/04 с присоединением заявки № (23) Приоритет тееудерстееннв|Й квинтет

CCCP

l0 делам нзебретеннй н еткрьпнй

Опубликовано 05.06.80. Бюллетень ¹ 21 (53) УДК681.327..66 (088. 8) Дата опубликования описания 09.06.80 (72) Авторы изобретения

Ю. А. Алексеенко и Б. И. Рувинский л к ф д (," .;;т,Я Я Г gp r J g ; 1. . 1 (7!) Заявитель (54) ПРОГРАММИРУЕМ АЯ ЛОГИЧЕСКАЯ МАТРИ?И

4 ! 2

Изобретение относится к области авто- - Наиболее близким по технической сушматики и вычислительной техники и может ности к изобретению является програмнайти применение при разработке програм мйруемая логическая матрица 31, постмируемых логических матрип дпя управле роенная на МОП-транзисторах и состояния дискретными устройствами. щая из двух взаимно перпендикулярных матриц. Она содержит тс входных и выИзвестны программируемые логические ходных сигнальных щин. Между каждыми матрицьтааМОП-транзисторах f1j и Г2), co - двумя входными шинами расположена обстоящие из двух взаимно перпендикулярных щая земляная шина. матриц. Первая матрица представляет со- Недостатки известных матриц связаны бой.дешифратор к-разрядного входного сло- с их размерами, требования к которым

1.0 ва, имеютций т1 выходов, а вторая — попе ттрн реализации их на БИСах являются памяти ттт -разрядных выходных слов. Кон- очень жесткими; Наличие значительного етрукФивно матрицы построейы из парал- . числа конгактов, необходимых при перелельйо расположенных диффузионных шин, . ходе от одной матрицы к другой, снижает

15 между котбриьм могут бйть включены надежность MBTpHllbJ, транзйсторы, Между каждыми двумя вы- . Цейью"изобретения является упрощение ходиыми шинами расположена общая (эем- матрицы за счет уменьшения ее размеров ,- пиная) шина, что приводит к увеличению" при интегральном исполнении. йлощадй, aaaiwаемой программируемой ло- - Поставленная цель достигается тем, j ической матрицей при ее реализация на что в программируемую логическую мат. бопьшой интегральной схеме (БИС)(пло- риду, содержащую матричный дешифратор, .щадь БИС - основной фактор, влияющий состоящий иэ входных шин, соединенных на ее стоимость). с затворами МОП-транзисторов, «» <>а40. 3 7396 эи и шины нулевого потейциала, и матричный формирователь слов, состоящий иэ разрядных шин, выходной шины и МОПтранзисторов одного из столбцов матричных дешифратора и формирователя слов

S подключены соответственно к одной из шии связи и шине нулевого потенциала, стоки

МОИ-транзисторов других столбцов мат ричных дешифратора и формирователя слов соединены с другими шинами связи соответственно, введен распределитель импульсов, выходы которого соединены с сс ответствующими разрядными шинами и затворами MOII-транзисторов матричного формирователя. слов; а истоки МОП тран зисторов других столбцов матричных дешифратора и формирователя слов подключены к соответствующим шинам связи.

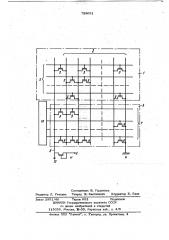

На чертеже изображена схема предложенной матрицы, г0

Программируемая логическая матрица содержит матричный дешифратор 1, состоящий из входных шин 2, шин 3 связи, шины 4 нулевого потенциала и МОПтранзисторов 5, матричный формирователь 25 слов 6, состоящий иэ разрядных шин 7, выходной шины 8 и МОП-транзисторов 9, и распределитель импульсов 10.

Входные шины 2 пересекают n + 1 шины связи 3, между которыми могут быть расположены транзисторы. Первая из + 1 .шин является выходной шиной

9 с нагрузочным транзистором 11, а последняя — шиной нулевого потенциала

4. nl разрядных шин 8 включены параллельно упомянутым входным шинам 2. Для упрощения чертежа приведена матрица с потенциальным питанием, однако,. все сказанное относится и к матрице с динамическим питанием.

Программируемая логическая матрица работает следующим образом. На к входных шин 2 поступает к разрядное входное слово, являющееся адресом m; разрядного выходного слова. При этом группа транзисторов, включенная между определенными L имя шинами связи запирается и па Bl:îäå 12 возникает сит нал "1 . После этого нащ шин поступает последовательность импульсов с распределителя импульсов. При этом на выходе 12 возникает сигнал О в случае появления импульсов на тех шинах, для которых в данной паре шин связи йрисутствуют транзисторы. Транзисторы на тг аннах 7. проставляются в соответ51 4 ствии с инверсным кодом выходного Фразрядного слова.

Таким образом, после прохождения импульсов на выходе 12 появляется последовательный код m -разрядного слова. В течение выборки всего rn -рмьрядного слова состояние к BxoQHblx lUHH, не изменяется.

Предложенная реализация программируемой логической матрицы увеличивает надежность ее работы при ее реализации на

МОП-БИС. Повышение надежности обеспечивается исключением контактов, необходимых при переходе от одной матрицы к другой при традиционной реализации. А размеры матрицы сокращаются в 1,5 раза, что снижает ее стоимость.

Формула изобретения

Программируемая логическая матрица, содержащая матричный дешифратор, состоящий из входных шин, соединенных с затвором МОП-транзисторов, шин связи и шины нулевого потенциала, и матричный формирователь слов, состоящий из разрядных шин, выходной шины и МОП-транзисторов, причем стоки и истоки NOII-транзисторов одного из столбов матричных дешифратора и формирователя слов подключены соответственно к одной из шин связи н шине нулевого потенциала, стоки МОПтранзисторов других столбцов матричных дешифратора и формирователя слов соединены с другими шинами связи соответственно, отличающаяся тем, что, с целью упрощения матрицы, она содержит распределитель импульсов, выходы которого соединены с соответствующими разрядными шинами и затворами МОП-транзисторов матричного формирователя слов, а истоки МОП-транзисторов других столбцов матричных дешифратора и формировагеля слов подключены к соответствующим шинам связи.

Источники информации, принятые во внимание при экспертизе

1, ЕЭЙ/HE 1972, у. 17, % 6.

2. «CompUter Design decemger

1973.

3. Электронная техника", сер. 3.

Микроэлектроника. вып, 5 (53), с. 2226 (прототип) .

730651

1

/2

Составитель В. Гордонова

Редактор Л, Утехина Техред Ж. Кастелевич Корректор Е. Папи

Заказ 2951/48 Тираж 662 Подписное

ЦНИИПИ Государственного комитета СССР по делаМ изобретений и открытий

113035, Москва, 7К-38, Раушская наб., д. 4/5 филиал ППП Патент, г. Ужгород, ул, Проектна, 4